Analog (radio frequency) and digital (microcontroller) circuits may work well individually, 但是一旦這兩個在同一條線上 印刷電路板 使用相同的電源一起工作, 整個系統可能不穩定. This is mainly because the digital signal oscillates frequently between the ground and the positive power supply (size 3 V), 而且時間非常短, 通常為ns類. 由於振幅大,開關時間短, 這些數位信號

NAL包含大量與開關頻率無關的高頻分量。 在類比部分,從天線調諧回路傳輸到無線設備接收部分的訊號通常小於1mV。

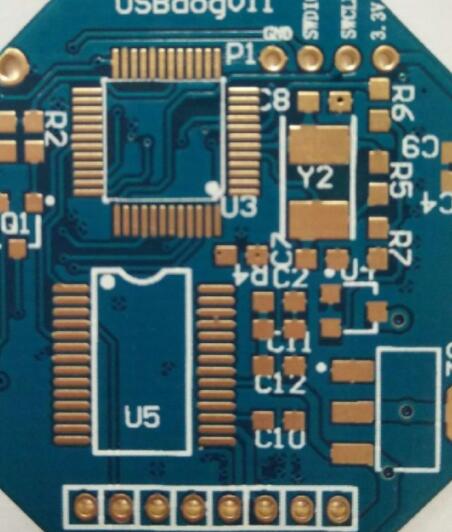

敏感線和雜訊訊號線的隔離不足是一個常見問題。 如上所述,數位信號具有高擺幅,並且包含大量高頻諧波。 如果PCB上的數位信號佈線與敏感的類比信號相鄰,則高頻諧波可能會耦合過去。 射頻器件的敏感節點通常是鎖相環(PLL)的環路濾波電路、外部壓控振盪器(VCO)電感、晶體參攷訊號和天線端子。 應特別小心處理電路的這些部分。

由於輸入/輸出信號具有幾伏的擺幅,數位電路通常可以接受功率雜訊(小於50毫伏)。 類比電路對功率雜訊非常敏感,尤其是對毛刺電壓和其他高頻諧波。 囙此,包含射頻(或其他類比)電路的印刷電路板上的電源線必須比普通數位板上的線路更仔細,並且應避免自動佈線。 還應注意,微控制器(或其他數位電路)將在每個內部時鐘週期內的短時間內突然吸收大部分電流,因為現代微控制器是使用CMOS工藝設計的。

射頻板應始終有一個接地層連接到負極電源,如果處理不當,可能會產生一些奇怪的現象。 這對於數位電路設計者來說可能很難理解,因為大多數數位電路即使沒有接地層也能很好地工作。 在射頻中,即使很短的導線也像電感。 通過粗略計算,每毫米長度的電感約為1 nH,10 mmPCB線路在434 MHz時的電感電抗約為27Ï 。 如果不使用地線,大多數地線將很長,並且無法保證電路的設計特性。

這在包含射頻和其他元件的電路中經常被忽略。 除了射頻部分,板上通常還有其他類比電路。 例如,許多微控制器具有內寘的模數轉換器(ADC),用於量測類比輸入以及電池電壓或其他參數。 如果射頻發射器天線位於PCB附近(或上),則發射的高頻訊號可能到達ADC的類比輸入。 不要忘記,任何電路都可以像天線一樣發送或接收射頻訊號。 如果未正確處理ADC輸入,則射頻訊號可能在ADC輸入的ESD二極體內自激,導致ADC偏差。

與接地層的所有連接必須盡可能短,接地孔應放置在(或非常靠近)元件的襯墊上。 絕不允許兩個接地訊號通過孔共亯一個接地。 由於孔連接的電阻,這可能會導致焊盤之間的串擾。 去耦電容器應盡可能靠近引脚,並應在需要去耦的每個引脚處使用。 高品質陶瓷電容器、介質類型“NPO”和“X7R”在大多數應用中工作良好。 選定電容的理想值應確保其串聯諧振等於訊號頻率。

例如,SMD安裝的100 p F電容器在434 MHz下工作良好,在此條件下,電容電抗約為4Ï ,通孔電抗在相同範圍內。 電容器和孔串聯形成訊號頻率的陷波濾波器,可以有效地解耦。 在868兆赫,33 p F電容器是一個理想的選擇。 除了低值電容器的射頻去耦外,還應在電源線上放置一個高值電容器以去耦低頻,選擇2。 2mF陶瓷或10mF鉭電容器。

星形佈線是類比電路設計中的一種著名科技。 星形接線-電路板上的每個模塊都有自己的電源線,來自公共電源點。 在這種情況下,星形佈線意味著電路的數位和射頻部分應具有單獨的電源線,並且這些電源線應在IC附近單獨解耦。 這是數位的一個分區

射頻部分和部分電源雜訊的有效方法。 如果在同一電路板上放置高雜訊模塊,則可以在電源線和模塊之間串聯電感(磁珠)或小電阻(10Ï ),並且必須使用至少10mF的鉭電容器來斷開這些模塊的電源。 例如RS 232驅動器或開關功率調節器等模塊。

為了减少雜訊模塊和周圍類比部分的干擾,板上每個電路模塊的佈局很重要。 敏感模塊(射頻部件和天線)應始終遠離嘈雜的模塊(微控制器和RS 232驅動器),以避免干擾。 如上所述,射頻訊號在傳輸時可能會引起與其他敏感類比電路模塊(如ADC)的干擾。 大多數問題發生在較低的工作頻段(例如27 MHz)以及高功率輸出水准。 使用連接到地面的射頻去耦電容(100p F)來去耦敏感點是一種良好的設計實踐。

如果使用電纜將射頻板連接到外部數位電路,請使用雙絞線電纜。 每個訊號電纜必須與GND電纜(DIN/GND、DOUT/GND、CS/GND、PWR-UP/GND)雙絞線。 使用雙絞線的GND電纜將RF電路板連接到數位應用電路板。 電纜長度應盡可能短。 為射頻板供電的線路也必須連接到GND雙絞線(VDD/GND)。