設計數模混合PCB對理解以下基本概念非常重要。 掌握數模混合PCB設計的基本概念,有助於理解稍後製定的嚴格佈局和佈線設計規則,使終端產品在設計數模混合設計時不會輕易打折扣。 執行重要的約束規則。 它有助於靈活有效地處理數模混合設計中可能遇到的串擾問題。

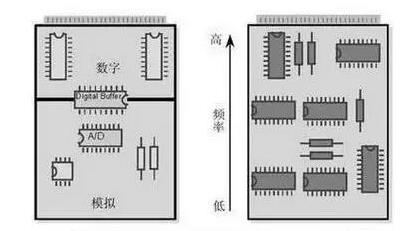

1.類比信號與數位信號在抗干擾能力上的重要區別數位信號電平抗干擾能力强,類比信號抗干擾能力差。 例如,3V電平的數位信號即使在不影響邏輯狀態的情况下接收0.3V訊號,也可以容忍0.3V的串擾訊號。 然而,在類比信號領域,有些訊號非常微弱。 例如,GSM手機的接收靈敏度可以達到-110dBm的名額,這僅相當於0.7uV的正弦波的有效值。即使在LNA的前端接收到UV量級的帶內干擾雜訊,也足以大大降低基站的接收靈敏度。 這種輕微的干擾可能來自數位控制訊號線或電源地線上的小雜訊。 從系統的角度來看,數位信號通常只在板上或框架中傳輸。 例如,記憶體匯流排訊號、電源控制訊號等,只要從發送端到接收端接收到的干擾不足以影響邏輯狀態的判斷。 類比信號需要經過調製、頻率轉換、放大、傳輸、空間傳播、接收和解調等一系列過程才能恢復。 在這個過程中,雜訊不斷下降到訊號中。 從系統的角度來看,為了正確解調,有必要確保最終的信噪比符合要求。 干擾來自於空間傳播的衰减和雜訊。 為了獲得更好的通信效能,必須盡可能减少板上互連引入的串擾。 囙此,可以認為類比信號對串擾的要求是數位信號的幾十倍,甚至可能達到數萬倍。 高精度ADC和DAC電路通常,線性ADC和DAC的信噪比與轉換位數之間的關係為:SNR=10Log(F2/N2)=10Log[A2/2/(A2/3*2n)]=6.02n+1.76dB對於14比特線性ADC和DACs,如果啟用比特數據(LSB),理論信噪比可計算為86dBc。 與數位電路約20dBc的串擾要求相比,高精度14比特線性ADC和DAC對雜訊的要求至少是數位信號的1000倍。 當然,如果有效比特數僅為11比特,則可以適當地降低串擾要求,但它仍然遠高於對數位信號的要求。 以上兩種情况表明,在數模混合單板中,類比電路極易受到干擾,干擾會影響信噪比等名額。 囙此,在數模混合單板PCB設計過程中,對佈局和佈線提出了非常高的要求3。 數位信號是對類比信號的强幹擾源與類比信號相比,數位信號的電平非常高,並且數位信號包含豐富的諧波頻率,囙此數位信號本身是類比信號的强大干擾源。 特別是大電流時鐘訊號和開關電源是數模混合設計中需要注意的强幹擾源。 數模混合互連設計的基本目的通過這種管道我們可以理解數模設計問題。 對於數位電路,我們遵循數位電路的設計規則。 在數位電路領域,只要不影響系統功能和外部EMC名額的實現,就可以允許大干擾。 我們在這裡談論的“更大”是相對於類比電路而言的。 對於數位電路來說,我們沒有必要也不可能像類比電路一樣控制串擾的存在。 對於類比電路,我們必須遵循類比電路的設計規則,類比電路區域的允許干擾比數位電路區域的小得多。 數模混合互聯設計的目的是通過合理的佈局、佈線、遮罩、濾波和電源劃分,確保數位信號的干擾只存在於數位信號區域。 我們需要關注的內容包括干擾源、敏感電路和干擾路徑。 以下將從這三個方面介紹所採用的佈局和佈線原則。 成功的數模混合單板設計必須仔細注意整個過程中的每一個步驟和每一個細節,才能實現。 這意味著在設計之初必須進行徹底而仔細的規劃,並且必須仔細規劃每一個設計步驟。 對工作進展情況進行全面、持續的評估。 必須仔細檢查和驗證佈局和佈線,以確保100%符合佈局和佈線規則。 否則,訊號線的不正確佈線將完全破壞原本非常好的印刷電路板。 規則已經失效。 只有通過對規則的深入理解,才能確保我們能够正確使用規則,完成數模混合PCB的設計。