晶圓級封裝的最初出現是由手機低速I/O和低速電晶體組件的製造推動的,如無源片上感測器和功率傳輸IC。 現時,WLP正處於發展階段,受到藍牙、GPS和聲卡等應用的推動,需求逐漸新增。 隨著行業發展到3G手機的生產階段,手機的各種新應用有望成為WLP的另一個增長驅動因素,包括電視調諧器、調頻發射機和堆棧記憶體。 隨著儲存設備製造商逐步實施WLP,它將導致整個行業的標準化轉型。

現時,該科技廣泛應用於各種領域,如閃存、EEPROM、高速DRAM、SRAM、LCD驅動器、RF設備、邏輯設備、電源/電池管理設備和類比設備(調節器、溫度感測器、控制器、運算放大器、功率放大器)。 晶圓級封裝主要採用兩種基本科技:薄膜再分配和凸塊形成。 前者用於將沿晶片週邊分佈的接合區域轉換為在晶片表面上以平面陣列形式分佈的凸塊接合區域。 後者用於在凸塊結合區域上創建凸塊,形成凸塊陣列。

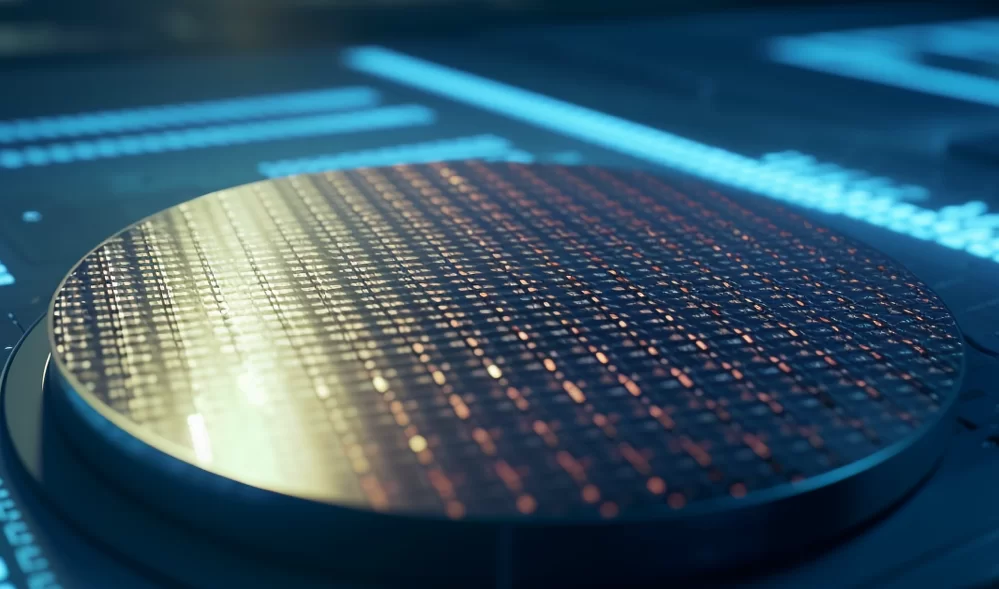

晶圓級封裝

現時,晶圓級封裝有三種路徑:WLCSP、FOWLP和PLP:

WLCSP(晶圓級晶片尺寸封裝),也稱為WLP中的扇形封裝,是用於最終晶片劃片的傳統封裝方法。 它適用於引脚數量較少的集成電路。 隨著IC輸出信號數量的新增,焊球尺寸變得更加嚴格。 PCB不能滿足調整封裝IC的尺寸和訊號輸出引脚的位置的要求。

FOWLP從晶片劃片開始,然後將它們重新分配到新的人造成型晶圓上。 優點包括减少封裝厚度、新增扇出(更多I/O介面)、更好的電力效能和更好的耐熱性。 FIWLP和FOWLP有不同的應用,但它們都是未來的主要包裝方法。 FIWLP最廣泛地用於類比和混合訊號晶片,其次是無線互連,CMOS圖像感測器也使用FIWLP科技封裝。 FOWLP將主要用於移動設備中的處理器晶片。

PLP(面板級封裝)與FOWLP類似,它將晶片重新分配到更大的矩形面板上,而不是圓形晶片上。 更大的面積意味著更多的成本節約和更高的包裝效率。 此外,將晶片切成正方形會導致浪費的晶圓封裝,矩形面板可以有效解決這一問題。 然而,這也對光刻和對準提出了更高的要求。 其基本思想是在直接封裝矽片的同時完成晶片製造,將多個晶片單元封裝在一個整體封裝結構中。 這避免了在傳統封裝中單獨封裝每個晶片的步驟,從而提高了生產率並降低了成本。

晶圓級封裝的工藝通常包括以下步驟:

晶圓製備:清洗和製備矽片,以確保封裝過程的可靠性和一致性。

封裝結構形成:在矽片上塗上一層封裝資料,通常是聚合物,以形成封裝結構的基礎。

電路連接:在矽片上創建金屬線(引線接合)或其他電路連接結構,將晶片的電路連接到封裝結構。

測試和質量驗證:進行電力性能測試、封裝完整性測試等,以確保封裝晶片符合質量要求。

晶片分離:將封裝的晶片與矽片分離,以獲得單獨的封裝晶片。

WLP基於BGA科技,是CSP的改進和增强形式,充分體現了BGA和CSP的科技優勢。 它有許多獨特的優點:

高封裝加工效率:採用晶圓形式的批量生產工藝製造。

它繼承了倒裝晶片封裝的優點,即輕、薄、短、小。

生產設施成本低:可以充分利用晶片製造設備,避免需要投資單獨的封裝生產線。

統一的晶片和封裝設計考慮:提高了設計效率,降低了設計成本。

縮短了生產週期:它大大縮短了從晶片製造、封裝到產品交付的整個過程,從而降低了成本。

成本效益:WLP的成本與每片晶圓上的晶片數量密切相關。 晶片上的晶片越多,其成本就越低。 這種包裝是最小、成本最低的包裝方法。

WLP的優點在於它適用於較小集成電路的晶片級封裝(CSP)科技。 通過在晶圓級採用並行封裝和電子測試技術,WLP在提高產量的同時顯著减少了晶片面積。 此外,通過在晶圓級並行傳導晶片連接,大大降低了每次I/O的成本。 此外,簡化的模具級測試程式進一步降低了成本。

利用晶圓級封裝能够在晶圓級實現晶片封裝和測試。