低壓配電系統訊號的設計 電路板 不僅僅是一個差分訊號, 同時也是一種高速數位信號. 因此, 無論LVDS傳輸介質是否使用 PCB板 電線或電纜, 必須採取措施防止訊號在媒體終端上反射, 應减少電磁干擾,以確保信號完整性. 只要我們在佈線時考慮這些元素, 設計高速差分電路板並不困難. 以下簡要介紹了LVDS訊號的設計要點 PCB板:21多層板佈局具有LVDS訊號的電路板通常佈置為多層板. 因為LVDS訊號是高速訊號, 相鄰層應為接地層,以遮罩LVDS訊號,防止干擾. 對於低密度的電路板, 如果物理空間條件允許, 將LVDS訊號和其他訊號放置在不同的層上. 例如, 在四層板中, 層通常可以佈置如下:LVDS訊號層, 地面層, 功率層, 和其他訊號層. 2.2 LVDS訊號阻抗計算和控制. LVDS訊號的電壓擺幅僅為3.50mV, 適用於電流驅動的差分訊號操作. 為了確保訊號在傳輸線中傳播時不受反射訊號的影響, LVDS訊號需要控制傳輸線阻抗, 微分阻抗通常為100++/- 10Ω. 阻抗控制的質量直接影響信號完整性和延遲.

1. 如何控制its PCB板 阻抗?

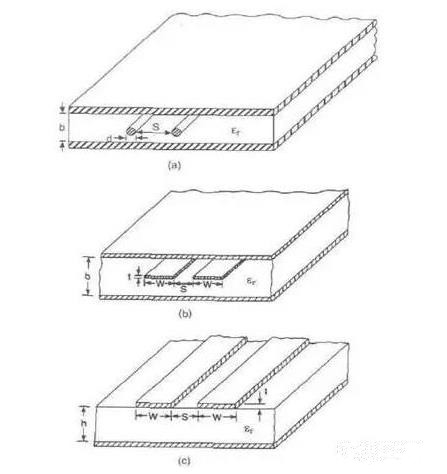

1.1確定接線管道, 參數和阻抗計算. LVDS分為外層微帶線差分模式和內層帶狀線差分模式. 通過合理設定參數並使用相關軟體,可以計算阻抗. 通過計算, 阻抗值與絕緣層的厚度成正比, 與介電常數成反比, 金屬絲的厚度和寬度.

1.2遵循平行等距線和緊密耦合的原則. 確定線寬和間距後, 佈線時嚴格遵循計算的線寬和間距, 兩行之間的間距必須始終保持恒定, 那就是, they must be parallel (you can place the picture). 同時, 在計算線寬和間距時,遵循緊耦合原則, 那就是, 差分對的行距小於或等於線寬. 當兩條差分訊號線非常接近時, 電流傳輸方向相反, 磁場相互抵消, 電場相互耦合, 電磁輻射要小得多. 而且, 兩條導線必須在同一層上,以避免分層佈線. 因為在實際加工中 PCB板, 疊層之間的層壓程度遠低於同一層的蝕刻精度, 層壓過程中的介質損耗不能保證差分線之間的距離等於層間介質的厚度, 這將導致層間差分對的差分阻抗變化.

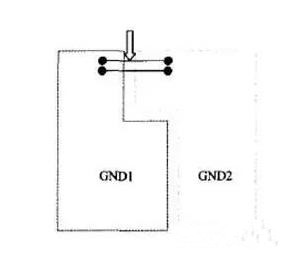

1.3.短而直. 為了確保訊號質量, LVDS差分對軌跡應盡可能短而直, 减少佈線中過孔的數量, 避免差分對佈線過長和匝數過多. 嘗試在拐角處使用45°或圓弧. 避免90°轉彎. 在不同差分線對之間選擇LVDS對路由方法沒有限制. 可以使用微帶線和帶狀線, 但必須注意的是,有一個良好的基準面. 不同差動線之間的間距不應太小, 並且應至少為差分線間距的3-5倍. 如有必要, 在不同差分線對之間添加接地孔隔離,以防止相互串擾. 盡可能使LVDS訊號遠離其他訊號. LVDS差分訊號不能跨平面分割. 儘管兩個差分訊號是彼此的返回路徑, 交叉分割不會切斷訊號的返回, but the transmission line across the segmentation will cause discontinuity in impedance due to the lack of a reference plane (as shown in the figure, where GND1 and GND2 are adjacent to LVDS Ground plane). 接收端的匹配電阻和接收引脚之間的距離應盡可能接近. 同時, 必須控制匹配電阻的精度. 對於點到點拓撲, 軌跡的阻抗通常控制在100Î), 但匹配電阻可以根據實際情況進行調整. 抵抗程度為1%-2%. 因為根據經驗, 10%的阻抗失配將產生5%的反射.

2. Simulation analysis of serial LVDS signal

The above analyzes the matters that must be paid attention to when 設計ing LVDS signals. 儘管在PCB設計過程中通常遵循上述規則, 為了提高設計的正確性和準確性, PCB的完整訊號類比必須通過類比進行. 獲取訊號的串擾, 延遲, 反射和眼圖波形, 從而達到正確設計的目的. 信號完整性問題的模擬過程是首先建立元件的模擬模型, 然後進行預類比,以確定佈線過程的參數和約束. 根據約束條件設計物理實現階段, 並進行後模擬以驗證設計是否滿足設計要求. 整個過程中模型的性質直接影響類比結果, 在預模擬和後模擬階段使用的模擬分析方法對模擬結果也至關重要, 本設計採用了更高階的spice模型. 下麵結合實際項目來說明本設計中模擬的實現過程.

2.1 PCB板 stack setting

From the above analysis, 已知的是 PCB板 與訊號的耦合和阻抗計算密切相關. 因此, 堆垛設計必須在 PCB板 design, 然後計算訊號的阻抗.

2.2 Set DC voltage value

This step is mainly to specify the DC voltage value for certain specific networks (usually power ground, 等.), 確定應用於網絡的直流電壓, 執行EMI模擬需要確定一個或多個電壓源引脚. 這些電壓值包括模型在類比過程中使用的參攷電壓資訊.

2.3 Device settings

During allegro simulation, allegro將設備分為3類:IC, connectors and discrete devices (resistance capacitors, 等.), allegro將根據設備類型為設備的管脚分配類比内容, 離散設備和連接器引脚内容為UPSPEC, IC的引脚内容可以在, 退出, BI公司, 等.

2.4 Model allocation

The main models used in the board-level high-speed PCB板 模擬過程包括設備模型和傳輸線模型. 設備型號通常由設備製造商提供. 在高速串列訊號中, 採用精度較高的SPICE模型進行模擬分析. 通過模擬軟件建模,形成輸電線路模型. 訊號傳輸時, 輸電線路將使信號完整性問題突出, 囙此,模擬軟件對輸電線路建模的能力直接影響到模擬結果.

2.5 SI inspection

The SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. 通常地, 我們需要注意的是建立高速網絡. 本設計主要針對LVDS串列訊號.

2.6 Extract network topology

Extract the topological structure of the signal of interest from the PCB板, 一般包括驅動端和接收端, 以及傳輸線和相關匹配電阻器和電容器. 從拓撲結構可以看出,網絡通過這些路徑, 這將導致訊號傳輸影響. This article only takes the network topology diagram of one of the signals as an example: as shown in Figure 4:

2.7 View waveform

After the above related steps are set up, 可以進行類比. Allegro可以進行訊號反射類比和串擾類比, 微分線也需要進行眼圖分析. 當然, 模擬也分為預模擬和後模擬. 當使用allegro設計 PCB板, 有必要根據模擬結果實时修改設計,以滿足要求. 因為類比過程複雜,步驟繁瑣, 我不會一一描述. 在差分對的接線中需要注意兩點. 一是兩條線的長度應該盡可能長, 長度相等是為了確保兩個差分訊號始終保持相反. 减少共模分量的極性. The other is that the distance between the two lines (this distance is determined by the differential impedance) must always be kept constant, 那就是, 它必須保持平行. 有兩種平行的管道, 一是兩條電線並排在同一條線上, and the other is that the two wires run on two adjacent layers above and below (over-under). 通常地, 前者有更多的並行實現. 等距離主要是為了確保兩者之間的差分阻抗相同,並减少反射. 差分對的接線方法應緊密並適當並聯. 所謂的適當接近是因為該距離將影響差分阻抗的值, 這是設計差分對的一個重要參數. 並行性的需要也是為了保持差分阻抗的一致性. 如果兩條線突然遠近, 差動阻抗將不一致, 這將影響信號完整性和定時延遲. 從類比的S參數圖, 可以分析差分對的差分阻抗和信號完整性. 下麵給出了本設計中的關鍵訊號類比波形,以供解釋. 從類比圖例圖5可以看出,S11在頻域中的退化指數為0-3.0GHz為:低於-16.770db, and S22 (pink curve) is not worse than -17db. 這表明差分對的差分阻抗接近設計名額, 信號完整性得到保證.

3. Conclusion

Through the above simulation analysis, 可以知道,在設計階段可以滿足對高速LVDS訊號的各種要求 PCB板, 和實際情況 PCB板 生產也證明了設計的正確性. 該產品運行穩定,完全滿足PCI-Express對高速資料傳輸和高可靠性的要求. 從本文的分析來看, 可以看出,在高速串列訊號的設計中, 不僅考慮了電路設計, 電路板圖設計和模擬分析也同樣重要, 隨著訊號的頻率越來越大, 訊號的延遲和串擾受到影響. 信號完整性和信號完整性等因素變得越來越複雜. 同時, 控制這些因素的影響變得越來越困難. 工程師必須徹底分析佈線設計, 使用的模型, 有效的類比和科學的分析方法, in order to provide the correct guidance for the complex high-speed PCB板 design and reduce the correction cycle to ensure The design is successful.