無論是設備佈局還是PCB板上的佈線, 有具體要求. 例如, 應盡可能避免輸入和輸出接線,以避免干擾. 兩條訊號線的平行佈線必須用地線隔開, 相鄰兩層的佈線應盡可能相互垂直. 寄生耦合可能並行發生. 電源線和地線應盡可能分為兩層,以相互垂直. 線上寬方面, 寬地線可以用作 數位電路PCB, which constitutes a ground network (analog circuits cannot be used in this way), 並且使用了大面積的銅.

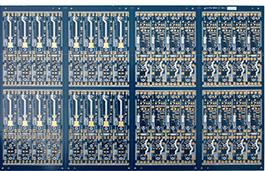

作為21世紀的歷史產物, 單片機成功地將電腦集成到 小型印刷電路板, 實現萬物互聯, 為我們的生活體驗提供了很多便利. 下一個, 老陳將向你展示單片機主控板需要使用的巧妙設計.

1、部件佈置

在部件佈局方面,相互關聯的部件應盡可能靠近。 例如,時鐘發生器、晶體振盪器和CPU的時鐘輸入都容易產生雜訊,囙此它們應該放得更近。 對於容易產生雜訊的器件、小電流電路、大電流電路開關電路等,應儘量遠離單片機的邏輯控制電路和存儲電路(ROM、RAM)。 如果可能,這些電路可以製成電路。 這有利於抗干擾,提高電路工作的可靠性。

2、去耦電容器

嘗試在關鍵組件(如ROM、RAM和其他晶片)旁邊安裝去耦電容器。 事實上,PCB板軌跡、引脚連接和佈線等可能包含較大的電感效應。 大電感可能會在Vcc軌跡上造成嚴重的開關雜訊尖峰。 防止Vcc軌跡上開關雜訊尖峰的唯一方法是在Vcc和電源接地之間放置一個0.1uF電子去耦電容器。 如果在PCB上使用表面貼裝元件,則可以直接對元件使用片式電容器,並將其固定在Vcc引脚上。 最好使用陶瓷電容器,因為這種電容器具有低靜電損耗(ESL)和高頻阻抗,並且這種電容器的介電穩定性的溫度和時間也非常好。 儘量不要使用鉭電容器,因為它們在高頻下的阻抗更高。

放置去耦電容器時,請注意以下幾點:

(1)在PCB板的電源輸入端連接一個100uF電解電容器。 如果體積允許,電容越大越好。

(2)原則上,需要在每個集成電路晶片旁邊放置一個0.01uF陶瓷電容器。 如果電路板的間隙太小,無法安裝,可以每10個晶片放置1-10個鉭電容器。

(3)對於抗干擾能力弱、關閉時電流變化大的部件,以及RAM和ROM等存儲部件,應在電源線(Vcc)和地線之間連接去耦電容器。

(4)電容器的引線不宜過長,尤其是高頻旁路電容器不能有引線。

3、地線設計

在單片機控制系統中,有多種類型的接地線,如系統接地、遮罩接地、邏輯接地、類比接地等。接地線的佈置是否正確將决定電路板的抗干擾能力。 設計地線和接地點時,應考慮以下問題:

(1)邏輯接地和類比接地應分開接線,不能一起使用。 將其各自的接地線連接到相應的電源接地線。 設計時,類比地線應盡可能厚,端子的接地面積應盡可能大。 一般來說,最好通過光耦合器將輸入和輸出類比信號與微控制器電路隔離。

(2)在設計邏輯電路的印刷電路板時,地線應形成閉環形式,以提高電路的抗干擾能力。

(3)接地線應盡可能厚。 如果接地線很薄,接地線的電阻將很大,導致接地電位隨電流變化而變化,導致信號電平不穩定,從而降低電路的抗干擾能力。 如果佈線空間允許,確保主地線的寬度至少為2~3mm,元件引脚上的地線應為1.5mm左右。

(4)注意接地點的選擇。 當電路板上的訊號頻率低於1MHz時,由於接線和部件之間的電磁感應影響很小,並且接地電路形成的迴圈電流對干擾的影響較大,囙此有必要使用接地點,使其不會形成回路。 當電路板上的訊號頻率高於10MHz時,由於佈線的明顯電感效應,接地阻抗變得非常大。 此時,接地電路形成的迴圈電流不再是主要問題。 囙此,應採用多點接地,以盡可能降低接地阻抗。

4、其他

(1)除了電源線的佈局外,跡線的寬度應根據電流的大小盡可能厚。 接線時,電源線和地線的佈線方向應與數據線的佈線方向一致。 在佈線工作結束時,使用地線覆蓋電路板底部沒有痕迹的地方,這些方法將有助於增强電路的抗干擾能力。

(2)數據線的寬度應盡可能寬,以减少阻抗。 數據線的寬度至少不小於0.3mm(12mil),如果為0.46~0.5mm(18mil~20mil),則更為理想。

(3) Since a via on the circuit board will bring about 10pF capacitance effect, 這將對 高頻電路, 所以當接線時, 應盡可能减少過孔的數量. 此外, 過孔過多也會降低電路板的機械強度.