作為一個 PCB設計 工程師, 這是非常必要的, 甚至是必要的, 掌握一些高速知識. 就訊號而言, 高速訊號通常存在於各種並行電路中公共汽車鎄和串列公共汽車鎄. 只有當你知道公共汽車 是, 你知道它跑得有多快嗎, 然後你就可以開始了 PCB 裝電線.

公共汽車

匯流排是兩個或多個設備之間通信的共亯物理通道。 它是訊號線的集合和多個組件之間的公共連接,用於在每個組件之間傳輸資訊。 根據工作模式的不同,匯流排可以分為兩種類型:一種是並行匯流排,另一種是串列匯流排。

並聯匯流排

可以同時傳輸多個位的數據,這就像一條寬敞的道路,允許多輛車並排行駛,它還具有雙向和單向點。

串列匯流排

同一時間只能傳輸一條數據,這就像一條只允許一輛車行走的狹窄道路。 數據必須一個接一個地傳輸,這看起來像一個長數據字串,囙此它被稱為“串列”。

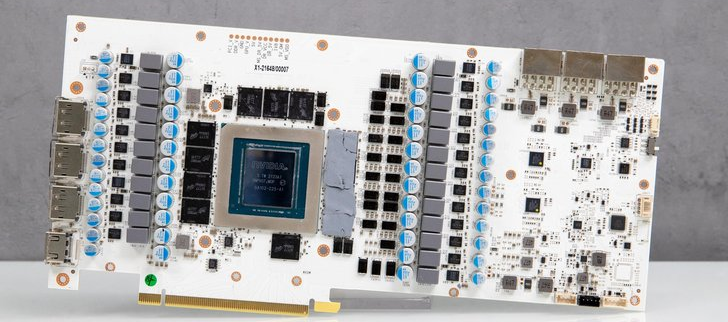

並行傳輸的最佳示例是記憶體晶片DDR。 它有一組數據線D0-D7,加上DQS和DQM。 這組線路一起傳輸。 無論哪個比特出錯,數據都無法正確傳輸。 僅重新傳輸。 囙此,數據電纜的每根電纜必須等長,並且必須纏繞數次。

串列數據不同。 數據逐個傳輸,比特之間沒有連接。 該比特沒有錯誤,無法傳輸下一位。 並行數據是一組數據,其中一位錯誤,而整個數据集將無法工作。

PCB佈線 requirements

並聯母線接線要求:

(1)建議母線最好內部接線,母線與其他接線之間的距離應盡可能新增。

(2)除特殊要求外,單線設計阻抗保證為50歐姆,差分設計阻抗保證為100歐姆。

(3)建議同一組匯流排保持相同的佈線長度,並與時鐘線遵循一定的時序關係,並參攷時序分析的强大結果控制佈線長度。

(4)建議盡可能靠近這組匯流排的輸入/輸出電源或GND基準面,以確保基準面的完整性。

(5)上升時間小於1ns的匯流排需要一個完整的基準面,不得穿過隔板。

(6)建議下層地址匯流排參攷時鐘佈線要求。

(7)蛇形繞組線的間距不得小於線寬的3倍。

高速PCB串列匯流排佈線要求

對於頻率高於100Mbps的串列匯流排,除了遵循並行匯流排的一般串擾控制和佈線規則外,在佈線設計中還需要考慮一些額外的要求:

(1) 這個 高速PCB 電視連續劇公共汽車 needs to consider 這個 loss of wiring and determine the line width and line length.

(2)建議在正常情况下線寬不小於5mil,接線應盡可能短。

(3)除扇出通孔外,高速串列匯流排不應穿孔和更換。

(4)當串列匯流排中插入引脚的速度高於3.125Gbps時,應優化防焊盤,以减少不連續阻抗引起的非輻射影響。

(5)建議在更換高速串列匯流排佈線層時,選擇通孔存根最小的佈線層。 對於到連接器的訊號,當佈線空間有限時,具有短通孔存根的佈線層優先分配給發送端。

(6)建議當速率為3.125Gbps或更高時,應在訊號通孔旁邊鑽一個接地孔,並且交流耦合電容器也應經過特殊處理,以用於防焊盤。

(7)如果通過反鑽孔處理高速訊號通孔,則有必要考慮縮小流量瓶頸後功率接地層電流容量的降低和濾波器回路電感的新增的影響。

(8)高速訊號避免了平面層的分界線,並且訊號線邊緣和分界線邊緣之間的水准距離保證為3W。

(9)兩個方向的高速訊號不應交叉和路由。