Hệ thống in PCB phân tích cấp tạo nhiễu Để tạo một hệ thống DSP ổn định và đáng tin cậy, can thiệp phải bị loại khỏi mọi khía cạnh, ngay cả khi nó không thể bị tiêu diệt hoàn toàn, nó phải được thu nhỏ càng nhiều càng tốt. Cho hệ thống DSP, Sự can thiệp chính đến từ các khía cạnh sau:. nhiễu kênh nhập và xuất. Liên quan tới sự can thiệp vào hệ thống thông qua kênh trước và kênh hậu chiều., như kết nối dữ liệu về hệ thống DSS. Sự nhiễu được trộn vào tín hiệu qua cảm biến, làm tăng lỗi nhận dữ liệu. Trong kết nối xuất, nhiễu có thể tăng lỗi dữ liệu xuất, hoặc thậm chí phạm sai lầm hoàn toàn, làm hệ thống bị hỏng. Có thể dùng trực tiếp để giảm sự can thiệp của kênh nhập và xuất, và sự can thiệp của bộ cảm biến và hệ thống chính DSS có thể được dùng để cô lập điện tử nhiễu. Name. Sự can thiệp của hệ thống cung cấp điện. Nguyên nhân gây nhiễu chính cho toàn bộ hệ thống DSS. Nguồn điện thêm nhiễu vào nguồn điện cung cấp điện cung cấp năng lượng cho hệ thống. Dây nguồn điện phải được tách ra khi thiết kế mạch con chip cung cấp năng lượng.. Comment. Sóng phóng đại. Khớp nối qua bức xạ thường được gọi là trò chuyện chéo.. Crosstalk xảy ra trong trường điện từ khi dòng điện chảy qua các dây., và trường điện từ trường tạo ra dòng chảy tạm thời ở những đường dây liền kề, gây méo các tín hiệu xung quanh hoặc thậm chí là lỗi. Sức mạnh của trò chuyện này phụ thuộc vào kích thước đo và khoảng cách cách biệt của thiết bị và dây nhợ.. Trong mạng lưới DSS, Khoảng cách của đường tín hiệu lớn hơn và gần với đường đất hơn., Càng có hiệu quả để giảm liên lạc. 2 Thiết kế PCB cho nguyên nhân gây nhiễu. Những diễn viên sau đây cho thấy làm thế nào để giảm các ảnh hưởng Sản xuất PCB quá trình của hệ thống DSS.

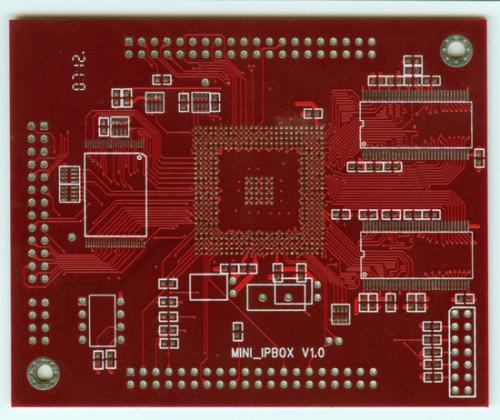

Để nâng cao chất lượng tín hiệu, giảm độ khó của dây điện, và tăng EMC của hệ thống, trong hệ thống điện tử cao tốc của hệ thống thiết kế bằng plastic của một tấm ván đa lớp của nó. PCB sửa, In cạnh giường của tấm ván đa lớp thông thường được chấp nhận. Thiết kế xếp có thể cung cấp đường trở về ngắn nhất, giảm vùng nối, và chặn nhiễu chế độ khác nhau. Trong thiết kế xếp, phân phối sức mạnh chuyên nghiệp và lớp mặt đất, and the tight coupling of the ground layer and the power layer is good for suppressing common mode interference (using adjacent planes to reduce the AC impedance of the power plane). Lấy tấm ván bốn lớp hiển thị trong hình A1 làm ví dụ để minh họa thiết kế bằng plastic. Có rất nhiều lợi thế khi chấp nhận việc này Cấu trúc PCB bốn lớp. Có một lớp sức mạnh bên dưới lớp trên, và các chốt điện của các thành phần có thể kết nối trực tiếp với nguồn năng lượng mà không đi qua mặt đất.. The key signal is selected on the bottom layer (bottorn layer), để hệ thống dây tín hiệu quan trọng có thể lớn hơn, và các thiết bị được đặt vào cùng một lớp càng nhiều càng tốt.. Nếu không cần thiết, không làm bảng thành phần hai lớp, sẽ làm tăng thời gian lắp ráp và phức tạp hóa lắp ráp.. Ví dụ như lớp trên, Chỉ khi các thành phần trên quá dày, chiều cao có giới hạn và thiết bị sản xuất nhiệt thấp, such as decoupling capacitors (patch) are placed on the bottom layer. Cho hệ thống DSS, có thể có một số lượng lớn đường dây được định tuyến., và kế hoạch được chấp nhận, và đường dây có thể được định tuyến trong lớp trong.. Nếu có nhiều chỗ dây có giá trị bị lãng phí theo cách thông qua các lỗ thông thường, mù/Hy vọng bị chôn có thể dùng để tăng vùng dây dẫn..

Thiết kế bố trí PCB Để đạt được hiệu suất tốt nhất của hệ thống DSS, Cấu trúc các thành phần rất quan trọng. Nơi Mạng DSP, Chớp, Comment, và các thiết bị CPLD trước, Xem cẩn thận khoảng cách dây., rồi đặt các bộ phận I.C. khác theo nguyên tắc tự lập chức năng, và cuối cùng hãy cân nhắc việc sắp đặt tôi/O các cảng. Kết hợp bố trí bên trên và xem xét PCB Cỡ: nếu kích cỡ quá lớn, Các đường in sẽ quá lâu., Trở ngại sẽ tăng lên, độ chịu nhiễu sẽ bị giảm, và giá ban quản trị sẽ tăng lên. nếu như PCB quá nhỏ, Phản ứng nhiệt sẽ không tốt., và không gian sẽ bị giới hạn, Đường viền phức tạp rất khó phá. Do đó, thiết bị sẽ được chọn theo nhu cầu thực sự., kết hợp với khoảng dây., và tính toán đại khái kích thước của PCB. Khi phát hành hệ thống DSS, chú ý đặc biệt đến vị trí của những thiết bị sau đây.

(1) High-speed signal layout In the entire DSP system, Các đường dây tín hiệu điện tử với tốc độ cao chính là giữa DSP và Chớp và SSAM, nên khoảng cách giữa các thiết bị phải càng gần càng tốt., và kết nối của họ ngắn nhất có thể, và chúng nên được kết nối trực tiếp. Do đó, để giảm ảnh hưởng của đường truyền lên chất lượng tín hiệu, Dấu vết tín hiệu tốc độ cao phải ngắn nhất có thể.. Also consider that many DSP chips with speeds up to several hundred MHz require a snake-shaped winding (delay tune). Điều này sẽ được nhấn mạnh trong hệ thống dây này.

(2) The layout of digital-analog devices is mostly not a single functional circuit in a DSP system. Một số lượng lớn các thiết bị điện tử và các thiết bị tổng hợp điện tử., Vậy là kỹ thuật số/bố trí tương tự nên tách ra. Thiết bị tín hiệu tương tự tập trung hết mức có thể., để so sánh mặt đất có thể vẽ một khu vực độc lập thuộc về tín hiệu tương tự ở giữa to àn bộ mặt đất số., để tránh nhiễu tín hiệu điện tử với tín hiệu tương tự. Đối với một số thiết bị điện tử, như là D/Máy chuyển, theo truyền thống thì chúng được coi là dụng cụ, đặt dưới đất tương tự, và cung cấp một vòng điện tử để cho phép tiếng ồn điện tử được nạp về nguồn tín hiệu để giảm tiếng ồn số..

(3) The layout of the clock As far as possible from the clock, tín hiệu con chip và xe buýt, The I/Đường dây và kết nối phải được giữ càng xa càng tốt.. Việc đột nhập đồng hồ của hệ thống DSP rất dễ bị nhiễu., và việc xử lý rất quan trọng. Luôn đảm bảo rằng máy phát đồng hồ gần con chip DSS nhất có thể., và làm cho dòng đồng hồ ngắn nhất có thể.. Cái vỏ ngoài của đồng hồ tinh dịch được thiết lập tốt nhất.

(4) Decoupling layout In order to reduce the instantaneous overshoot of the voltage on the power supply of the integrated circuit chip, một tụ điện tách ra được thêm vào con chip mạch tổng hợp., có thể loại bỏ tác động của cái gai lên nguồn cung điện và giảm sự phản chiếu của dây điện trên PCB . Thêm một tụ điện tách ra có thể vượt qua nhiễu tần số cao của thiết bị mạch hoà hợp., và cũng có thể được dùng làm tụ điện dự trữ năng lượng cung cấp và hấp thụ năng lượng khởi động của cửa ra vào và đóng cửa hệ thống..

Vì Kiểm chứng PCB in the DSP system, đặt các tụ điện tách ra cho mỗi mạch tổng hợp, như DSP., Comment, Flash, Comment., và thêm chúng giữa mỗi nguồn điện và mặt đất của con chip, and pay special attention to the decoupling capacitors as close as possible to the power supply terminal (source) and IC component pins (pin). Ensure the purity of the current from the power supply terminal (sotlrce terminal) and the IC, và ngắn âm thanh càng nhiều càng tốt. Như đã hiển thị trong hình 2, khi sử dụng tụ điện, dùng cầu lớn hoặc nhiều cầu kì, và kết nối giữa cầu và tụ điện phải ngắn và dày nhất có thể.. Khi khoảng cách giữa hai kinh là quá dài, nó không tốt vì con đường quá lớn; Tốt nhất là hai phương án của tụ điện tách ra càng gần càng tốt., để tiếng ồn có thể chạm đến mặt đất trong đường ngắn nhất.