Là đại diện của vật liệu PCB tổn thất thấp, Teflon Multilayer Board đã có hơn mười năm kinh nghiệm ứng dụng thực tế trong lĩnh vực truyền thông dân sự và quân sự, nhưng bị hạn chế bởi kịch bản ứng dụng và hiệu suất xử lý của nó, Teflon PCB truyền thống chủ yếu là các ứng dụng sản phẩm thụ động veneer, bảng kép, chẳng hạn như mạng lưới cấp nguồn trên trời của trạm cơ sở. Nhưng đối với các ứng dụng sóng milimet trong tương lai, cấu trúc bảng điều khiển đơn và đôi thông thường rất khó đáp ứng nhu cầu thiết kế, thì có thể dự đoán rằng sẽ có ngày càng nhiều nhu cầu về tấm đa lớp PTFE (thay vì tấm lai PTFE+FR-4). Trong khi đó, sự xuất hiện của cấu trúc tấm nhiều lớp cho phép số lượng PTH có chức năng truyền tín hiệu tăng lên, điều này chắc chắn đề cập đến vấn đề tách nhiều lớp PTFE.

1. Định nghĩa và tiêu chuẩn phán quyết về khuyết tật tách giữa các lớp

Các khiếm khuyết kết nối bên trong là sự hiện diện của các tạp chất không dẫn điện giữa lá đồng bên trong của các bức tường bên trong của lỗ ngón tay và đồng mạ điện, chủ yếu là bụi bẩn khoan được tạo ra bởi các lỗ khoan trong quá trình xử lý PCB. Cần lưu ý rằng khiếm khuyết này phổ biến trong tất cả các lớp PCB, không chỉ PTFE PCB Multilayer.

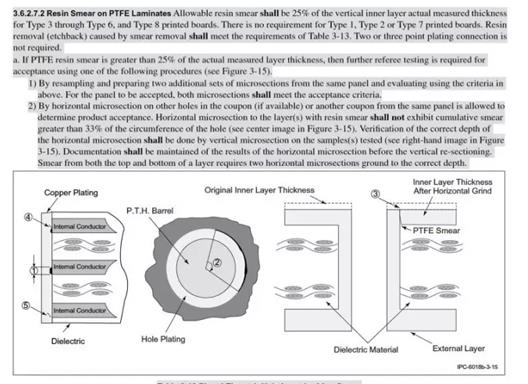

Theo tiêu chuẩn công nghiệp bảng mạch in IPC-6018B giải thích về bảng tần số cao, để xác định xem khiếm khuyết tách giữa các lớp trong bảng đa lớp PTFE có thể chấp nhận được hay không, ngoài việc đánh giá sơ bộ từ lát mài dọc, Cũng cần phải xác định các lát mài phẳng để xác định xem các tạp chất còn lại có lớn hơn 120O hay không, được giải thích cụ thể như sau:

2. Cơ chế sản xuất các khuyết tật tách giữa các lớp tấm nhiều lớp PTFE

So với dòng nhựa epoxy thông thường và dòng nhựa hydrocarbon, dòng nhựa PTFE có nhiều khả năng tạo ra các khuyết tật tách giữa các lớp khi xử lý các tấm nhiều lớp, chủ yếu là do bản thân vật liệu có các đặc tính của nhựa PTFE. Đầu tiên, PTFE là một loại nhựa nhiệt dẻo, chuỗi phân tử dài và không dễ uốn cong, và nóng chảy sẽ xảy ra ở nhiệt độ cao (>327 độ C); Thứ hai, nhựa polytetrafluoroethylene (PTFE) có khả năng kháng hóa chất tuyệt vời như "vua của nhựa" và phù hợp với phần lớn các hóa chất và dung môi, trơ, axit và kiềm mạnh, nước và nhiều dung môi hữu cơ.

Mặc dù hai điểm trên có thể được coi là lợi thế độc đáo của nhựa teflon, chế biến thứ cấp là "điểm đau". Trong quá trình xử lý PCB thực tế, vòng quay tốc độ cao của bit tạo ra rất nhiều nhiệt trong quá trình tiếp xúc với vật liệu PTFE, làm tan chảy nhựa PTFE trong vật liệu và dính vào bit. Khi con dao khoan được quấn lại, nhiệt độ được chuyển nhanh chóng bởi lá đồng bên trong khi nhựa nóng chảy một phần tiếp xúc với lá đồng bên trong. Khi nhựa PTFE nóng chảy sau khi nguội đi, nó gắn vào lớp đồng bên trong, tạo thành một loại có chứa dư lượng nhựa PTFE (bụi bẩn khoan), tiếp theo là hóa học (chất lỏng bụi bẩn khoan) hoặc vật lý (plasma) vào quá trình bụi bẩn khoan, gần như làm cho nhựa PTFE "bất lực", và cuối cùng bụi bẩn khoan còn sót lại này tạo ra một thiếu sót tách lớp mạ đồng trên lớp đồng bên trong.

Sơ đồ lỗ hổng tách giữa các lớp PTFE Multilayer

3. Hướng cải thiện các khuyết tật tách giữa các lớp PTFE đa lớp

Đối với các nhà sản xuất PCB đã xử lý các tấm đa lớp PTFE, hầu hết trong số họ đã trải qua "nỗi đau" do lỗi tách lớp. Nó cũng đã được đề xuất làm mát bằng khí lỏng cho các bit hoặc tấm được khoan theo thời gian để giải quyết sự thiếu hụt này hoặc sử dụng một số giải pháp oxy hóa mạnh "đặc biệt" để loại bỏ dư lượng PTFE dính vào đồng bên trong. Nhưng đáng tiếc là, xét về tính thực dụng (khả năng thao tác) và hiệu quả thực tế, phương pháp trên có hiệu quả rất nhỏ, không có ý nghĩa quảng bá ngành công nghiệp quy mô lớn.

Theo ý kiến của các tác giả, một nỗ lực chung của các nhà sản xuất vật liệu PTFE (hướng dẫn lựa chọn vật liệu), nhà máy bảng mạch PCB (tối ưu hóa quy trình) và khách hàng cuối cùng (phát triển và chấp nhận tiêu chuẩn) là cần thiết để cải thiện vấn đề tách bánh sandwich.

3.1 Lựa chọn vật liệu phù hợp

Trong cuộc trao đổi giữa tác giả và nhà máy sản xuất bảng mạch PCB hoặc kỹ sư OEM về bảng đa lớp PTFE, đầu tiên sẽ nhận được âm thanh tiêu cực của bảng đa lớp sản xuất PTFE, nhưng với chiều sâu của giao tiếp, Phát hiện ra rằng hầu hết kiến thức của khách hàng về bảng điều khiển đa lớp PTFE cũng dừng lại ở vật liệu bảng lõi PTFE truyền thống hơn 10 năm trước (hoặc vật liệu được gọi là bảng lõi PTFE thế hệ trước, chẳng hạn như TACONIC TLY 5, TLX-8, RF-35, v.v.), được đặc trưng bởi (1) hàm lượng nhựa PTFE cao (hàm lượng nhựa lên đến wT.75%); (2) Chứa sợi thủy tinh thô (ví dụ: 7628 sợi thủy tinh); (3) hàm lượng chất độn thấp (hoặc không có chất độn) và sử dụng vật liệu bảng lõi PTFE thế hệ trước để xử lý nhiều lớp, chắc chắn sẽ có những khiếm khuyết nghiêm trọng trong việc tách lớp.

Là vật liệu lõi PTFE thế hệ trước, TACONIC đã thành công trong việc đưa các vật liệu lõi PTFE đa lớp như TSM-DS3, EZIO-28 ra thị trường trong những năm gần đây. Hai vật liệu lõi PTFE thế hệ mới này phù hợp để sản xuất các tấm nhiều lớp được đặc trưng bởi: (1) hàm lượng chất độn cao (wT.75%+) và độ bóng cao của chất độn; (2) vải sợi thủy tinh mịn (ví dụ 106104); (3) Có thể kết hợp với lá đồng có độ nhám rất thấp. Nếu vật liệu phù hợp có thể được chọn từ giai đoạn lựa chọn ban đầu để xử lý nhiều lớp PTFE, nó sẽ cải thiện đáng kể hiệu quả của quá trình PCB trong việc cải thiện sự tách biệt giữa các lớp.

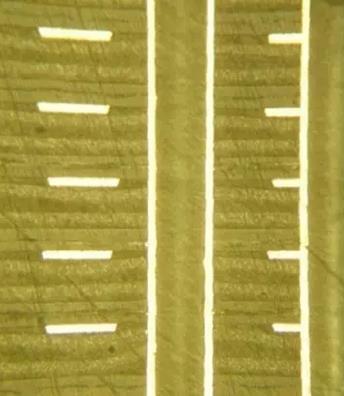

Bản vẽ lát tấm nhiều lớp

3.2 Tối ưu hóa các thông số gia công PCB

Đối với quy trình PCB, cần đặc biệt chú ý đến việc tối ưu hóa các thông số khoan và nhấn mạnh vào việc tìm kiếm sự cân bằng giữa cải tiến chất lượng và chi phí.

(1) Lựa chọn công cụ khoan: Chọn công cụ tối ưu hóa cho vật liệu PTFE, đặc biệt là những công cụ có hiệu suất loại bỏ chip tuyệt vời. Trong triết lý thiết kế của bit, khả năng xả chip có hai thông số thiết kế chính: góc xoắn ốc và độ dày lõi. Góc xoắn ốc càng lớn, độ dày lõi càng mỏng, rãnh chip của bit càng lớn, khả năng loại bỏ chip càng mạnh, tại thời điểm này, sự hợp tác giữa nhà máy bảng PCB và nhà cung cấp dụng cụ khoan là đặc biệt quan trọng;

b) Kiểm soát số lượng ngăn xếp. Cho dù PCB được xử lý dày như thế nào, nó là khoan từng cái một, sử dụng epoxy hoặc tấm đục lỗ lạnh làm tấm bìa trên và dưới;

(3) Kiểm soát số lỗ tối đa (đề nghị thay đổi công cụ ít hơn 200 lỗ). Đây là điểm kiểm soát đóng góp lớn nhất vào việc cải thiện tách lớp trong quá trình sản xuất PCB, nhưng cũng là liên kết đóng góp lớn nhất vào chi phí xử lý khoan, đòi hỏi nhà máy bảng PCB phải tìm điểm cân bằng.

(4) Các thông số khoan thích hợp. Theo kinh nghiệm của TACONIC, tốc độ quay và tốc độ cho ăn tương đối thấp có lợi hơn cho việc giảm chip khoan so với tốc độ quay cao và cho ăn nhanh, do đó cải thiện các khiếm khuyết tách giữa các lớp.

3.3 Thiết lập các tiêu chuẩn chấp nhận được cho khách hàng cuối (OEM)

Bản vẽ lát tấm nhiều lớp

Cho đến nay, trong thị trường truyền thông dân sự-quân sự, bảng tổng hợp PTFE không thực sự là một ứng dụng quy mô lớn, ngoài các tiêu chuẩn hiện tại của IPC, hầu hết các yêu cầu tách lớp OEM đã được mở rộng đến tiêu chuẩn chấp nhận chuyên nghiệp FR-4 truyền thống, Nhưng người viết cho rằng, do môi trường lắp ráp và ứng dụng của bảng hệ thống kỹ thuật số và bảng tần số vi sóng khác nhau, tiêu chuẩn nghiệm thu truyền thống còn phải bàn bạc. Rủi ro "không" và rủi ro "ở một mức độ nhất định" không thể được tóm tắt là chi phí chất lượng.

4. Ghi chú cuối

Để cải thiện các khuyết tật phân tách giữa các lớp của bảng đa lớp PTFE, các tiêu chuẩn lựa chọn vật liệu, xử lý PCB và chấp nhận của khách hàng nên được thực hiện. Tư duy hệ thống giúp thúc đẩy cải thiện sự tách biệt giữa các lớp để đạt được kết quả cải thiện tốt hơn.