Công nghệ kết nối cho chip đóng gói mạch tích hợp hiệu suất cao, độ tin cậy cao

Hướng phát triển thị trường của linh kiện điện tử (Đối với hội đồng mạch in PCBA)

Đối với các công nghệ trưởng thành của LSI với mức độ tích hợp và tốc độ cao hơn, cần phải phát triển các kỹ thuật cách ly sử dụng vật liệu K thấp khi thích hợp. Nhưng để đáp ứng hiệu suất cao của các đơn vị này, lớp cách ly ngày càng mỏng hơn do cấu trúc xốp và nhiều lớp. Do đó, LSI trở nên dễ bị tổn thương. Mặt khác, để đáp ứng các yêu cầu tốc độ cao, dòng điện LSI liên tục tăng lên. Ngoài kích thước chip từ lớn đến nhỏ, mật độ nhiệt và tiêu thụ điện năng cũng đang tăng lên. Do đó, đối với các chất nền đóng gói bán dẫn trong tương lai (đóng gói chất nền IC), những vấn đề này cần được giải quyết, cụ thể là độ giòn, nhiệt độ cao, tốc độ cao và chi phí thấp của môi trường giữa các lớp. Các cài đặt trước trong tương lai cho quy trình bán dẫn sẽ là 20nm trở xuống, sẽ yếu hơn nhiều.

Công nghệ đóng gói cần thiết cho thế hệ 20nm

Các thông số kỹ thuật cần thiết cho thế hệ 20nm tiếp theo là:

Ứng suất thấp cho lớp K giòn thấp

Bức xạ nhiệt cao 5W cho LSI hiệu suất cao

Tốc độ cao 10GHz cho chức năng cao

Hướng phát triển gói bán dẫn

Để phù hợp với sự tăng trưởng chức năng và giảm chi phí của các thiết bị điện, bao gồm cả thiết bị di động, các quy tắc đặt trước wafer đang hướng tới các quy tắc đặt trước lớn hơn, chi tiết hơn. Để giảm chi phí, công nghệ đóng gói chất bán dẫn đang nhanh chóng chuyển từ công nghệ tham gia dây vàng tiêu chuẩn nhất sang tham gia dây đồng, làm giảm lượng vàng được sử dụng. Ngoài ra, việc sử dụng công nghệ tương tác chip lộn ngược đáp ứng đáng kể mức độ tích hợp và hiệu suất cao hơn của LSI. Trong năm 2010, liên kết chip đảo ngược chiếm 15% công nghệ đóng gói chất bán dẫn toàn cầu và liên kết chì chiếm 85%. Đến năm 2015, tỷ lệ liên kết chip đảo ngược dự kiến sẽ đạt 25% và liên kết dẫn dự kiến sẽ đạt 75%. Đặc biệt là đối với LSI hiệu suất cao và tích hợp cao, đòi hỏi bức xạ nhiệt cao và tốc độ tín hiệu cao, công nghệ tương tác chip đảo ngược đang được xem xét tích cực là phù hợp.

Công nghệ chip lật Common Sense

Phù hợp với Low K

Công nghệ chip đảo ngược thường được sử dụng:

. Hàn các mặt liền kề, cấu trúc chính là C4 (thiết kế hợp tác chip giải quyết có kiểm soát)

. Được sử dụng để uốn loại Au-Bump và ACF

Liên kết siêu âm cho chữ ký loại AU-AU

Liên kết áp suất và liên kết siêu âm áp dụng áp suất cao và dao động cơ học trên LSI, vì vậy các phương pháp này không thể được sử dụng cho LSI K thấp. Vì vậy, trong các phương pháp trên, C4 có thể được sử dụng một cách thích hợp và do so sánh ba phương pháp, sự kết hợp phù hợp với thực tế là C4 gây ra thiệt hại tối thiểu cho chip.

Công nghệ C4 ra đời vào đầu những năm 40 cho các máy tính đa năng và đã được sử dụng liên tục. Khi số lượng chip Low K tăng lên, C4 được sử dụng cho Low K bằng cách thay thế cấu trúc UBM, vật liệu và cải tiến.

Sự phát triển gần đây của Cu-Column lồi (gần như tương tự như những tiến bộ của C4) phù hợp cho các đĩa hàn nội tuyến hoặc chồng chéo, không phải cho các chip K thấp. Các gói cấu trúc cột Cu được báo cáo có thể làm hỏng lớp k thấp do mô đun đàn hồi cao của Cu (130GPa). Sự không phù hợp của hệ số giãn nở nhiệt (CTE) là một yếu tố gia tốc.

Ngoài ra, công nghệ C4 ban đầu được coi là phù hợp với việc sử dụng các nút kim loại nóng chảy sau thông lượng và mô đun đàn hồi cao (50GPa) của thông lượng, do đó lượng ứng suất được thêm vào LSI trong quá trình liên kết và lắp đặt tấm mẹ do sự khác biệt trong việc mở rộng nhiệt. Do đó, công nghệ C4 không thể được sử dụng cho LSI trong tương lai, vốn yếu hơn nhiều.

Bức xạ nhiệt

Cho đến nay, lớp lót hữu cơ đã được sử dụng để đóng gói chip đảo ngược. Lớp lót hữu cơ có độ dẫn nhiệt nhỏ, 0,5W/MK và khó áp dụng cho LSI với mức tiêu thụ điện năng cao. Nếu hệ thống làm mát hoặc làm mát được thêm vào để cải thiện bức xạ nhiệt, chi phí đóng gói, kích thước và chiều cao của mặt phẳng hoặc bề mặt sẽ tăng lên.

Trên thực tế, do bức xạ nhiệt thấp, một điểm của LSI hạn chế tiềm năng của nó, do đó không tạo ra nhiều nhiệt. Ngoài ra, do bức xạ nhiệt không tốt, nhiệt độ nút thắt tăng lên và dòng điện rò rỉ tăng lên, điều này làm tăng thêm mức tiêu thụ điện năng và sự gia tăng tiêu thụ điện năng làm tăng nhiệt độ. Đó là một vòng luẩn quẩn nguy hiểm. Do đó, cải thiện bức xạ nhiệt là một vấn đề liên quan chặt chẽ.

Tốc độ cao của tín hiệu

Tổn thất thiệt hại trung bình cao (0,02) đối với lớp trung tâm của lớp lót hữu cơ và trở kháng (T/H) đối với lớp trung tâm thông qua lỗ cao. Kết quả là tổn thất thiệt hại chèn cao trong dải tần số cao. Tuy nhiên, sử dụng chất nền không lõi với cùng một vật liệu như chất nền hữu cơ truyền thống không phải là giải pháp cơ bản. Ngoài ra, vật liệu lớp composite có thể rất đa dạng, vì vậy người dùng khó chọn vật liệu tốt nhất và toàn bộ yêu cầu đặt trước phải xem xét vấn đề hiệu suất tốc độ cao.

Vì chất nền mỏng, một loạt các cơ sở cần được thay thế. Điều này trở thành một trở ngại cho sản xuất. Do vấn đề này, việc chuyển sang chất nền không lõi là rủi ro cao và chỉ phù hợp với các sản phẩm được bản địa hóa.

Công nghệ truyền thống rất khó đáp ứng nhu cầu của thế hệ 20nm trong tương lai. Do đó, cần phải phát triển một gói bán dẫn mới với công nghệ cốt lõi mới.

Các loại Monsterpac và các điểm thủ công

Monsterpac typec được phát triển để đáp ứng quy trình 20nm mà công nghệ đóng gói truyền thống khó có thể thích ứng. Điều này hoàn toàn khác với quy trình và cấu trúc đóng gói truyền thống.

Cấu trúc đóng gói

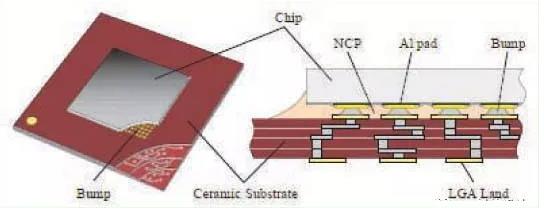

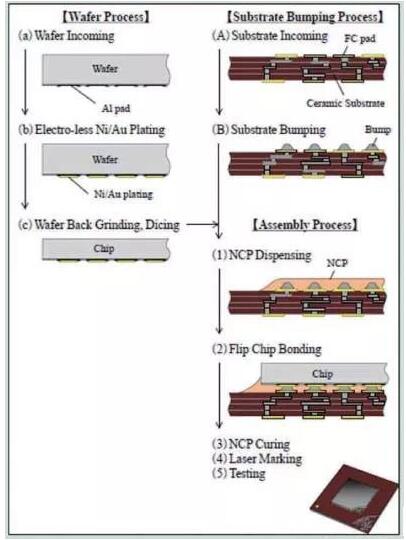

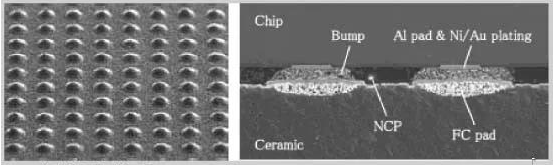

Cấu trúc đóng gói của chúng tôi, lớp lót là gốm, chip bán dẫn với nắp lật, chip và lớp lót bổ sung NCP (dán không dẫn). Nó không được đúc bằng khí epoxy hoặc nhựa tự nhiên. Mặt sau của con chip bị lộ. Hàn reflow có độ cong nhiệt độ cao nhỏ hơn 30-50μm và do đó được đóng gói dưới dạng LGA (Gói mảng tiếp xúc) không có bóng hàn thay vì BGA (Gói mảng lưới). Dán dẫn điện có chứa bạc được sử dụng cho các điểm lồi được in trên bề mặt để các mô-đun không còn được sản xuất trên đĩa hàn. Không mạ niken và vàng chỉ trên đĩa Al của chip, không có quy trình lồi wafer (Hình 1-3).

Cấu trúc đóng gói FIC-1

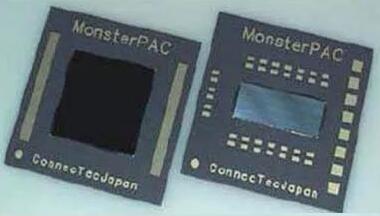

Hình ảnh gói FIC-2

Quy trình FIC-3

Tương tự như trên, gói của chúng tôi chỉ bao gồm 4 vật liệu (chip, lồi, gốm và NCP). Cấu trúc đơn giản này làm cho gói nhỏ, mỏng và nhẹ.

Có hai loại vật liệu nền gốm chính để lựa chọn: HTCC (High Temperature Co-Burning Ceramic) và LTCC (Low Temperature Co-Burning Ceramic). Các tính chất đặc biệt của gốm sứ (chẳng hạn như tính chất điện, dẫn nhiệt, CTE và cong vênh) và sự tham gia của chip đảo ngược cho phép gói của chúng tôi đáp ứng các giải pháp tốt nhất cho các yêu cầu khác nhau, từ các sản phẩm điện đến chip bán dẫn.

Cấu trúc kiểu Monsterpac độc đáo

Những địa điểm độc đáo này được mô tả như sau:

. Không dính thiệt hại

. Bức xạ nhiệt cao

. Mất chèn thấp

. Độ tin cậy cao

Bằng cách kết hợp những lợi ích chính này, MonsterPac TypeC đã thành công trong việc cung cấp hiệu suất tốt nhất có thể cho LSI thế hệ 20nm.

Không dính thiệt hại

Công nghệ cốt lõi của bao bì của chúng tôi là công nghệ liên kết chip đảo ngược không bị hư hại, thành công trong việc đạt được liên kết không bị hư hại và có độ tin cậy cao với chip bán dẫn được sản xuất bằng gia công chính xác tiên tiến.

Chip bán dẫn không bị hỏng là:

Liên kết áp suất thấp

Chúng ta có thể đạt được áp suất liên kết 0,12g/bump, đó là 1/20 áp suất 2,4g/bump của C4 bình thường. Bằng cách giảm tải trọng tham gia đến giới hạn này, thiệt hại cho môi trường giữa các lớp do tham gia có thể tránh được.

Căng thẳng co lại thấp trong quá trình bảo dưỡng bề mặt lồi

Căng thẳng co lại trong quá trình củng cố điểm lồi nhỏ hơn 10 MPA/điểm lồi và rất nhỏ. Năng suất cao và hàn ngược đáng tin cậy đã đạt được thành công bằng cách giảm nhiệt độ, tải và ứng suất co lại được áp dụng cho các lớp trung gian của môi trường giòn như K thấp và Al pad và đường dây, v.v., tránh đứt và nứt đường dây.

Như bạn có thể thấy từ những ưu điểm này, đây là gói duy nhất có cấu trúc để tránh thiệt hại cho lớp K thấp yếu.

Bức xạ nhiệt cao

Nhận ra rằng nhiệt của chip bán dẫn được bức xạ bởi chất nền gói, chúng tôi đã chọn chất nền gốm thay vì chất nền hữu cơ thông thường (độ dẫn nhiệt là 0,5W/mk) vì độ dẫn nhiệt của nó cao hơn 14W/mk so với chất nền hữu cơ. Khi kích thước gói là 21 * 21mm và khi sử dụng chất nền gốm, tiêu thụ điện năng đạt 6W, Nó mạnh hơn 1,7 lần so với chất nền hữu cơ có công suất tiêu thụ 3,6W.

Thấp chèn có thể làm tổn thương bạn

Thiết bị điện tử đòi hỏi mức độ hiệu suất cao trong dải tần số cao. Mất chèn cho lớp lót gốm là 0,42dB (@20GHz, L=5mm), trong khi mất chèn cho lớp lót hữu cơ là 0,62dB. Tần số cho phép của tấm cơ sở gốm lớn hơn 10 GHz và của tấm cơ sở hữu cơ là 3 GHz.

Độ tin cậy cao và chống ẩm cao

Điện trở trở lại bình thường (MSL: mức độ ướt) là mức 3 (@30DEG/60 100% RH192Hr). Mỗi Monsterpac typec có một chip bán dẫn không bị hư hỏng và các vết lồi được làm từ vật liệu không tan chảy. Ở nhiệt độ cao trở lại, các vết sưng không tan chảy, do đó, nó sẽ không lặp lại nóng chảy và tái bảo dưỡng, và chất nền gốm sẽ không hấp thụ độ ẩm. Do đó, MonsterPac Type C có xếp hạng MSL Class 1 (@85DEG/85 100% RH192Hr) để loại bỏ độ ẩm và bao bì chống ẩm mà không cần nướng trước và tuổi thọ thực vật của MonsterPac Type C là vô hạn.

Tốc độ tăng trưởng thực vật cao

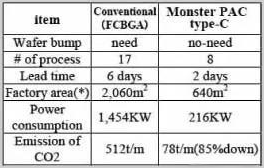

Để tạo điều kiện sản xuất, chúng tôi đã phát triển một cấu trúc lồi khí epoxy thay vì hàn lồi. Do đó, một số lượng lớn các cơ sở xử lý lồi wafer là cần thiết và chi phí của một lượng lớn có thể+hàn liền kề với reflow là cần thiết. Do đó, kích thước bề mặt phẳng hoặc bề mặt của thiết bị có thể giảm 69% và mức tiêu thụ năng lượng của thiết bị có thể giảm 85% so với các thiết bị quy trình C4 thông thường có cùng kích thước. Các nhà máy điện tiết kiệm năng lượng và tải nền thấp có thể đạt được thành công.

Công suất

Sự độc đáo của Monsterpac typec

Công nghệ gốm nâng cao

Monsterpac typec cho rằng việc sử dụng kem dẫn điện có chứa bạc làm vật liệu lồi là phù hợp. Một vết sưng được hình thành trên bề mặt gốm, tùy thuộc vào tình hình, bằng cách sử dụng kỹ thuật in phần SMD hàn thông thường. Không cần tiền xử lý và làm sạch bề mặt chất nền gốm trước khi xử lý cao hoặc mạ bề mặt sau khi hình thành cao. FCBGA hữu cơ truyền thống yêu cầu các điểm lồi dài trên đĩa Al của chip bán dẫn, chẳng hạn như thông lượng, Au và Cu. Tuy nhiên, các vết lồi dựa trên gốm không yêu cầu quá trình lồi dài wafer này. Thay vào đó, họ sản xuất Ni và Au không mạ điện trên chip bán dẫn. Các vết lồi dựa trên công nghệ gốm đã đạt được thành công một quy trình xử lý đơn giản và chi phí thấp.

Ngoài ra, không giống như các vết lồi cứng (độ cứng 10Hv) được sử dụng trong các kỹ thuật thông thường như thông lượng, Au và Cu lồi, các vết lồi mềm (1Hv) đã được phát triển để duy trì mô hình ở độ cứng thấp.

Đối với bùn dẫn điện lồi mềm có chứa bạc, chúng tôi đã phát triển các điểm cố định có liên quan có kinh nghiệm trong ứng suất thấp, lực cản chữ ký thấp và in nhựa đường chi tiết. Lực lượng lao động của các vết lồi mà chúng tôi đã hình thành cho đến nay là các mặt phẳng mảng: khoảng cách 150 angstrom; Hàn đĩa ngoại vi: Khoảng cách 75 đảo. Tuy nhiên, các quy tắc đặt trước thực tế xem xét khoảng cách giữa các tấm hàn này, do đó khoảng cách giữa các mảng bề mặt 60 ° m chỉ áp dụng cho các vết lồi mở.

Không dính thiệt hại

Sử dụng công nghệ tương tác chip đảo ngược mềm, NCP được sử dụng để phân phối các lồi mềm được hình thành bởi công nghệ lồi gốm, sau đó gắn chip bán dẫn với chip đảo ngược. Trong quá trình tham gia, dán dẫn điện và NCP của khối lồi được bảo dưỡng đồng thời. Kết quả là, chữ ký chung và độ tin cậy đã đạt được thành công.

Nhiệt độ tại cơ sở FCB dưới 200 độ C và thấp hơn 40 độ C so với công nghệ liên kết thông thường. Áp suất liên kết nhỏ hơn 0,12g/dot, bằng 1/20 công nghệ liên kết thông thường. Thông qua các liên kết ép nóng áp suất thấp, nhiệt độ thấp này, chip bán dẫn không bị ảnh hưởng bởi ứng suất và các lực bên ngoài trong quá trình liên kết và bảo dưỡng sau liên kết. Với bùn dẫn điện và NCP mới được phát triển, việc liên kết tốc độ cao dưới 1,0 giây đã được thực hiện thành công. NCP bao gồm các chất bổ sung thường được tìm thấy ở cả hai mặt của miếng đệm chip và miếng lồi. Tuy nhiên, nó là phổ biến để lật các phím chip ở áp suất thấp. Chất bổ sung này được chôn trong các vết lồi và do đó không ảnh hưởng đến chữ ký giữa các miếng đệm chip và các vết lồi. Đây là một trong những ưu điểm của Soft Bump. Sau khi phân phối NCP trước khi hàn ngược, NCP dễ dàng được bổ sung giữa các điểm lồi và khoảng cách hẹp, và với các phím tải thấp, sự liên kết giữa chip và chất nền không xảy ra. Do đó, kỹ thuật tham gia này phù hợp với khoảng cách hẹp giữa các tấm.

Vấn đề với kỹ thuật tham gia phổ biến là trong trường hợp tham gia chip lộn ngược với lồi hàn, ứng suất rút lại rất lớn (khoảng 200-500mPa/lồi) được áp dụng cho lồi của chip bán dẫn và mặt bích Al trong quá trình tan chảy thông lượng để chữa bệnh. Tuy nhiên, Kỹ thuật tham gia ứng suất thấp đã thành công vì mô đun đàn hồi thấp của vật liệu lồi không nóng chảy đòi hỏi ứng suất hồi phục rất nhỏ (dưới 10MPa/lồi).

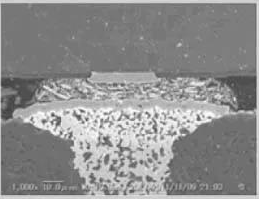

Đó là do quá trình phát triển của các công nghệ cơ bản nói trên mà sự thành công của hàn ngược không bị tổn hại. Hình 4 là điểm chính của chip đảo ngược và hồ sơ của chữ ký.

Hình 4 - Hình ảnh bên ngoài và mặt cắt

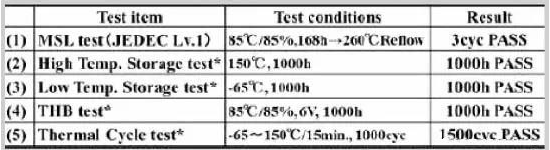

Độ tin cậy đóng gói

TC đã kiểm tra các đường viền của các điểm lồi phía sau, nhưng không kiểm tra và đo lường các vết nứt và loại bỏ quy mô có thể gây ra bởi các khớp nối gãy.

APIC (Thiết bị ứng dụng IC)

Gia công APIC ngày nay đang hướng tới gia công chính xác bằng cách sử dụng vật liệu Low K, đòi hỏi dung sai nhiệt độ cao và tốc độ cao. Monsterpac TypeC có những ưu điểm sau để đáp ứng các yêu cầu này.

. Không dính thiệt hại

. Bức xạ nhiệt cao

Khi tốc độ cao

Một số khách hàng APIC đang đánh giá quy mô sản xuất MonsterPAC TypeC

Loại PAC C

Là kết quả của việc đánh giá thực tế giữa FCBGA hữu cơ và Monsterpac Type C trong cùng điều kiện (cùng váy, cùng chip và cùng khoảng cách pad), nhiệt độ của Monsterpac Type C Tj thấp hơn 10 độ C so với gói hữu cơ. Sau khi so sánh Tj rất chính xác, sự khác biệt sẽ là khoảng 20 độ C.

Bảng tần số vô tuyến (Bảng tần số vô tuyến):

Hiện nay, đối với LSI truyền thông tốc độ cao, gói bo mạch đang được cải tiến liên tục. Các phần này cần các thuộc tính đặc biệt sau:

. Thích hợp cho tốc độ cao và tần số cao

Kích thước nhỏ

Đối với các ứng dụng tốc độ cao và tần số cao, như đã đề cập ở trên, việc sử dụng lớp lót gốm có thể cải thiện tổn thất chèn, nếu thích hợp, có thể được sử dụng cho 10GHz.

Ngoài ra, nhiều chip và một số lượng lớn các thành phần SMD có thể được sử dụng trong các gói nhỏ vì chúng có thể được tham gia bằng cách sử dụng các chip đảo ngược nhỏ, khoảng cách chi tiết.

Hợp tác với khách hàng để mở mẫu bảng tần số phát xạ, hiệu suất của nó đã được khách hàng công nhận và đang chuẩn bị sản xuất quy mô lớn

Mô-đun RF

Đối với những tấm vỏ này, độ ẩm của chất nền là rất chặt chẽ. MSL của Monsterpac TypeC là Cấp 1, vì vậy không có nghẹt thở ướt.

Có thể thấy rằng monsterPAC TypeC là tốt nhất cho các gói phẳng, với các gói hữu cơ truyền thống SMD và chip đảo ngược yêu cầu nhiều lần hàn trở lại.

Thẩm phán

Đối với quy trình 20nm thế hệ tiếp theo, cần phải đóng gói để phù hợp với bức xạ nhiệt cao hơn và tốc độ cao hơn. Tuy nhiên, công nghệ đóng gói thông thường rất khó để đáp ứng các yêu cầu này. Do đó, cần phải phát triển một công nghệ đóng gói mới phù hợp với quy trình 20nm.

Monsterpac TypeC của chúng tôi phù hợp với quy trình 20nm sắp tới và tối đa hóa hiệu suất LSI. Hiệu suất cao của nó giống như một sản phẩm kỳ lạ đáng kinh ngạc. MonsterPAC mà chúng tôi đã phát triển đã khiến C4 trở nên lỗi thời và trở thành công nghệ chính cho thế hệ chất bán dẫn tiếp theo trong tương lai.

Phát triển công nghệ thế hệ tiếp theo

Nghiên cứu và phát triển chất nền gốm mới

Sự phát triển của công nghệ lát gốm luôn tươi sáng. Cho đến nay, các bản vẽ chính xác và chi tiết với mật độ cao đã tụt hậu xa so với các chất nền IC hữu cơ.

Để giải quyết vấn đề này và đạt được tiến bộ, chúng tôi đã tiến hành phát triển một chất nền gốm chính xác với mật độ cao mà không ảnh hưởng đến chi phí. Mục tiêu của chúng tôi là khoảng cách đường 20 ° m để đạt được độ chính xác phù hợp và sử dụng đồ họa chi tiết linh hoạt hơn. Theo mặc định, khoảng cách qua lỗ cũng cần chính xác và chi tiết hơn, với mục tiêu là 50 ° m.

Cho đến nay, chất nền gốm đã được làm bằng cách sử dụng dập và in mặt nạ, tùy thuộc vào từng trường hợp. Những kỹ thuật hiện có này bị giới hạn trong việc vẽ chính xác và chi tiết. Chúng tôi đang xem xét thay thế chúng bằng laser và quy trình in trực tiếp. Thực hiện công nghệ này sẽ mang lại hiệu suất tốt hơn so với chất nền hữu cơ. Cho đến nay, chất nền gốm thường được sử dụng trong các sản phẩm cao cấp, nhưng chất nền mới này sẽ nhắm vào hàng tiêu dùng. Ma trận thực sự cần hàng tiêu dùng hiệu suất cao để phát triển từ tôi.

Sự kết hợp của chất nền này với công nghệ MonsterPAC sẽ cung cấp cho thế giới bảng mạch in (PCB) với hiệu suất tốt nhất và độ tin cậy cao.