L, Phức chip hoà khí thiết kế process

Được. process of sản xuất con chip là like building a house with LEGO. Sau khi dùng bánh quế như là móng, và sau đó quá trình sản xuất con chip được xếp chồng lên từng lớp, có cần thiết Ô'lề mề can be produced (làse will be introduced later). Tuy, không vẽ thiết kế, Thật vô dụng khi có một sức mạnh sản xuất. Do đó, Kiến trúc rất quan trọng. Nhưng ai là kiến trúc sư ở Description thiết kế? Tiếp, Tờ giấy này sẽ giới thiệu Description thiết kế.

Vào trong Sản phẩm Description process, nhiều DescriptionNó được thiết kế và thiết kế bởi người chuyên nghiệp Description Công ty thiết kế, như MediaTek, Nửa, Vàotel và những nhà sản xuất nổi tiếng, tất cả thiết kế riêng chip hoà khívà cung cấp chip với các đặc điểm và hiệu quả khác nhau cho các nhà s ản xuất xuôi dòng. Vì Description được thiết kế bởi mỗi nhà máy, Description thiết kế phụ thuộc vào công nghệ của kỹ sư, và chất lượng kỹ sư ảnh hưởng đến giá trị của một công ty. Tuy, Khi các kỹ sư thiết kế... chip hoà khí, những bước chân là gì?? Thiết kế có thể đơn giản được chia thành.

Công trình lắp ráp

Thiết kế bước đầu tiên và mục tiêu.

Vào Thiết kế Description., Bước quan trọng nhất là sự xác định. Bước này giống như quyết định bao nhiêu phòng tắm cần thiết trước khi thiết kế tòa nhà, những quy tắc xây dựng cần được tuân thủ, và thiết kế sau khi phân tích mọi chức năng, để không dành thêm thời gian sửa đổi sau đó. Description thiết kế cũng cần phải đi qua những bước tương tự để đảm bảo rằng con chip được thiết kế sẽ không bị lỗi..

Bước đầu tiên trong quy định là để xác định mục đích và hiệu quả của Description và đặt hướng chung. Bước tiếp lào là xem thủ tục nào để thực hiện. Ví dụ như, Con chip của thẻ mạng không dây cần phải đáp ứng với IEE 802.Chính tả Keywords. Không, con chip sẽ không được tương thích với các sản phẩm trên thị trường., làm cho nó không thể kết nối với các thiết bị khác. Cách cuối cùng là thiết lập phương pháp tiến hành Description, phân bổ các chức năng khác nhau, và xác định phương pháp kết nối giữa các đơn vị khác nhau, để hoàn tất việc mô tả kỹ thuật..

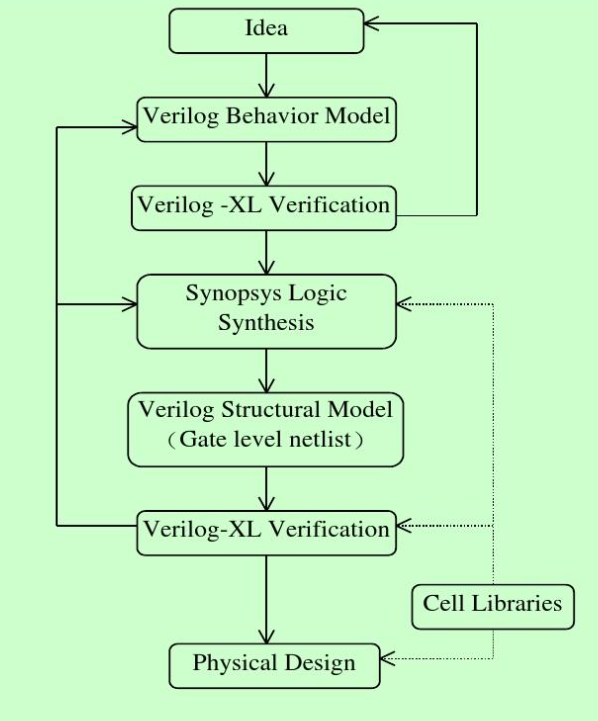

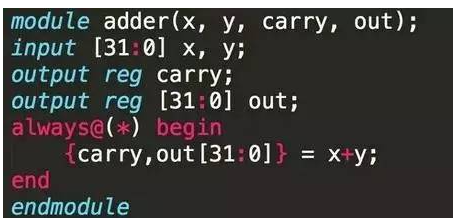

Sau khi thiết kế kỹ thuật, theo chi tiết thiết kế con chip. Việc này giống như việc viết lại kế hoạch kiến trúc đầu tiên và vẽ ra sơ đồ tổng hợp cho việc vẽ tiếp theo. Vào chip hoà khí, hardware description language (HDL) is used to describe the mạch. Được. commonly used HDL includes Verilog, VHDL, Comment. chức năng của một Description có thể dễ dàng diễn tả bằng mật mã. Sau đó kiểm tra sự đúng của chức năng chương trình và tiếp tục sửa đổi nó cho đến khi nó đạt được chức năng cần thiết..

Ví dụ Verilog of 32 Bit phụ bếp

Với máy tính, mọi thứ trở nên dễ dàng.

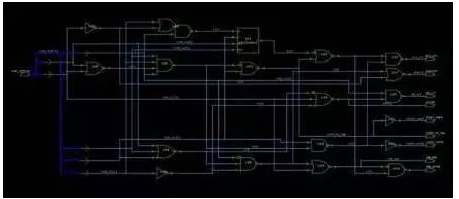

Với một kế hoạch hoàn chỉnh, bước tiếp theo là vẽ một bản thiết kế bảng. Trong thiết kế hoà khí sinh học, giai đoạn tổng hợp logic là đặt mật mã HDL đã được xác định vào công cụ tự động thiết kế điện tử (công cụ nở A) và để máy tính chuyển đổi mật mã HDL thành mạch logic để sản xuất sơ đồ mạch sau đây. Sau đó, lặp đi lặp lại xác định xem bức vẽ kiểu cổng logic có khớp với các yêu cầu và sửa đổi nó cho đến khi chức năng này đúng.

Kết quả tổng hợp bộ điều khiển

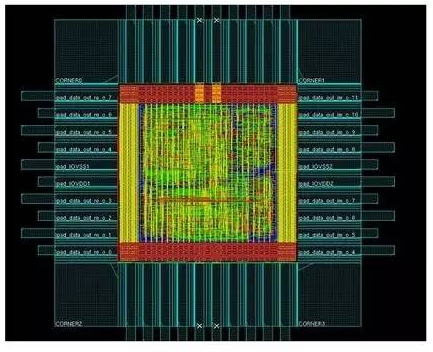

Cuối cùng, đặt đoạn mã tổng hợp vào một loạt công cụ EDA khác để bố trí mạch, nơi và tuyến đường. Sau khi phát hiện liên tục, sẽ được hình thành sơ đồ mạch sau. Trong ảnh, bạn có thể thấy nhiều màu khác nhau như xanh, đỏ, xanh và vàng. Mỗi màu khác nhau đại diện cho mặt nạ ánh sáng. Còn cách dùng mặt nạ?

bố trí và đường cong

Lớp mặt nạ, xếp con chip

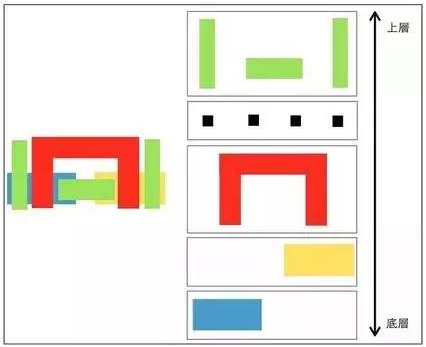

Trước hết, It is known that Description sản xuất nhiều mặt nạ. Những mặt nạ này có lớp trên và dưới, và mỗi lớp có nhiệm vụ riêng. Một hình ảnh đơn giản về mặt nạ. Lấy CM, yếu tố cơ bản nhất trong các mạch tổng hợp, như một ví dụ, mà tên đầy đủ của CM chỉ là.....một loại khí quản sắt vụn, đó là, kết hợp NMOS và PMOS để tạo ra CMOS. As for what is metal oxide semiconductor (MOS)? Loại thành phần được sử dụng rộng rãi trong chip rất khó giải thích., và rất khó cho người đọc hiểu. Tôi sẽ không học ở đây nữa..

Trong hình vẽ bên dưới, bên trái là sơ đồ mạch được hình thành sau sơ đồ mạch và đường cong. Ai cũng biết mỗi màu là một mặt nạ. Bên phải là độ trải rộng của từng mũ trùm. Sản xuất bắt đầu từ phía dưới, theo phương pháp được đề xuất trong bài báo trước về sản xuất các chip Description, làm chúng từng lớp một, và cuối cùng sản xuất con chip được mong muốn.

Đến giờ, Chúng ta nên có một sự hiểu biết sơ bộ về... Thiết kế Description.. Toàn bộ, Rõ ràng là Description thiết kế is a very complex specialty. Nhờ vào sự trưởng thành của phần mềm máy tính, Description thiết kế can be accelerated. The Description xưởng thiết kế dựa vào kiến thức của kỹ sư.. Mỗi bước được mô tả ở đây có chuyên môn riêng và có thể được phân loại độc lập thành nhiều khóa chuyên nghiệp.. Ví dụ như, Viết ngôn ngữ mô tả phần cứng không đơn giản. Nó chỉ cần quen thuộc với ngôn ngữ lập trình., nhưng cũng cần phải hiểu làm thế nào mà mạch logic hoạt động và làm thế nào để chuyển đổi các thuật to án cần thiết thành các chương trình như thế nào mà phần mềm tổng hợp có thể chuyển đổi chương trình thành các cổng logic.

2, bánh quế là gì?

Trong tin tức của Name, chúng tôi luôn đề cập đến nhà máy bánh quy có kích cỡ, như hãng bánh quế 8-inch hay 12-inch. Tuy, cái gọi là bánh quế? Phần nào là 5cm? Có khó sản xuất bánh quy lớn không?? Những bước tiếp theo là giới thiệu từng bước cho nền tảng đầu tiên của người thầy giáo "bánh quế"..

Đánh sáp là cơ sở để sản xuất các loại chip máy tính. Chúng ta có thể so sánh sản xuất chip với việc xây nhà với các khối Lego, và hoàn thành hình dạng mong muốn (tức là, mọi loại phỉnh) bằng cách xếp lớp này sau lớp khác. Tuy nhiên, nếu không có nền tảng vững chắc, ngôi nhà được xây sẽ bị đảo lộn, đó không phải là điều anh muốn. Để tạo ra một ngôi nhà hoàn hảo, bạn cần một đĩa nền ổn định. Đối với sản xuất chip, phương tiện này là bánh quế được mô tả tiếp theo.

Trước hết, hãy nhớ rằng khi chúng ta chơi với những khối cao tầng khi còn nhỏ, s ẽ có một hình chiếu tròn nhỏ trên bề mặt các khối nhà. Với cấu trúc này, chúng ta có thể gắn chặt hai khối đá với nhau mà không cần dùng keo. Chế độ sản xuất Chip cũng sửa chữa các nguyên tử sau đó thêm và các phương diện tương tự. Do đó, chúng ta cần tìm một phương tiện có bề mặt ngăn nắp để đáp ứng các điều kiện cần thiết cho việc sản xuất tiếp theo.

Nguyên liệu rắn, có một cấu trúc tinh thể đặc biệt. Nó có đặc tính là các nguyên tử được sắp xếp chặt chẽ từng cái một., và có thể hình thành một bề mặt nguyên tử phẳng. Do đó, những yêu cầu này có thể được đáp ứng bằng cách dùng một tinh thể để làm bánh quy. Tuy, làm thế nào để sản xuất vật liệu này? Có hai bước chính: tẩy rửa và vẽ pha lê, và sau đó một vật liệu có thể hoàn thành.

Cách tạo một phòng đơn bào chế pha lê

Sự thanh tẩy được chia thành hai giai đoạn.. Bước đầu tiên là sự thanh lọc kim loại. Cách này đã được tốt chức sự hồn động carbon và biển động oxiṭ silicon và với sự tinh khiết cao hơn được 97.. Nhiều xưởng luyện kim loại, như sắt hay đồng, dùng phương pháp này để đạt được kim loại thuần khiết vừa đủ. Tuy, Tài sản sản sản sản sản phụ sản sản sản sản sản phụ sản sản phụ sản sản sản sản sản sản phụ sản cũng không đủ.. Do đó, Công trình Siemens sẽ được dùng thêm để thanh lọc. Theo cách này, Một tài thiếu biệt cách thiết sự quang của a a a a ã.

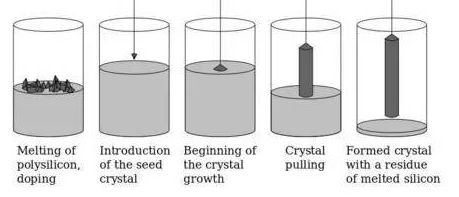

Quá trình sản xuất cột Silicon

Bước tiếp theo là vẽ pha lê. Thứ nhất, loại polysilicon loại cao khiết được lấy ở trên được nung chảy để làm silicon lỏng. Liên kết với bề mặt nước với một hạt giống pha lê và từ từ kéo nó lên khi quay. Về lý do tại sao lại cần đến silicon pha lê, thì đó là vì sự sắp đặt của các nguyên tử silicon cũng giống như của những người xếp hàng. Nó cần một người lãnh đạo để sau này mọi người biết cách sắp xếp đúng cách. Hạt giống Silicon là một lãnh đạo quan trọng để cho các nguyên tử sau này biết cách xếp hàng. Cuối cùng, sau khi các nguyên tử silicon rời khỏi bề mặt lỏng tụ lại, những cái cột silic đơn đơn được sắp xếp gọn gàng được lắp ráp.

Cột silicon đặc trưng

Tuy nhiên, 5cm và 5cm thì có gì? Anh ta đề cập tới đường kính đường kính của những cột pha lê do chúng tôi sản xuất, trông giống như một phần của cây bút chì. Bề mặt được điều trị và cắt thành từng mảnh tròn mỏng. Có khó khăn gì để làm bánh quy lớn?

Như đã đề cập, quá trình sản xuất cột pha lê giống như làm kẹo bông, quay và hình cùng lúc. Nếu em từng làm kẹo dẻo, Bạn nên biết rằng rất khó để làm ra kẹo dẻo lớn và rắn chắc, và quá trình vẽ pha lê cũng như nhau. Tốc độ quay và điều khiển nhiệt độ sẽ ảnh hưởng đến chất lượng cột pha lê. Do đó, to hơn kích cỡ, Tốc độ và nhiệt độ càng cao. Do đó, để làm bánh quế cấp cao cấp cấp cấp mm hơn bánh quế 5cm.

Tuy, cả một cái cột silicon không thể biến thành một cái nền để sản xuất chip. Để sản xuất bào xương bằng silicon từng cái một, cần phải cắt ngang cột silicon thành bánh quế bằng dao kim cương, và sau đó bánh quy có thể đánh bóng thành những cái bào gạo bằng silicon. Sau bao nhiêu bước đi, đã hoàn tất việc sản xuất đĩa nền. Tiếp theo là xếp nhà, đó là, chip sản xuất. Còn về việc làm phỉnh?

Layers of stacked chips

After introducing what silicon wafers are, Tôi cũng biết rằng sản xuất Ô'lề mề is like building a house with Lego blocks, tạo ra hình dạng cần thiết bằng cách xếp lớp sau lớp. Tuy, có vài bước để xây một ngôi nhà, và họ cũng vậy. Description manufacturing. Các bước để làm gì? Description? Tờ giấy này sẽ đưa ra tiến trình của... chip hoà khí manufacturing.

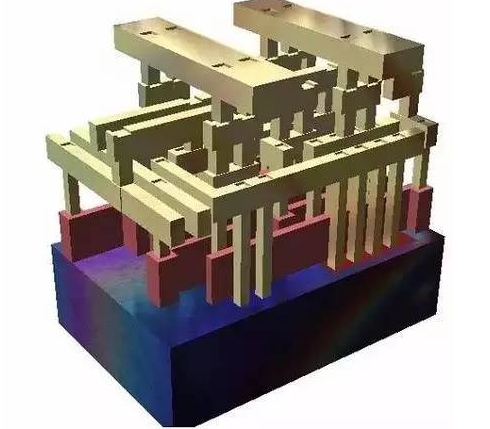

Trước khi bắt đầu, Chúng ta phải hiểu trước đã chip hoà khí is. Description, tên đầy đủ của hệ thống điện tử, có thể nhìn thấy từ tên của nó rằng nó kết hợp mạch được thiết kế theo một cách xếp. Dùng phương pháp này, chúng ta có thể giảm vùng cần thiết để kết nối mạch điện. The following figure is a 3D Diagramma of Description mạch. Có thể thấy được cấu trúc của nó như xà và cột của một ngôi nhà, chồng lông từng lớp, đó là lý do Description Sản xuất được so với việc xây một ngôi nhà.

Vị trí 3D của chip hoà khí

Từ hồ sơ 3D của con chip Description ở hình bên trên, phần màu xanh thẫm ở dưới là phần bánh quế được nhập vào bài báo trước. Từ hình vẽ này, chúng ta có thể biết rõ tầm quan trọng của lớp đất đóng vào con chip. Còn phần đỏ và kaki, nó sẽ được hoàn thành trong suốt các sản phẩm của Description.

Trước hết, Phần màu đỏ có thể so sánh với sảnh ở tầng trệt của tòa nhà cao tầng.. Phòng ở tầng một là cửa ngõ của một ngôi nhà.. Đó là nơi người ta đi vào và ra. Nó thường có nhiều chức năng hơn dưới sự điều khiển giao thông. Do đó, so với những tầng khác, Cấu trúc sẽ phức tạp hơn và cần nhiều bước. Vào trong Description circuit, Phòng này là lớp vỏ cổng logic, mà là phần quan trọng nhất của toàn bộ Description. Một loạt các cổng logic được kết hợp để hoàn thành chip hoà khí với đầy đủ chức năng.

The yellow part is like a general floor.. So với tầng một, nó sẽ không có cấu trúc quá phức tạp, và mỗi tầng sẽ không thay đổi nhiều trong lúc xây dựng. Mục đích của lớp này là kết nối các cổng logic ở phần đỏ với nhau. Lý do tại sao nhiều lớp cần đến là vì có quá nhiều đường dây có thể kết nối với nhau. Khi một lớp không thể chứa tất cả các dòng, Phải xếp vài lớp mới đạt được mục tiêu này. Trong quá trình này, đường dây của các lớp khác sẽ được nối lên và xuống để đáp ứng các yêu cầu dây dẫn..

Layered construction and layer by layer structure

After knowing the structure of Description, chúng tôi sẽ giới thiệu làm thế nào để tạo ra nó. Hãy tưởng tượng nếu chúng ta muốn vẽ một bức tranh đẹp với một bình xịt sơn, Chúng ta cần cắt tấm hình bìa của tấm hình và đưa lên báo.. Rồi spray the paint evenly on the paper. Sau khi sơn khô, tháo chốt chắn. Sau khi lặp lại bước này, Các hình ảnh phức tạp và gọn gàng có thể hoàn thành. Sản xuất Description là chồng thành từng lớp bằng cách bọc một cách tương tự.

Khi làm Description, nó có thể đơn giản được chia thành bốn bước trên. Mặc dù các bước sản xuất và các vật liệu đã được sử dụng khác nhau trong thực tế, Nguyên tắc tương tự được thông qua. Quá trình này hơi khác so với sơn họa.. Description Đầu tiên được phủ xong bọc, trong khi vẽ sơn được che trước và sau đó sơn lại. Mỗi tiến trình được mô tả bên dưới.

-tóe nước kim loại: rải đồng loạt các vật liệu kim loại cần dùng trên bánh để làm mảnh mỏng.

-Liệu pháp Coating: phát đầu tiên chất liệu chống photon trên bánh quế., pass through the mask (the principle of the mask will be explained kế time), trúng tia sáng vào phần không mong muốn, và phá hủy cấu trúc của vật liệu liệu có chạm khắc. Rồi, Các vật liệu bị hư hỏng được rửa sạch bởi các hóa chất..

-Công nghệ chạm vết: Bánh quế bằng silicon mà không có sự bảo vệ ánh sáng được khắc lên bởi chùm tia ion.

-Xóa photon: hủy bỏ các liệu pháp còn lại bằng cách dùng dung dịch gỡ bỏ photon, để hoàn thành một quá trình.

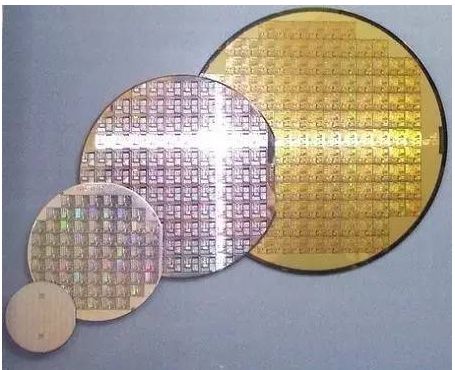

Cuối, nhiều Ô'lề mề will be completed on a whole wafer. Tiếp, miễn là quảng trường đã hoàn thành chip hoà khíđã bị cắt đứt, chúng có thể được gửi đến... Name nhà máy Name. Cái gì? Name nhà máy? Tôi sẽ giải thích sau..

Đối tượng bánh quế với kích thước khác nhau

3, quá trình cấu tạo nano là gì?

Samsung và TSMC rất nóng trong quá trình chế tạo khí quản tiên tiến. Cả hai đều muốn lãnh đạo ở xưởng đúc bánh quế để giành được lệnh. Nó gần như trở thành tranh chấp giữa 1mm và 16nm. Tuy, Điều gì là nghĩa của hai con số là 14K và 16nm, và nó đề cập đến phần nào? Sẽ có lợi ích gì trong tương lai sau khi giảm quy trình? Chúng ta sẽ giải thích ngắn gọn về tiến trình nano.

Thật là tinh tế. NanoNameName?

Trước khi bắt đầu, Chúng ta phải hiểu nano nghĩa là gì. Toán, nanotetơ là 0..9m 00000000000000000kg, nhưng đây là một ví dụ rất tệ. Rốt cuộc rồi., Chúng ta chỉ có thể thấy nhiều số không sau các số thập phân., Nhưng chúng t ôi không có cảm giác thực tế. Nếu so sánh độ dày của móng, nó có thể rõ ràng hơn.

Nếu bạn thật sự đo được với thước kẻ và thước đo, bạn có thể biết rằng độ dày của móng là khoảng 0.0001 meter (0.1 mm), đó là, Hãy cố gắng cắt một móng vô hàng ngàn đường., và mỗi dòng là một mm. Do đó, You can imagined how small 1 mm is.

Sau khi biết được nhỏ nano, Chúng ta cũng nên hiểu ý định giảm quy trình. Mục đích chính của việc phân hủy bán dẫn là cho thêm các bán dẫn vào các con chip nhỏ hơn, để các con chip không phát triển hơn vì tiến bộ công nghệ, Thứ hai, nó có thể tăng hiệu quả hoạt động của người điều hành; Thêm, giảm lượng cũng có thể giảm lượng điện tiêu thụ; Cuối, sau khi độ lớn của con chip bị giảm, Sẽ dễ dàng cắm nó vào thiết bị di động để đáp ứng nhu cầu của độ nhẹ trong tương lai..

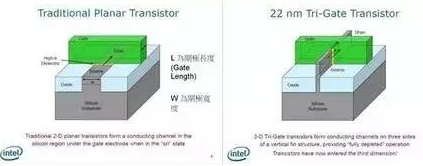

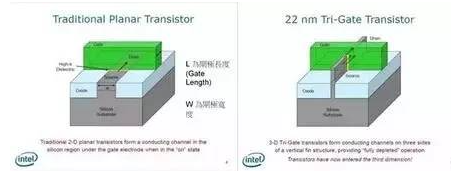

Rồi quay lại khám phá xem tiến trình nano là gì. Lấy 14 nm làm ví dụ. Quá trình đề cập đến sợi dây nhỏ nhất trong con chip có thể là 14 nm.. Thí dụ như hình mẫu của các bán dẫn truyền thống. Mục đích chính của việc giảm bán dẫn là giảm lượng điện tiêu thụ, nhưng phần nào cần giảm để đạt được mục đích này?

Chữ L ở phần dưới bên trái là phần chúng ta mong muốn thu nhỏ lại.. Bằng cách giảm độ dài cổng, the current can use a shorter path from the drain end to the source end (if you are interested, bạn có thể dùng Google để tìm MOSSET, which will be explained in more detail).

Hơn nữa, máy tính vận hành trên 0 và 1. Làm sao bán dẫn có thể đạt được mục đích này? Phương pháp này là phán xét liệu bán dẫn có lưu lượng hiện thời hay không. Khi điện thế được cung cấp tại cổng điện (Quảng trường Green), dòng điện sẽ chảy từ thiết bị dẫn đến thiết bị nguồn. Nếu không cung cấp điện, dòng điện sẽ không chảy, vì vậy nó có thể đại diện cho 1 và 05239; 188;1366; Về lý do tại sao chúng tôi dùng 0 và 1 để phán xét, nếu bạn quan tâm, bạn có thể kiểm tra đại số Brin. Chúng tôi dùng phương pháp này để chế tạo máy tính.)

Size reduction has its physical limitations

Tuy, quá trình sản xuất không thể giảm vô hạn. Khi ta giảm bán dẫn đến khoảng 20nm, chúng ta sẽ gặp vấn đề trong vật lý lượng tử, để bộ bán dẫn rỉ, bù l ại lợi ích khi tôi bị giảm. Như một phương pháp cải tiến, the concept of FinFET (tri gate) is introduced, như hiển thị trên hình phải. Trong lời giải thích trước của Intel, có thể biết rằng việc sử dụng công nghệ này có thể giảm sự rò rỉ do hiện tượng vật lý gây ra..

Quan trọng hơn, phương pháp này có thể tăng cường vùng tiếp xúc giữa đầu cổng và lớp dưới. Trong thực tế truyền thống (ở phía trên trái), bề mặt tiếp xúc chỉ có một mặt, nhưng sau khi sử dụng công nghệ FinFET (ba cổng), bề mặt tiếp xúc sẽ trở nên ba chiều, mà có thể dễ dàng tăng cường vùng tiếp xúc. Bằng cách này, nguồn thoát nước có thể nhỏ hơn trong khi vẫn duy trì cùng một vùng liên lạc, rất có ích để giảm kích thước.

Cuối, Đó là lý do có người nói rằng các nhà máy lớn sẽ phải đối mặt với những thử thách khá nghiêm trọng khi bước vào quá trình 10M. Nguyên nhân chính là kích thước của một nguyên tử là 0.1 nm. Trong trường hợp 10 phút, chỉ có ít hơn 100 nguyên tử trong một đường, mà rất khó để làm, và miễn là có một nhược điểm của một nguyên tử, như các nguyên tử rơi ra hoặc các chất trong quá trình sản xuất, Sẽ có một hiện tượng chưa rõ, sẽ ảnh hưởng đến sản lượng của nó.

Nếu bạn không thể t ưởng tượng được khó khăn, Bạn có thể làm một thí nghiệm nhỏ. Line up a 10 with 100 beads on the table * 10 square, và cắt một mảnh giấy để che những viên xâu., Sau đó lấy chuỗi hạt tiếp theo bằng một cái bàn chải nhỏ, and finally make him form a 10 * A rectangle of 5. Theo cách này, Chúng ta có thể biết được những khó khăn mà các nhà máy lớn phải đối mặt, và rất khó khăn để đạt được mục tiêu này..

As Samsung and TSMC will complete the mass sản xuất of 14 nm and 16 nm FinFET in the near future, Cả hai đều muốn cạnh tranh về OEM của chip iPhone thế hệ mới của Apple.. Chúng ta sẽ thấy một cuộc cạnh tranh thương mại tuyệt vời và có nhiều điện thoại di động tiết kiệm sức mạnh và gọn nhẹ.. Nhờ vào lợi ích của luật Moore.

4, Nói bạn nghe trại tế bào là gì

Name, cuối cùng bảo vệ và hòa nhập chip hoà khí

Sau một quá trình dài, từ thiết kế đến sản xuất, Cuối cùng chúng ta đã có... chip hoà khí. Tuy, một con chip khá nhỏ và mỏng. Nếu nó không được bảo vệ bên ngoài, nó sẽ dễ dàng bị trầy và hư hại. Thêm nữa., bởi vì kích thước con chip rất nhỏ, Sẽ không dễ dàng để đặt nó vào bảng mạch mà không có vỏ bọc lớn hơn.. Do đó, Tờ giấy này sẽ mô tả và giới thiệu Name next.

Hiện tại, có hai gói hàng chung, một là gói nhúng thường dùng trong đồ chơi điện tử., mà giống như một con rết trong bộ đồ đen, và còn lại là gói bưu kiện BGA phổ biến khi mua CPU được đóng hộp.. Như những người khác Name phương pháp, PGA (pin grid array) used by early CPUs; Pin grid array) or improved QFP (plastic square flatpack) of dip. Bởi vì có quá nhiều. Name phương pháp, nhúng và BGA Name sẽ được đưa vào bên dưới.

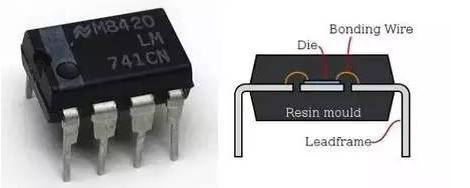

Description Name, lasting

The first thing to introduce is the dual inline package; Dip), như có thể nhìn thấy từ hình tượng bên dưới, the chip hoà khí với gói hàng này sẽ trông giống một con rết đen ở chân của sự kết nối hàng đôi, thật ấn tượng.. Đây. Name phương pháp là sớm nhất Description Name công nghệ, có lợi thế với giá thấp và thích hợp cho những con chip nhỏ mà không có quá nhiều dây. Tuy, bởi vì hầu hết chúng là nhựa, Áp lực phân tán nhiệt rất thấp., mà không thể đáp ứng yêu cầu của những con chip tốc độ cao hiện tại. Do đó, Phần lớn các chip dùng gói này là các chip bền bỉ, như khoảng 741 trong con số bên dưới, or chip hoà khíBộ phận tốc độ hoạt động ít hơn, Các thẻ nhỏ hơn và ít lỗ kết nối.

Khung xem ngang

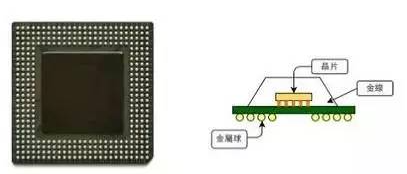

Còn về mảng lưới bóng (kiểu BGA) là bao đóng, so với nhúng, thì lượng đóng hộp nhỏ hơn và có thể dễ đặt vào các thiết bị nhỏ hơn. Hơn nữa, vì cái chốt nằm bên dưới con chip, nó có thể chứa nhiều chốt kim loại hơn nhúng, nó rất thích hợp với loại chip yêu cầu nhiều tiếp xúc. Tuy nhiên, phương pháp đóng gói này có giá cao và phương pháp kết nối phức tạp, nên nó hầu hết được dùng trong các sản phẩm với giá bán lẻ cao.

Biểu đồ quét biểu đồ của BGA dùng gói lật con chip

Với sự phát triển của các thiết bị di động, các công nghệ mới đã nhảy lên sân khấu

Tuy, dùng chúng Name phương pháp sẽ thu hút một lượng lớn. Ví dụ như, Thiết bị di động và thiết bị đeo được đòi hỏi rất nhiều thành phần. Nếu mỗi thành phần được bọc độc lập, nó sẽ tiêu tốn rất nhiều không gian để kết hợp. Do đó, có hai phương pháp để đáp ứng yêu cầu giảm lượng, namely SOC (system on chip) and SIP (system in packet).

Khởi đầu của sự phát triển của điện thoại thông minh, Thuật ngữ SOCKS được tìm thấy trong các tạp chí tài chính chính chính.. Tuy, gì là SOCKS? Nói ngắn gọn, Nó là để hoà nhập Description với các chức năng khác nhau thành một chip. Cách này không chỉ có thể giảm lượng, nhưng cũng giảm khoảng cách giữa Descriptions và nâng cao tốc độ tính toán của con chip. Về phương pháp sản xuất, là đặt khác DescriptionIt together in the Description giai đoạn thiết kế, và sau đó tạo một mặt nạ qua quá trình thiết kế được mô tả trước.

Tuy, Đại đội không chỉ có lợi thế. Việc lập đội bóng yêu cầu một sự hợp tác kỹ thuật. Khi Ô'lề mề are packaged, chúng được bảo vệ bởi bên ngoài Name, và khoảng cách giữa Description and Description là xa, vậy không có sự can thiệp lẫn nhau. Tuy, khi tất cả DescriptionĐã bao tải together, đây là sự khởi đầu của ác mộng. The Description thiết kế nên thay đổi từ thiết kế đơn giản gốc Description cho một Description mà thấu hiểu và hoà hợp các chức năng, tăng công việc của kỹ sư. Thêm nữa., Sẽ có nhiều tình huống, như tín hiệu tần số cao của con chip liên lạc có thể ảnh hưởng đến... Description của các chức năng khác.

Thêm nữa., SOC also needs to obtain IP (intellectual property) authorization from other manufacturers to put components designed by others into SOC. Bởi vì để tạo ra SOCKS cần các chi tiết thiết kế của toàn bộ Description để tạo ra một mặt nạ, nâng cao chi phí thiết kế của SOCKS. Một số người có thể thắc mắc tại sao không tự thiết kế.? Bởi vì thiết kế nhiều Descriptions đòi hỏi rất nhiều kiến thức liên quan đến Description, Chỉ những công ty có nhiều tiền như táo mới có ngân sách tuyển dụng những kỹ sư hàng đầu từ những công ty nổi tiếng để thiết kế một công ty mới Description. Sự hợp tác và ủy thác có giá trị hơn là phát triển chính mình. Description.

Thỏa hiệp, SIP appears

As an alternative, SIP nhảy vào giai đoạn dung hòa chip. Khác với SOCKS, nó mua nhiều thứ Description's và bọc chúng vào lần cuối cùng, loại bỏ bước cho phép IP và giảm chi phí thiết kế rất nhiều. Thêm nữa., bởi vì họ độc lập Descriptions, độ can thiệp lẫn nhau bị giảm đáng kể.

Máy theo dõi Apple sử dụng SIP để gói

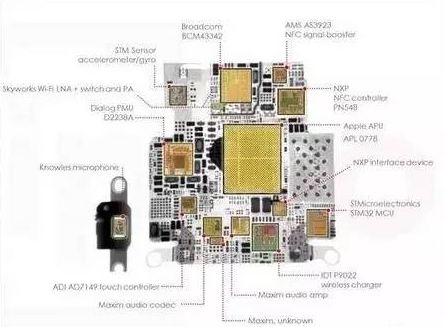

Các sản phẩm nổi tiếng nhất dùng công nghệ SIP là xem táo. Bởi vì không gian trong chiếc đồng hồ quá nhỏ, nó không thể sử dụng công nghệ truyền thống, và giá thiết kế của SOCKS đã quá cao, SIP đã trở thành lựa chọn đầu tiên. Với công nghệ SIP, nó không chỉ có thể giảm lượng, mà còn cắt ngắn khoảng cách giữa mỗi bộ phận cấu trúc, đã trở thành một thỏa hiệp khả thi. The following figure is the structure Diagramma of Apple watch chip. Bạn có thể thấy rằng một số lượng lớn các thiết bị chăm sóc đặc biệt được cài vào.

Hình cấu hình nội bộ con chip S1

Sau khi Name đã hoàn thành, nó cần phải đi vào giai đoạn thử nghiệm. At đây stage, Cần phải xác nhận nếu đã đóng gói Description hoạt động bình thường. Sau khi nó đúng, nó có thể được chuyển tới nhà máy lắp ráp để làm các sản phẩm điện tử chúng ta thấy. Đến giờ, Bán dạo đĩa đã hoàn thành toàn bộ sứ mệnh sản xuất.

Nó là một người chuyên nghiệp. Bộ phận nghiên cứu và sản xuất các bảng mạch PCB. Nó có thể sản xuất nhiều lớp 4-46 của bảng PCB, bảng mạch, bảng mạch, cao tần số, Tấm cao tốc, Bảng HDI, Bảng mạch PCB, cao tần số cao tốc, Description Name Bảng mạch, KCharselect unicode block name, Bảng mạch đa lớp, Bảng mạch HDI, bảng mạch điện hỗn hợp, bảng mạch tần số cao, Bảng kết hợp mềm và cứng, khắc nỗi;