L. Phủ lên Comment đệm

1.1. Để đè lên các lớp đệm dán (ngoại trừ các lớp đệm lót lót tạo bề mặt) có nghĩa là các lỗ bao chéo, có thể dẫn tới việc vỡ mảnh khoan và tổn thương các lỗ trên các lỗ trong suốt quá trình khoan khoan do khoan nhiều lần tại một nơi.

1.2. Hai lỗ trên tấm lưới đa lớp bị đè lên, ví dụ, một lỗ là cái đĩa bị gián và lỗ khác là cái đĩa nối (đĩa đính hoa). Kết quả là, kết quả âm tính là đĩa đệm, dẫn đến các mảnh vụn.

2. Lạm dụng Lớp đồ họa

2.1. Một số kết nối vô dụng đã được thực hiện trên một số lớp đồ họa, nhưng những dòng có hơn năm lớp đã được thiết kế thay vì bốn lớp, gây ra sự hiểu sai.

Sơ đồ thời gian thiết kế là dễ. Lấy phần mềm protein làm ví dụ, vẽ các đường với lớp trên để mỗi lớp, và đánh dấu các đường với lớp trên. Trong dữ liệu vẽ ánh s áng, khi lớp vẽ trên bảng không được chọn, đường sẽ bị cắt và cắt, hoặc đường sẽ bị ngắt kết nối, bởi vì đường làm dấu hiệu của lớp đồ thị được chọn, nên độ nguyên vẹn và độ sáng của lớp đồ họa được duy trì trong thời gian thiết kế.

2.3. Thật bất tiện khi vi phạm những thiết kế thông thường, như là thiết kế của bề mặt thành phần ở dưới lớp và thiết kế của bề mặt hàn ở trên.

Ba. Rối loạn ký tự

Ba

3.2. Thiết kế ký tự quá nhỏ để làm cho việc in màn hình khó và quá lớn để chồng chéo các ký tự, làm cho khó phân biệt.

4. Cài đặt độ mở của màn mối hàn một mặt

4.1. Má đơn mặt không khoan lỗ. Nếu các lỗ cần được đánh dấu, kích cỡ lỗ phải được thiết kế bằng không. Nếu tính số được thiết kế, tọa độ của lỗ sẽ xuất hiện ở vị trí này và vấn đề sẽ xảy ra khi dữ liệu khoan tạo ra.

4.2. Làm hàm đặc biệt cho những lớp đệm đính đơn, như là khoan lỗ.

5. Vẽ đệm để kết nối với các khối đệm

Các tấm đệm vẽ với các khối lấp răng có thể vượt qua kiểm tra Congo trong thiết kế của mạch nhưng không thể xử lý được. Vì vậy, các Má không thể tạo trực tiếp dữ liệu kháng cự. Khi dùng bề mặt trên, khu vực khối lấp răng sẽ được yểm trợ bởi chỗ lắp, điều đó làm cho thiết bị khó lắp ráp.

6. The Electric stratum is flower binding pad and connection

Bởi vì nguồn năng lượng được thiết kế như một bảng làm mẫu, cục diện đối lập với hình ảnh trên bảng mạch thật sự in, và mọi kết nối đều là đường tách biệt, mà thiết kế nên rất rõ ràng. Nhân tiện, phải cẩn thận khi thiết lập nguồn điện hay các đường dây cách ly ở nhiều nơi. Không còn khoảng trống để ngắt kết nối hai bộ nguồn điện hay chặn vùng kết nối (để tách một bộ nguồn cung cấp năng lượng).

7. Hình phủ định cấp xử lý

7.1. Tấm đơn được thiết kế trên lớp TOP. Nếu không xác định ngược và trước, tấm ván có thể được làm với các thành phần và không được hàn kỹ lưỡng.

7.2. Ví dụ, một tấm ván bốn lớp được thiết kế với bốn lớp đáy của TOP mid1 và mid2, nhưng nó không được xếp theo thứ tự này trong suốt quá trình xử lý, yêu cầu chỉ dẫn.

8. Quá nhiều những khối lấp đầy trong thiết kế hoặc những đường rất mỏng để lấp đầy các khối lấp đầy.

8.1. Mất dữ liệu vẽ ánh sáng và dữ liệu vẽ đèn chưa hoàn tất.

8.2. Bởi vì các khối điền được vẽ từng phần một trong việc xử lý dữ liệu vẽ ánh sáng, lượng dữ liệu vẽ được tạo ra là khá lớn, làm cho việc xử lý dữ liệu khó xử lý.

9. Mảnh đất nối của thiết bị lắp ráp bề mặt quá ngắn.

Cái này để thử nghiệm. Với thiết bị trên bề mặt quá dày, khoảng cách giữa chân rất nhỏ và miếng đệm rất mỏng. Để đặt cái chốt thử, nó phải nằm ở một vị trí bay ngược (trái- phải) bị lệch, như kiểu thiết kế đệm quá ngắn, không ảnh hưởng đến thiết bị lắp đặt, nhưng sẽ không làm cái chốt thử bị đặt sai vị trí.

Mười. Khoảng cách giữa lưới lớn là quá nhỏ.

Những cạnh giữa các đường dây tạo ra một vùng kẹt nhỏ quá (ít hơn 0.3mm). Trong quá trình làm bảng mạch in, quá trình chuyển đổi đồ họa dễ dàng sản xuất ra rất nhiều lớp màng vỡ được gắn vào bảng sau khi phát triển, dẫn đến việc ngắt đường.

11. Mảnh giấy đồng rộng lớn quá gần khung ngoài.

Một vùng lớn của giấy đồng phải tránh xa bên ngoài ít nhất 0.2mm bởi vì khi nặn hình dạng, như giấy đồng, rất dễ làm tan sợi đồng và gây ra vấn đề thay đổi thay đổi.

Độ dài hình dạng

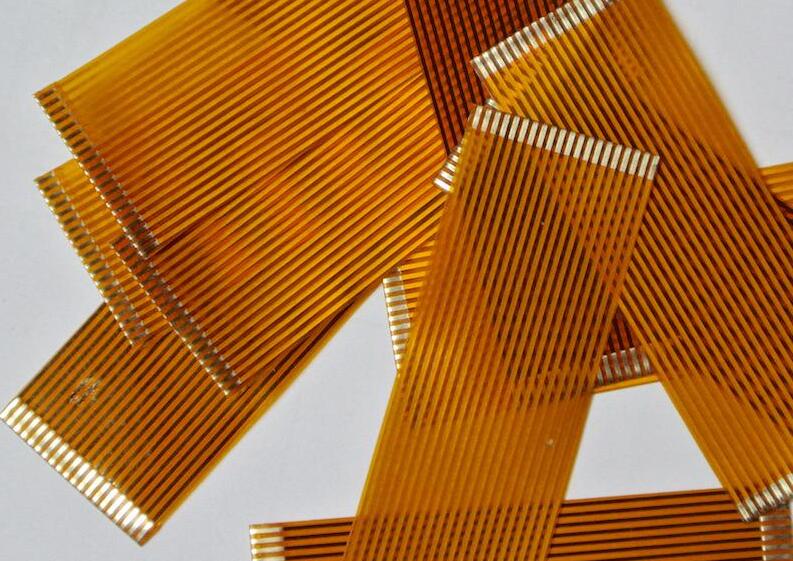

Một số khách hàng đã thiết kế hồ sơ trong lớp Keep, Lớp trên, Lớp trên trên, Comment. và các hồ sơ này không trùng khớp, Điều đó gây khó khăn cho... Sản xuất Bảng mạch mềm to determine which profile line to use.

Nội dung

Lớp phủ không phẳng do lớp điện quang biểu đồ ảnh hưởng đến chất lượng.

Dùng đường viền khi khu bằng đồng bốn lớp quá rộng để tránh bị phỏng khi xử lí các vá SMT.