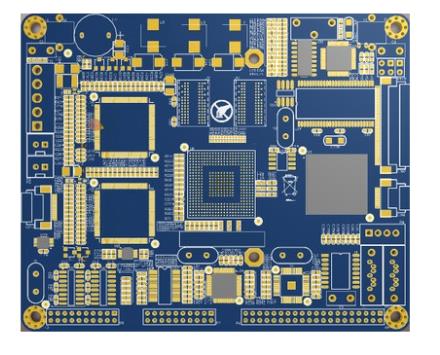

1. Bố cục tổng thể của bảng mạch in và bố trí thiết bị 1) Cho dù một sản phẩm có thành công hay không, một sản phẩm phải chú ý đến chất lượng bên trong và một sản phẩm khác phải xem xét vẻ đẹp tổng thể. Một sản phẩm chỉ có thể được coi là thành công khi cả hai đều hoàn hảo. Trên bảng PCB, các yêu cầu bố trí của các thành phần phải được cân bằng và thưa thớt. Dày đặc có thứ tự, không nặng đầu nhẹ, qua lỗ càng ít càng tốt. Hình dạng của bảng mạch là hình chữ nhật. Tỷ lệ khung hình là 3: 2 hoặc 4: 3; Độ ồn của bảng 4 lớp thấp hơn 20dB so với bảng 2 lớp. Tiếng ồn của bảng 6 lớp thấp hơn 10dB so với bảng 4 lớp. Trong điều kiện kinh tế cho phép, cố gắng sử dụng bảng nhiều lớp. 2) Bảng mạch thường được chia thành khu vực mạch tương tự (sợ nhiễu), khu vực mạch kỹ thuật số (sợ nhiễu, nhiễu), khu vực ổ đĩa điện (nguồn gây nhiễu), vì vậy bảng nên được chia thành ba khu vực một cách hợp lý. 3) thiết bị thường chọn thiết bị tiêu thụ điện năng thấp, ổn định tốt và sử dụng thiết bị tốc độ cao ít nhất có thể. 4) đường dây tinh tế: đường dây rộng có thể được thực hiện không mỏng; Các đường cao áp và tần số cao phải trơn tru, không có góc vát sắc nét và không sử dụng góc vuông ở các góc. Dây nối đất nên càng rộng càng tốt và sử dụng một khu vực rộng lớn của đồng, giúp cải thiện đáng kể các vấn đề về điểm kết nối. 5) Đồng hồ bên ngoài là một nguồn tiếng ồn tần số cao không chỉ gây nhiễu cho hệ thống ứng dụng mà còn có thể gây nhiễu cho thế giới bên ngoài, khiến việc phát hiện khả năng tương thích điện từ không đạt tiêu chuẩn. Trong các hệ thống ứng dụng có yêu cầu cao về độ tin cậy của hệ thống, việc lựa chọn chip đơn tần số thấp là một trong những nguyên tắc giảm tiếng ồn của hệ thống. Trong những năm gần đây, một số nhà sản xuất vi điều khiển tương thích 8051 cũng đã áp dụng một số công nghệ mới để giảm nhu cầu về đồng hồ bên ngoài xuống còn 1/3 so với ban đầu mà không làm giảm tốc độ tính toán. Công nghệ vòng khóa pha bên trong được sử dụng rộng rãi trong vi điều khiển 32 bit, nó làm giảm tần số xung nhịp bên ngoài xuống 32KHz, trong khi tốc độ bus bên trong tăng lên 8MHz hoặc thậm chí cao hơn. 6) Hệ thống cáp phải có hướng hợp lý: chẳng hạn như đầu vào/đầu ra, AC/DC, tín hiệu mạnh/yếu, tần số cao/thấp, áp suất cao/thấp, v.v., hướng của nó phải là tuyến tính (hoặc tách biệt) và không được trộn lẫn với nhau. Mục đích là để ngăn chặn sự can thiệp lẫn nhau. Xu hướng là một đường thẳng, nhưng thường không dễ dàng đạt được và xu hướng bất lợi là theo chu kỳ. Yêu cầu thiết kế cho DC, tín hiệu nhỏ, bảng mạch PCB điện áp thấp có thể thấp hơn. "Hợp lý" là tương đối. Hướng cáp giữa các lớp trên và dưới về cơ bản là thẳng đứng. Toàn bộ bảng không muốn đồng nhất và những gì có thể được ép không nên được ép lại với nhau.7) Về mặt sắp xếp thiết bị, giống như các mạch logic khác, các thiết bị liên quan nên càng gần càng tốt để có được khả năng chống ồn tốt hơn. Đầu vào đồng hồ của bộ tạo đồng hồ, bộ dao động tinh thể và CPU dễ gây nhiễu, vì vậy chúng nên ở gần nhau, đặc biệt là không chạy đường tín hiệu dưới bộ dao động tinh thể. Các thiết bị dễ tạo ra tiếng ồn, mạch hiện tại thấp và mạch hiện tại cao nên tránh xa các mạch logic càng xa càng tốt. Nếu có thể, một bảng mạch khác nên được thực hiện.

2. Công nghệ dây mặt đất Quy định an toàn SkE và mạng tương thích điện từ 1) Mạch analog và mạch kỹ thuật số có nhiều điểm tương đồng và khác biệt trong thiết kế và phương pháp định tuyến của sơ đồ bố trí thành phần. Trong mạch analog, điện áp nhiễu cực nhỏ được tạo ra bởi hệ thống dây dẫn có thể gây ra sự biến dạng nghiêm trọng của tín hiệu đầu ra do sự hiện diện của bộ khuếch đại. Trong mạch kỹ thuật số, dung lượng tiếng ồn TTL là 0,4V~0,6V, dung lượng tiếng ồn CMOS là 0,3Vcc~ 0,45 lần, vì vậy mạch kỹ thuật số có khả năng chống nhiễu mạnh. Việc lựa chọn hợp lý nguồn điện tốt và phương pháp thanh cái nối đất là một đảm bảo quan trọng cho hoạt động đáng tin cậy của thiết bị. Nguồn điện và thanh cái mặt đất tạo ra một số lượng đáng kể các nguồn gây nhiễu, trong đó nhiễu tiếng ồn do dây mặt đất gây ra. 2) Mặt đất kỹ thuật số được tách ra (hoặc một điểm nối đất) từ mặt đất tương tự và dây mặt đất được mở rộng. Chiều rộng dây phải được xác định theo dòng điện. Nói chung, dày hơn là tốt hơn (một dây 100 mm đi qua khoảng 1 đến 2A). Dây nối đất>Dây nguồn>Dây tín hiệu là một phương pháp hợp lý để lựa chọn chiều rộng dây dẫn. 3) Dây nguồn và dây nối đất nên càng gần càng tốt, nguồn điện và mặt đất trên toàn bộ bảng in phải được phân phối theo hình dạng "giếng" để dòng điện được phân phối có thể được cân bằng. 4) Để giảm nhiễu xuyên âm giữa các đường dây, nếu cần thiết, bạn có thể tăng khoảng cách giữa các dây in và đặt một số đường dây zero-volt trong đó làm cách ly giữa các đường dây. Đặc biệt là giữa tín hiệu đầu vào và đầu ra, ba kỹ thuật tách rời, lọc và cách ly a tách rời, lọc và cách ly là ba biện pháp phổ biến để chống nhiễu phần cứng. b Đầu vào nguồn cung cấp kết nối với tụ điện điện phân 10~100uf. Nếu có thể, tốt nhất là kết nối trên 100 uF; Về nguyên tắc, mỗi chip IC nên có một tụ gốm 0,01pF. Nhưng tụ điện; Đối với các thiết bị có khả năng chống ồn kém và thay đổi công suất lớn khi tắt, chẳng hạn như thiết bị lưu trữ RAM và ROM, một tụ điện tách rời nên được kết nối trực tiếp giữa dây nguồn và dây mặt đất của chip; Bộ lọc c đề cập đến việc phân loại các loại tín hiệu khác nhau và kiểm soát hướng của chúng theo đặc tính tần số của chúng. Thường dùng có các loại bộ lọc thông thấp, bộ lọc thông cao, bộ lọc băng thông. Sử dụng bộ lọc thông thấp trên dây nguồn AC được giới thiệu để cho phép 50 tuần nguồn AC đi qua trơn tru và đưa tiếng ồn tần số cao khác xuống mặt đất. Chỉ số cấu hình cho bộ lọc low-pass là mất chèn. Mất chèn bộ lọc thông thấp được chọn quá thấp để ngăn chặn tiếng ồn, mất chèn cao sẽ gây ra "rò rỉ" ảnh hưởng đến an toàn cá nhân của hệ thống. Bộ lọc High Pass và Band Pass nên được lựa chọn và sử dụng theo yêu cầu xử lý tín hiệu trong hệ thống. d Cách ly tín hiệu điển hình là cách ly quang học. Sử dụng thiết bị cách ly quang điện để cách ly đầu vào và đầu ra của chip đơn, một mặt tín hiệu gây nhiễu không thể đi vào hệ thống chip đơn, mặt khác, tiếng ồn của hệ thống chip đơn sẽ không được truyền qua dẫn. Lá chắn được sử dụng để cô lập bức xạ không gian. Đối với các bộ phận có tiếng ồn đặc biệt lớn, chẳng hạn như nguồn chuyển mạch, được bao phủ bởi hộp kim loại, có thể giảm nhiễu từ nguồn tiếng ồn đối với hệ thống chip đơn. Đối với các mạch analog đặc biệt sợ nhiễu, chẳng hạn như các mạch khuếch đại tín hiệu yếu có độ nhạy cao, chúng có thể được che chắn. Điều quan trọng là bản thân lá chắn kim loại phải được kết nối với các quy định an toàn SkE nối đất thực và mạng tương thích điện từ trên bo mạch PCB.