1 Giới thiệu

Quá trình SMT sử dụng hàn hoặc dán để tạo thành các kết nối cơ học và điện giữa các yếu tố và bảng PCB. Ưu điểm chính của nó là kích thước nhỏ, trọng lượng nhẹ và khả năng kết nối tốt; Mạch tần số cao có hiệu suất tốt và trở kháng ký sinh. giảm đáng kể; Hiệu suất chống sốc và rung tốt. Khi sử dụng quy trình SMT, dây dẫn không cần phải đi qua bảng, điều này có thể tránh việc nhận dây dẫn hoặc tạo tín hiệu bức xạ, do đó cải thiện tỷ lệ tín hiệu nhiễu của mạch. Để đánh giá hiệu suất của quá trình SMT, trước hết, các mối hàn phải được hình thành đúng cách; Tiền đề của sự hình thành chính xác là kích thước của miếng đệm của các thành phần trên bảng PCB phải được thiết kế hợp lý; Thứ hai, trong quá trình bố trí bảng PCB, mật độ của các thành phần nên được sắp xếp hợp lý, Để đáp ứng các yêu cầu của điểm kiểm tra. Khi thực hiện thiết kế bảng mạch, nó được thực hiện thông qua DFM (Manufacturing Design). DFM là một phần quan trọng của các công nghệ quan trọng trong kỹ thuật song song. Nó bắt đầu với thiết kế sản phẩm, xem xét khả năng sản xuất và khả năng phát hiện và là một công cụ hiệu quả để thiết kế bảng mạch từ thiết kế đến sản xuất thành công.

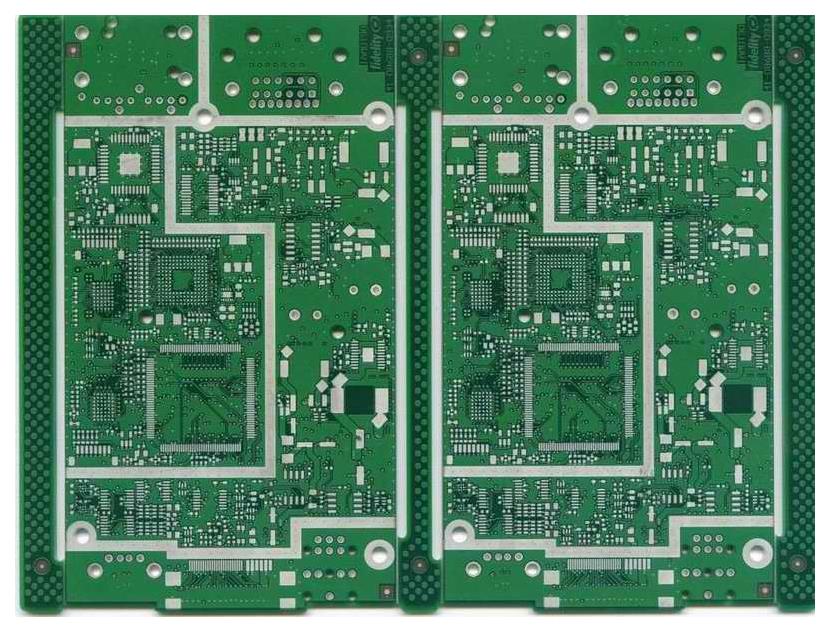

2. Lựa chọn vật liệu bảng PCB

Có hai loại chính của chất nền bảng mạch in: vật liệu chất nền hữu cơ và vật liệu chất nền vô cơ, trong đó vật liệu chất nền hữu cơ được sử dụng phổ biến nhất. Các bo mạch PCB được sử dụng cũng khác nhau cho các lớp khác nhau. Ví dụ, vật liệu composite đúc sẵn được sử dụng cho các tấm 3 đến 4 lớp và epoxy thủy tinh chủ yếu được sử dụng cho các tấm đôi. Trong quá trình lắp ráp điện tử không chì, mức độ uốn cong của bảng mạch in khi nung nóng tăng lên do nhiệt độ tăng. Do đó, trong SMT, cần phải sử dụng các tấm có độ cong nhỏ hơn, chẳng hạn như FR-4 và các loại chất nền khác. Sau khi chất nền được làm nóng, các điện cực sẽ bị tước và độ tin cậy sẽ giảm do tác động của căng thẳng mở rộng và co lại trên các thành phần. Do đó, cần chú ý đến hệ số giãn nở vật liệu khi lựa chọn vật liệu, đặc biệt là khi các thành viên lớn hơn 3,2a 1,6mm. Các tấm PCB được sử dụng trong công nghệ lắp ráp bề mặt đòi hỏi độ dẫn nhiệt cao, khả năng chịu nhiệt tuyệt vời (150, 60 phút) và khả năng hàn (260, 10 giây), độ bền liên kết lá đồng cao (trên 1,5 Pa) và độ bền uốn (25 Pa), độ dẫn điện cao và hằng số điện môi nhỏ, độ chính xác tốt (chính xác ± 0,02 mm) và khả năng tương thích với chất tẩy rửa, ngoài ra, yêu cầu phải có vẻ mịn và bằng phẳng, không bị cong vênh, nứt, sẹo và rỉ sét. Độ dày của bảng mạch in là 0.5mm, 0.7mm, 0.8mm, 1mm, 1.5mm, 1.6mm, (1.8mm), 2.7mm, (3.0mm), 3.2mm, 4.0mm, 6.4mm, trong đó bảng mạch PCB với độ dày 0.7mm và 1.5mm được sử dụng để thiết kế bảng điều khiển đôi ngón tay vàng, 1.8mm và 3.0mm là kích thước phi tiêu chuẩn. Từ quan điểm sản xuất, kích thước của bảng mạch in không được nhỏ hơn 2500mm, kích thước lý tưởng thường là (250~350mm) Ø (2000mm). Sử dụng Puzzle Công nghệ lắp ráp bề mặt quy định lượng uốn cong của chất nền có độ dày 1,6mm là 0,5mm trên và 1,2mm dưới. Thông thường, tỷ lệ uốn cho phép là dưới 0,065%.

3. PCB board overhole và bố trí phần tử

3.1 Bố trí quá lỗ

1) Tránh đặt overhole trong vòng 0,6mm hoặc trong vòng 0,6mm trên bề mặt gắn pad.

2) Không có lỗ thông qua (nghĩa là không có lỗ mở bên dưới phần tử; tắc nghẽn màng hàn có thể được loại trừ) giữa các miếng vá linh kiện không có chân bên ngoài (chẳng hạn như tụ điện trở chip, tụ điện có thể điều chỉnh, v.v.) để đảm bảo chất lượng làm sạch.

3) Là lỗ thông qua để kiểm tra giá đỡ, khoảng cách giữa các đầu dò đường kính khác nhau trong thử nghiệm trực tuyến tự động cần được xem xét đầy đủ khi thiết kế bố trí.

4) Khoảng cách phù hợp giữa đường kính lỗ thông qua và dây dẫn của phần tử là quá lớn và dễ hàn. Thông thường, đường kính lỗ thông qua lớn hơn 0,05-0,2mm so với đường kính dây dẫn, và khi đường kính tấm là 2,5 đến 3 lần đường kính lỗ thông qua, nó rất dễ dàng để hình thành các điểm hàn đủ điều kiện.

5) Không thể kết nối quá lỗ và pad để tránh mất hàn hoặc cách ly nhiệt. Nếu overhole cần phải được kết nối với pad, nó nên được kết nối với nhau càng nhiều càng tốt bằng dây mỏng (nhỏ hơn 1/2 chiều rộng của pad hoặc 0,3mm~0,4mm), khoảng cách giữa overhole và cạnh của pad lớn hơn 1mm.

3.2 Bố trí thành phần

Khi thực hiện quá trình hàn trở lại, cần chú ý đến các điểm sau theo hướng sắp xếp của các thành phần:

1) Các thành phần trên tấm nên được phân phối càng đồng đều càng tốt (nhiệt và không gian đồng đều);

2) Các bộ phận nên được sắp xếp theo cùng một hướng càng nhiều càng tốt để giảm hiện tượng hàn kém;

3) Khoảng cách giữa các thành phần phải lớn hơn 0,5mm để tránh bù nhiệt độ không đủ;

4) Cần có một số không gian bảo trì và thử nghiệm xung quanh PLCC, SOIC, QFP và các thiết bị lớn khác;

5) Các yếu tố cung cấp điện không nên được tập trung, nên được bố trí riêng biệt trên cạnh của bảng mạch PCB hoặc ở vị trí có tản nhiệt thông gió tốt;

6) Không đặt các bộ phận có giá trị gần các khu vực tập trung căng thẳng cao, chẳng hạn như cạnh, góc hoặc chèn, lỗ gắn, khe cắm, vết cắt bảng điều khiển và khe hở PCB để giảm vết nứt hoặc vết nứt.

3.3 Hướng thành phần

Khi thực hiện quá trình hàn sóng, cần chú ý đến các điểm sau theo hướng sắp xếp của các thành phần:

1) Tất cả các yếu tố thụ động phải song song với nhau;

2) Trục dài của SOIC và các phần tử thụ động phải vuông góc với nhau;

3) Trục dài của phần tử thụ động phải vuông góc với hướng chuyển động của tấm dọc theo băng tải máy hàn sóng;

4) Các thành phần gắn trên bề mặt phân cực nên được đặt càng nhiều càng tốt theo cùng một hướng;

5) Khi hàn các thành phần đa pin như SOIC, miếng đệm ăn cắp hoặc khu vực miếng đệm nên được thêm vào ở cả hai chân theo hướng dòng chảy của hàn để ngăn chặn cầu nối;

6) Các loại thành phần tương tự nên được sắp xếp trên tấm theo cùng một hướng, làm cho các thành phần dễ dàng hơn để đặt, kiểm tra và hàn;

7) Khi sử dụng các quy trình lắp ráp khác nhau, cần xem xét khả năng thích ứng của chân và trọng lượng của phần tử đối với quá trình hàn ngược hoặc hàn sóng để ngăn chặn các bộ phận rơi hoặc hàn. Thiết bị đóng đinh bốn bên.

4. PCB mạch và thiết kế pad

4.1 Yêu cầu thiết kế quy trình mạch

1) Các cạnh kẹp của quá trình bảng mạch in là 5mm.

2) Tránh kết nối dây với miếng đệm ở một góc nhất định và cố gắng làm cho dây thẳng đứng với miếng đệm của phần tử, dây nên được kết nối với miếng đệm từ trung tâm của cạnh dài của miếng đệm.

3) Giảm chiều rộng của dây kết nối với miếng đệm, trừ khi bị giới hạn bởi công suất sạc, giới hạn xử lý và các yếu tố khác, chiều rộng là 0,4mm hoặc một nửa chiều rộng của miếng đệm (tùy theo điều kiện nào nhỏ hơn). Một là để ngăn chặn tản nhiệt quá nhanh và một là để ngăn chặn mặt nạ hàn không đủ chính xác, dẫn đến dòng chảy của hàn, tạo thành hàn kém.

4) Cấu trúc định tuyến bảng mạch in: dấu vết được thực hiện bằng công nghệ khắc thông thường, chiều rộng và khoảng cách dòng là 0,6mm; Các dấu vết mỏng được làm bằng công nghệ khắc đường tốt với chiều rộng đường và khoảng cách 0,3mm; Các dấu vết siêu mịn với chiều rộng đường 0,3mm và khoảng cách 0,15mm.

5) Các phương pháp lắp ráp khác nhau có yêu cầu dây khác nhau. Chiều rộng chì của phương pháp chèn lớn hơn 0,2mm, chiều rộng chì của phương pháp lắp đặt là 0,1 đến 0,2mm, chiều rộng chì lắp ráp khoảng cách tốt là 0,05 đến 0,1mm.

6) Bất cứ khi nào có thể, nên tránh sử dụng các dây kết nối (đặc biệt là các thiết bị pin khoảng cách tốt) giữa các tấm hàn của chúng. Bất kỳ dây kết nối nào đi qua các tấm liền kề phải được che chắn bằng mặt nạ hàn.

7) For multi-pin components (such as S0IC, QFP, etc.), the short connection between the pin pads is not allowed to pass through. Separation can be excluded), so as not to cause displacement or be mistaken for bridging after welding.

8) Khi thiết kế bảng PCB với chip không đóng gói (chip trần), miếng đệm vuông của chip trần phải được nối đất thay vì nổi; Ngoài ra, để đảm bảo sự tham gia đáng tin cậy, miếng đệm phải được mạ vàng đồng đều. Đối với các yếu tố định hướng, chẳng hạn như triode, chip, v.v., cần chú ý đến độ phân cực của chúng khi định tuyến.

4.2 Yêu cầu thiết kế mạch điện

1) Nguyên tắc mà dây đi qua trong khoảng cách giữa các chân: mật độ thấp yêu cầu hai dây có đường kính 0,23mm phải đi qua trong khoảng cách trung tâm của chân 2,54mm; Mật độ trung bình yêu cầu đường kính dây phải đi qua trong khoảng cách trung tâm của pin là 1,27mm. Đó là dây 0,15mm; Mật độ cao đòi hỏi 2 đến 3 dây mỏng hơn trong khoảng cách trung tâm của pin 1,27mm.

2) Chiều rộng của dòng bảng in phải nhất quán nhất có thể, điều này có lợi cho việc kết hợp trở kháng. Trong quá trình sản xuất tấm in, chiều rộng có thể là 0,3mm, 0,2mm và 0,1mm, nhưng khi các đường nét trở nên mỏng hơn và khoảng cách trở nên nhỏ hơn, chất lượng sẽ khó kiểm soát trong quá trình sản xuất. Trừ khi có yêu cầu đặc biệt, nói chung nên áp dụng nguyên tắc dây của chiều rộng đường 0.3mm và khoảng cách đường 0.3mm.

3) Cố gắng sử dụng mạch ngắn, đặc biệt là đối với mạch tín hiệu nhỏ, đường dây càng ngắn, điện trở càng nhỏ, nhiễu càng nhỏ, chiều dài của đường nối nên được rút ngắn càng tốt.

4) Hướng dây của tấm nhiều lớp: Theo lớp nguồn, tách lớp nối và lớp tín hiệu để giảm nhiễu giữa nguồn điện, mặt đất và tín hiệu. Ngoài ra, luật bản quyền dòng yêu cầu các bảng in hai lớp liền kề phải vuông góc với nhau hoặc theo đường chéo và đường cong thay vì đường song song để giảm khớp nối và nhiễu giữa các lớp chất nền.

5) Nguyên tắc thiết kế của dây nguồn và dây mặt đất: diện tích dây càng lớn càng tốt để giảm nhiễu. Đối với đường tín hiệu tần số cao, hãy sử dụng đường mặt đất để che chắn. Lớp điện diện tích lớn và lớp tiếp đất phải liền kề, vai trò của nó là hình thành một tụ điện giữa nguồn điện và mặt đất, đóng vai trò lọc.

4.3 Thiết kế đệm

Kích thước của miếng đệm có ảnh hưởng lớn đến khả năng sản xuất và tuổi thọ của sản phẩm SMT và là một phần cực kỳ quan trọng trong thiết kế mạch PCB. Phát huy tác dụng trọng yếu. Các yêu cầu sản xuất của các thành phần là khác nhau. Thiết kế pad nên được sản xuất theo thông số kỹ thuật của các yếu tố để đảm bảo độ tin cậy của mạch và ngăn ngừa các khuyết tật về tay nghề (như bia mộ và xiên), cho thấy lợi thế của SMT. Trong thiết kế cụ thể, nó cũng phải được thiết kế theo mật độ lắp ráp của sản phẩm cụ thể, quy trình khác nhau, thiết bị khác nhau và yêu cầu của các bộ phận đặc biệt. Hiện tại, không có tiêu chuẩn thống nhất cho các thành phần gắn trên bề mặt. Các quốc gia khác nhau và các nhà sản xuất khác nhau có hình dạng và gói linh kiện khác nhau. Do đó, nó phải phù hợp với hình dạng gói và chân của các thành phần bạn chọn khi thiết kế kích thước của miếng đệm. Đợi đã, xác định chiều dài và chiều rộng của miếng hàn. Thiết kế pad linh kiện thường được sử dụng có thể tham khảo một số tiêu chuẩn, chẳng hạn như IPC-SM-782, IPC-7095, IPC-7525, IEC-TC52 WG6, JIS C-5010 và biên soạn tiêu chuẩn quy trình công nghiệp điện tử.

Dưới đây là một số điều bạn nên làm khi thiết kế đệm:

1) Đối với cùng một thiết bị, đối với miếng đệm được sử dụng đối xứng, tính đối xứng tổng thể nên được duy trì nghiêm ngặt trong thiết kế, tức là hình dạng và kích thước của mẫu miếng đệm phải giống hệt nhau;

2) Đối với cùng một thiết bị, thiết kế pad sử dụng kích thước gói và các thông số số để tính toán kích thước pad để đảm bảo ứng dụng rộng rãi của kết quả thiết kế;

3) Độ tin cậy của mối hàn chủ yếu phụ thuộc vào chiều dài chứ không phải chiều rộng khi thiết kế miếng đệm;

4) Thiết kế của pad nên phù hợp: nếu pad quá lớn, hàn sẽ khuếch tán lớn hơn và các mối hàn hình thành sẽ mỏng hơn; Nếu nó quá nhỏ, thì tấm đồng foil có quá ít sức căng bề mặt đối với chất hàn nóng chảy. Khi sức căng bề mặt của lá đồng nhỏ hơn sức căng bề mặt của hàn nóng chảy. Dưới sức căng, các mối hàn được hình thành là các khớp không ướt;

5) Khi miếng đệm được kết nối với một khu vực dẫn điện lớn (chẳng hạn như nối đất, nguồn điện, v.v.), nên được cách ly nhiệt bằng dây tốt hơn, chiều rộng của dây thường là 0,2 đến 0,4 và chiều dài khoảng 0,6mm.

6) Thiết kế pad trong peak hàn thường lớn hơn so với trong reflow hàn, bởi vì các thành phần trong peak hàn được cố định bằng keo, và pad lớn hơn một chút, sẽ không gây nguy hiểm cho sự dịch chuyển và đứng thẳng của các thành phần, nhưng có thể làm giảm "hiệu ứng bóng của peak hàn". ".

4.4 Mối quan hệ giữa chiều rộng đĩa C (LâW) của các thành viên hình chữ nhật và chiều rộng đầu hàn W của các thành viên là: C=WâS (0,7ï½ 1,3) mm. Đối với các thành viên RC dưới 0805, CâW; Đối với các thành viên RC trên 0805, C=W+0,1~0,25mm. Chiều dài khoảng 0,9mm và khoảng cách giữa các miếng đệm là A=L-0,7mm.

Độ dày thay đổi rất nhiều. Ví dụ, điện trở chỉ bằng khoảng một nửa so với tụ điện. Cần chú ý đến thiết kế của đệm. Đặc biệt đối với các thành viên RC nhỏ, nên xem xét hàn ướt tốt ở phía thiết bị đầu cuối. Hơn nữa, đỉnh và đáy của khu vực hàn cuối của cụm chip hai đầu nguồn không hoàn toàn phù hợp. Đối với một mối hàn đáng tin cậy, cũng cần phải có một đầu nhúng vào hàn. Do đó, cần phải có một pad lớn hơn pad của các thành phần.

4.5 Yếu tố hình trụ

MELF Component Pad Pattern Design Formula: Chiều rộng của pad là C=Dâ (0,7ï½ 1,0) mm=Ímax, chiều dài là S=Lmax- (Lmin-2I), khoảng 1mm và khoảng cách giữa hai pad là A=Lmax-2S=Lmin-2I, khoảng L-1mm. (Thiết kế lý tưởng chỉ xem xét dung sai phần tử, không tính lỗi vị trí.) Trong quá trình sản xuất cụ thể, kích thước nên được phóng to một chút, có tính đến lỗi vị trí phần tử. Khi hàn trở lại, chiều rộng tăng 0,05~0,1mm, chiều dài tăng 0,2~0,3mm; Khi hàn đỉnh, chiều rộng tăng 0,1mm và chiều dài tăng 0,2~0,6mm. Ngoài ra, trong quá trình hàn reflow, mong muốn mở khe hở trong thiết kế tấm hàn, do đó các thành phần có thể được định vị trong quá trình hàn reflow. Kích thước chiều sâu notch F=(Lmax-A)/2, độ sâu notch E là 0,3mm (đối với các thành phần kích thước nhỏ, ví dụ: điện trở 1/8W) và 0,4mm (đối với các thành phần kích thước lớn, ví dụ: điện trở 1/4W). Vì độ dày của lớp đồng (bao gồm cả lớp mạ và lớp kháng) của tấm hàn nói chung sẽ không vượt quá 0,2mm, khoảng cách E không nên quá lớn.

4.6 SOP (dây dẫn cánh), thiết bị đóng gói QFP

Thiết kế đệm cho loại thiết bị này không có công thức tính toán tiêu chuẩn, điều này tương đối khó khăn. Chiều rộng của miếng C phải bằng (hoặc lớn hơn một chút/nhỏ hơn) chiều rộng của đầu hàn (hoặc pin), thường là C=W+0,1mm. Chiều dài của miếng đệm thường là 2,0 ± 0,5mm, thường là B=T+b1+b2, trong đó b1=0,45 ± 0,6mm, có lợi cho các mối hàn có đường viền mặt trăng cong tốt khi hàn tan chảy và cũng có thể tránh hàn một cách hiệu quả. Các khuyết tật cầu tồn tại đúng cách và xem xét độ lệch vị trí của các thành phần; b2=0,25~1,5mm, chủ yếu là để đảm bảo rằng các mối hàn có thể hình thành hình dạng mặt trăng cong, (nó cũng nên được xem xét cho SOIC, QFP và các thiết bị khác. Đối với các thiết bị SOIC và QFP, chiều dài của miếng đệm là B=T+(0,6~0,8) mm, khoảng cách giữa các trung tâm của miếng đệm bằng với khoảng cách của chính chip và khoảng cách giữa các miếng đệm bằng (hoặc hơi nhỏ) khoảng cách giữa các dây dẫn. Đối với các chip IC như SO và SOJ có khoảng cách pin lớn hơn 1,27mm, chiều rộng của miếng đệm là Câ1,2W, khoảng cách pin từ 0,65 đến 1,27 và độ dày của miếng đệm là CâW, thường là C=W+0,1~0,25mm; Đối với chip IC tối đa 0,65mm (bao gồm cả khoảng cách pin 0,65mm), chiều rộng của miếng đệm phải bằng chiều rộng pin. Chiều rộng của miếng đệm QFP phải bằng chiều rộng của pin, C=W+0,1mm; Đối với QFP khoảng cách tốt, đôi khi nên giảm chiều rộng của miếng đệm một cách thích hợp, chẳng hạn như khi có một dây dẫn đi qua giữa hai miếng đệm. Chiều dài của tấm B=L+(0,6~1,0) mm và khoảng cách của tấm A=Fï¼ 0,25 mm.

Đồng thời, miếng đệm dài hơn làm tăng sức căng bề mặt giữa dán và miếng đệm, có lợi cho việc giải phóng dán và mang lại sự tiện lợi cho quá trình in dán. Nó cũng đã được chứng minh trong các ứng dụng thực tế rằng các khu vực giao thoa tồn tại ở phía trước và phía sau của dây dẫn trên đĩa hàn, rất có lợi cho lượng hàn dư thừa, do đó làm giảm nguy cơ cầu nối sau hàn.

4.7 Bóng bán dẫn (SOT)

Mối quan hệ giữa chiều rộng của tấm hàn C và chiều rộng của dây dẫn phần tử W là: C ¥ W; Chiều dài của tấm hàn=chiều dài chì của phần tử+b1+b2, trong đó b1=b2=0,3~0,5mm; Khoảng cách giữa các tấm được đảm bảo bằng khoảng cách trung tâm của dây dẫn. Trên cơ sở này, bốn cạnh của mỗi tấm được kéo dài ít nhất 0,35mm.

4.8 Thiết bị SOJ, PLCC (chân J)

Nguyên tắc thiết kế đệm: (0,5½ 0,8mm) (1,85½ 0,15mm); Trung tâm của pin nên nằm giữa 1/3 bên trong của mẫu pad và trung tâm của pad; Khoảng cách giữa hai hàng miếng đệm cho SOJ thường là 4,9mm.

4.9 BGA Pad thiết kế và trống Pad

BGA pad có hình dạng tròn với đường kính 80% đường kính của quả bóng. Kích thước số liệu được sử dụng trong thiết kế vì các bộ phận được sản xuất theo hệ mét, trong khi thiết kế theo hệ Anh dẫn đến độ lệch vị trí. Với các yếu tố quy trình lắp ráp, đôi khi một miếng đệm trống được thiết kế bên dưới cụm chip hai đầu cuối. Nó không được sử dụng để hàn, nó được sử dụng để hàn sóng, vì vậy nó được gọi là mẫu rối. Mô hình này làm cho keo dễ dàng dính vào các thành phần để các thành phần không bị dính vì bề mặt keo quá thấp.

5. Yêu cầu sản xuất đánh dấu điểm chuẩn

1) Các đồ họa thường được sử dụng cho các điểm cơ sở là hình vuông, hình tròn, hình tam giác và hình chữ thập. Đường kính của điểm cơ sở lần lượt là 0,5mm và 3mm. Thông thường, 2 đến 3 vòng tròn rắn có đường kính 1 mm được đặt trên đường chéo của tấm làm dấu tham chiếu. Nếu đó là một câu đố, thì mỗi câu đố nên được thiết kế một dấu chuẩn;

2) Kích thước của các dấu hiệu trên cùng một tấm gỗ phải giống nhau và các biến thể không được vượt quá 25 ° m;

3) Điểm tham chiếu có thể là đồng trần hoặc mạ niken, mạ thiếc và hàn (HASL, độ dày 7-10 angstrom). Độ dày của lớp phủ là 5 đến 10 angstrom, không quá 25 angstrom, độ phẳng bề mặt của điểm tham chiếu phải trong vòng 15 angstrom;

4) Điểm cơ sở phải cách cạnh của bảng in ít nhất 5 mm. Đối với các tấm có hình dạng không đều, cần thêm cạnh 5mm. Đặt trên đường chéo của bảng và cụm, không nên có các tính năng mạch khác xung quanh điểm tham chiếu, kích thước của khu vực mở bằng đường kính của điểm đánh dấu;

5) Trục cưa có thể áp dụng công nghệ tách tấm dập, cũng có thể áp dụng công nghệ tách rãnh chữ V khắc hai mặt. Độ sâu của rãnh chữ V được kiểm soát trong vòng 1/6 đến 1/8 độ dày của tấm, và chiều dài được kiểm soát trong vòng 1/3 bên; Đối với bảng mạch PCB không có hàn sóng, mặt trước và mặt sau của bảng số kép có thể được sử dụng trên một nửa và các mẫu ở cả hai bên có thể được sắp xếp theo cùng một cách để cải thiện việc sử dụng thiết bị