Bài viết này bắt đầu với cách bố trí bảng mạch PCB cơ bản thảo luận về vai trò và kỹ thuật thiết kế của bảng mạch PCB xếp chồng lên nhau để kiểm soát bức xạ EMI. Có rất nhiều cách để giải quyết vấn đề EMI. Các phương pháp ức chế EMI hiện đại bao gồm: sử dụng lớp phủ ức chế EMI, chọn phụ tùng ức chế EMI phù hợp và thiết kế mô phỏng EMI.

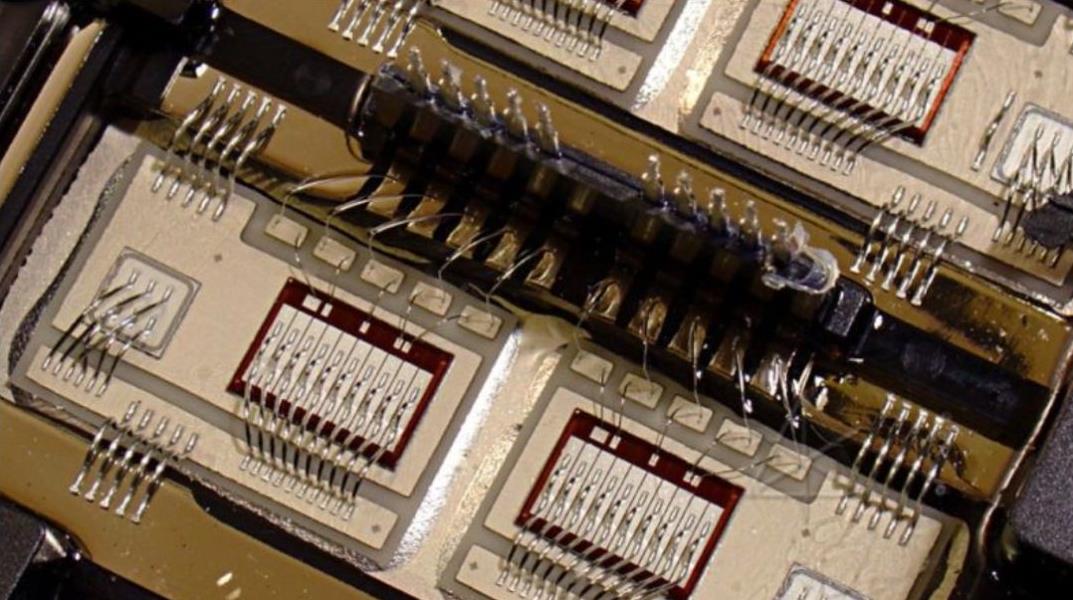

Xe buýt điện

Vị trí hợp lý của tụ điện với công suất thích hợp gần chân nguồn của mạch tích hợp có thể làm cho điện áp đầu ra của mạch tích hợp thay đổi nhanh chóng. Tuy nhiên, vấn đề không kết thúc ở đó. Vì các tụ điện có phản ứng tần số hạn chế, điều này ngăn chúng tạo ra công suất hài hòa cần thiết cho đầu ra IC điều khiển sạch trên toàn băng tần. Ngoài ra, điện áp thoáng qua được tạo ra trên thanh cái nguồn sẽ tạo ra sự sụt giảm điện áp trên các đường dẫn tách biệt, là nguồn gây nhiễu EMI chính ở chế độ chung. Chúng ta nên giải quyết những vấn đề này như thế nào? Trong trường hợp IC trên bảng của chúng tôi, mặt phẳng nguồn xung quanh IC có thể được coi là một tụ điện tần số cao tốt, thu thập năng lượng rò rỉ từ các tụ điện rời rạc cung cấp năng lượng tần số cao cho đầu ra sạch. Ngoài ra, một lớp năng lượng tốt nên có điện cảm nhỏ hơn sao cho tín hiệu thoáng qua được tổng hợp từ điện cảm cũng nhỏ hơn, do đó làm giảm EMI chế độ chung. Tất nhiên, kết nối từ lớp nguồn đến chân nguồn IC phải càng ngắn càng tốt vì tín hiệu kỹ thuật số tăng nhanh hơn và nhanh hơn dọc theo và nó được kết nối trực tiếp với miếng đệm nơi chân nguồn IC được đặt, điều này sẽ được thảo luận riêng.

Để điều khiển EMI chế độ chung, máy bay công suất phải là một cặp máy bay công suất được thiết kế hợp lý để tạo điều kiện tách rời và có độ tự cảm đủ thấp. Nó tốt như thế nào, một số người có thể hỏi? Câu trả lời cho câu hỏi này phụ thuộc vào sự phân tầng của nguồn điện, vật liệu giữa các lớp và tần suất hoạt động (tức là chức năng của thời gian tăng IC). Thông thường, khoảng cách giữa các lớp công suất là 6 triệu, vật liệu FR4 và điện dung tương đương của lớp công suất là khoảng 75 pF trên mỗi inch vuông. Rõ ràng, khoảng cách giữa các lớp càng nhỏ, điện dung càng lớn. Không có nhiều thiết bị có thời gian tăng từ 100 đến 300ps, nhưng với tốc độ phát triển hiện tại của IC, các thiết bị có thời gian tăng từ 100 đến 300ps sẽ chiếm một tỷ lệ đáng kể. Đối với các mạch có thời gian tăng từ 100 đến 300ps, khoảng cách lớp 3mil sẽ không còn phù hợp với hầu hết các ứng dụng. Vào thời điểm đó, cần phải sử dụng kỹ thuật phân lớp với khoảng cách giữa các lớp nhỏ hơn 1 mils và thay thế vật liệu điện môi FR4 bằng vật liệu có hằng số điện môi rất cao. Giờ đây, gốm sứ và gốm sứ có thể đáp ứng các yêu cầu thiết kế của mạch thời gian tăng từ 100 đến 300ps. Mặc dù các vật liệu và phương pháp mới có thể được áp dụng trong tương lai, thường đủ để xử lý sóng hài cao cấp và duy trì trạng thái thoáng qua đủ thấp cho các mạch thời gian tăng từ 1 đến 3ns phổ biến hiện nay, khoảng cách giữa các lớp 3 đến 6mil và vật liệu điện môi FR4, có nghĩa là EMI chế độ chung có thể được giảm xuống rất thấp. Ví dụ về thiết kế xếp chồng bảng mạch PCB được đưa ra trong bài viết này sẽ giả định khoảng cách giữa các lớp từ 3 đến 6 mils.

Bảo vệ điện từ

Một chiến lược phân lớp tốt từ quan điểm định tuyến tín hiệu nên là đặt tất cả các dấu vết tín hiệu trên một hoặc nhiều lớp bên cạnh mặt phẳng nguồn hoặc mặt đất. Đối với điện, một chiến lược phân tầng tốt nên là tầng điện liền kề với tầng mặt đất và khoảng cách giữa tầng điện và tầng mặt đất càng nhỏ càng tốt, đó là những gì chúng ta gọi là chiến lược phân tầng.

Bảng mạch PCB

Chiến lược xếp chồng nào giúp che chắn và ngăn chặn EMI? Các sơ đồ xếp chồng lớp sau đây giả định rằng dòng điện chạy trên một lớp duy nhất và một điện áp hoặc nhiều điện áp được phân phối trên các phần khác nhau của cùng một lớp. Trường hợp của nhiều mặt phẳng năng lượng sẽ được thảo luận sau.

1) Bảng 4 lớp: Thiết kế của bảng 4 lớp có một số vấn đề tiềm ẩn. Thứ nhất, đối với các tấm bốn lớp truyền thống có độ dày 62 mils, ngay cả khi lớp tín hiệu ở bên ngoài và lớp nguồn và lớp tiếp xúc ở bên trong, khoảng cách giữa lớp nguồn và lớp tiếp xúc vẫn còn quá lớn. Nếu yêu cầu chi phí được đưa ra, hãy xem xét các lựa chọn thay thế cho hai tấm bốn lớp truyền thống sau đây. Cả hai giải pháp đều có thể cải thiện hiệu suất ức chế EMI, nhưng chỉ khi mật độ thành phần trên tấm đủ thấp và có đủ khu vực xung quanh thành phần (nơi đặt lớp đồng cung cấp điện mong muốn). Các lớp bên ngoài của PCB là sự hình thành và hai lớp giữa là tín hiệu/nguồn điện. Nguồn điện trên lớp tín hiệu được định tuyến bằng dấu vết rộng, cho phép trở kháng đường dẫn thấp hơn cho dòng điện và trở kháng thấp hơn cho đường dẫn vi băng tín hiệu. Từ quan điểm điều khiển EMI, đây là một cấu trúc bảng mạch PCB 4 lớp hiện có. Trong sơ đồ thứ hai, các lớp bên ngoài lấy điện và nối đất và hai lớp ở giữa lấy tín hiệu. Những cải tiến trong sơ đồ này ít hơn so với các tấm 4 lớp truyền thống, với trở kháng giữa các lớp kém như các tấm 4 lớp truyền thống. Nếu trở kháng dấu vết được kiểm soát, sơ đồ xếp chồng lên nhau ở trên đòi hỏi phải định tuyến dấu vết rất cẩn thận dưới các đảo đồng cung cấp điện và mặt đất. Ngoài ra, các đảo đồng trên mặt phẳng nguồn điện hoặc mặt đất nên được kết nối càng chặt chẽ càng tốt để đảm bảo kết nối DC và tần số thấp.

2) 6 lớp hội đồng quản trị: Nếu mật độ của các thành phần trên 4 lớp hội đồng quản trị là tương đối lớn, 6 lớp hội đồng quản trị được sử dụng. Tuy nhiên, một số sơ đồ xếp chồng trong thiết kế bảng 6 lớp không đủ để che chắn trường điện từ và ít ảnh hưởng đến tín hiệu thoáng qua làm giảm thanh cái nguồn. Hai ví dụ được thảo luận dưới đây. Ví dụ, nguồn điện và mặt đất được đặt trên lớp thứ hai và thứ năm tương ứng. Do trở kháng cao của lớp phủ đồng cung cấp điện, việc kiểm soát bức xạ EMI chế độ chung là rất bất lợi. Tuy nhiên, từ quan điểm kiểm soát trở kháng của tín hiệu, phương pháp này là khá chính xác. Ví dụ thứ hai đặt nguồn điện và mặt đất tương ứng ở lớp thứ ba và thứ tư. Thiết kế này giải quyết vấn đề trở kháng của lớp phủ đồng cung cấp điện. EMI chế độ khác biệt tăng lên do hiệu suất che chắn điện từ kém của lớp đầu tiên và lớp thứ sáu. Thiết kế này có thể giải quyết vấn đề EMI chế độ khác biệt nếu số lượng đường tín hiệu trên cả hai lớp ngoài là nhỏ và chiều dài dấu vết ngắn (ngắn hơn 1/20 bước sóng hài tín hiệu). EMI chết vi sai được ức chế đặc biệt tốt bằng cách lấp đầy các khu vực không thành phần và không dấu vết trên lớp ngoài bằng đồng và nối đất các khu vực phủ đồng (một khoảng cách cho mỗi bước sóng 1/20). Như đã đề cập trước đó, khu vực đồng nên được kết nối với mặt phẳng nối đất bên trong tại nhiều điểm. Các thiết kế bảng 6 lớp hiệu suất cao nói chung thường sắp xếp các lớp 1 và 6 thành các tầng, và các lớp 3 và 4 để lấy điện và nối đất. EMI ức chế là tuyệt vời do hai lớp dây tín hiệu microband kép trung tâm giữa mặt phẳng nguồn và mặt đất. Nhược điểm của thiết kế này là chỉ có hai lớp dấu vết. Như đã đề cập trước đó, nếu các dấu vết bên ngoài ngắn hơn và đồng được đặt trong khu vực không có dấu vết, thì việc xếp chồng tương tự có thể đạt được với các tấm 6 lớp truyền thống. Một cách bố trí bảng 6 lớp khác là tín hiệu, mặt đất, tín hiệu, nguồn điện, mặt đất và tín hiệu, cho phép môi trường cần thiết cho thiết kế toàn vẹn tín hiệu. Lớp tín hiệu liền kề với mặt phẳng nối đất và mặt phẳng nguồn và mặt phẳng nối đất được ghép nối. Rõ ràng, nhược điểm là sự mất cân bằng xếp chồng của các lớp. Điều này thường gây ra rắc rối trong sản xuất. Giải pháp cho vấn đề là lấp đầy tất cả các khu vực trống của lớp thứ ba bằng đồng. Nếu mật độ đồng của lớp thứ ba gần với lớp điện hoặc hình thành sau khi đồng được lấp đầy, bảng có thể được tính là một bảng mạch cân bằng cấu trúc. Khu vực làm đầy đồng phải được kết nối với nguồn điện hoặc mặt đất. Khoảng cách giữa các lỗ được kết nối vẫn là bước sóng 1/20 và không nhất thiết phải ở khắp mọi nơi, nhưng lý tưởng nhất nên được kết nối.

3) Bảng 10 lớp: Do lớp cách điện giữa các bảng nhiều lớp rất mỏng, trở kháng giữa các lớp của bảng 10 hoặc 12 lớp là rất thấp. Miễn là không có vấn đề gì với việc xếp lớp và xếp chồng lên nhau, nó hoàn toàn hứa hẹn tính toàn vẹn tín hiệu tuyệt vời. Việc sản xuất các tấm 12 lớp với độ dày 62 mils là khó khăn hơn và không có nhiều nhà sản xuất có thể xử lý các tấm 12 lớp.

Vì luôn có một lớp cách điện giữa các lớp tín hiệu và các lớp vòng lặp, giải pháp phân bổ 6 lớp trung gian trong thiết kế bảng 10 lớp để định tuyến các đường tín hiệu không phải như vậy. Một lần nữa, điều quan trọng là làm cho lớp tín hiệu liền kề với lớp vòng lặp, tức là, bố trí bảng là tín hiệu, mặt đất, tín hiệu, nguồn điện, mặt đất, tín hiệu, tín hiệu, tín hiệu, mặt đất, tín hiệu. Thiết kế này cung cấp một con đường tốt cho dòng tín hiệu và dòng vòng của nó. Một chiến lược định tuyến thích hợp là định tuyến layer 1 theo hướng X, layer 3 theo hướng Y, layer 4 theo hướng X, v.v. Trực quan, layer 1 và layer 3 là một cặp layer combo, layer 4 và layer 7 là một cặp layer combo, layer 8 và layer 10 là một cặp layer combo. Khi cần phải thay đổi hướng của dấu vết, đường tín hiệu trên lớp đầu tiên phải "thông qua lỗ" đến lớp thứ ba và sau đó thay đổi hướng. Trong thực tế, điều này có thể không phải lúc nào cũng có thể được thực hiện, nhưng như một triết lý thiết kế, nó nên được cố gắng tuân thủ. Tương tự như vậy, khi hướng định tuyến của tín hiệu thay đổi, nên đi qua lớp 8 và lớp 10 hoặc lớp 4 đến lớp 7. Kiểu định tuyến này đảm bảo khớp nối chặt chẽ giữa đường đi về phía trước và đường trở lại của tín hiệu. Ví dụ, nếu tín hiệu được định tuyến trên lớp 1 và vòng lặp được định tuyến trên lớp 2 và chỉ trên lớp 2, vòng lặp của nó vẫn ở trên lớp 2 ngay cả khi tín hiệu từ lớp 1 đến lớp 3 thông qua "lỗ hổng", do đó duy trì độ tự cảm thấp, điện dung cao và hiệu suất che chắn điện từ tốt. Điều gì sẽ xảy ra nếu hệ thống dây điện thực sự không hoạt động theo cách đó? Ví dụ, một đường tín hiệu trên tầng đầu tiên đi qua lỗ để đến tầng thứ mười. Tại thời điểm này, tín hiệu vòng lặp phải tìm mặt phẳng nối đất từ tầng thứ chín và dòng điện vòng lặp cần tìm lỗ nối đất gần nhất (ví dụ: chân nối đất cho các thành phần như điện trở hoặc tụ điện). Nếu bạn tình cờ có một lối đi như vậy gần đó, bạn thực sự may mắn. Nếu không có lỗ thủng chặt chẽ này, độ tự cảm sẽ tăng lên, điện dung sẽ giảm và EMI chắc chắn sẽ tăng lên. Khi đường tín hiệu phải rời khỏi cặp dây hiện tại sang các lớp dây khác qua lỗ, lỗ nối đất nên được đặt gần lỗ nối để tín hiệu vòng lặp có thể quay trở lại thành tầng nối đất thích hợp một cách trơn tru. Đối với sự kết hợp nhiều lớp của lớp 4 và 7, vòng lặp tín hiệu sẽ quay trở lại từ lớp nguồn hoặc hình thành (tức là lớp 5 hoặc 6) vì điện dung giữa lớp nguồn và hình thành được ghép nối tốt và tín hiệu dễ truyền.

Thiết kế nhiều lớp điện

Nếu hai mặt phẳng cung cấp điện của cùng một nguồn điện áp yêu cầu đầu ra dòng điện lớn, bảng mạch phải được bố trí trong hai bộ mặt phẳng cung cấp điện và mặt đất. Trong trường hợp này, lớp cách nhiệt được đặt giữa mỗi cặp mặt phẳng nguồn và mặt phẳng nối đất. Bằng cách này, chúng ta có hai cặp bus cung cấp điện có trở kháng bằng nhau và chúng ta mong đợi chúng chia đều dòng điện. Nếu ngăn xếp của mặt phẳng công suất tạo ra trở kháng không bằng nhau, shunt sẽ không đồng đều, điện áp thoáng qua sẽ lớn hơn nhiều và EMI sẽ tăng mạnh. Nếu bạn có nhiều điện áp cung cấp điện với các giá trị khác nhau trên bo mạch, bạn sẽ cần nhiều mặt phẳng cung cấp điện, hãy nhớ tạo các mặt phẳng nguồn và mặt đất theo cặp của riêng bạn cho các nguồn điện khác nhau. Trong cả hai trường hợp trên, hãy nhớ các yêu cầu của nhà sản xuất đối với cấu trúc cân bằng khi xác định vị trí trên tấm phù hợp với nguồn điện và mặt đất.

Tóm tắt

Xem xét rằng hầu hết các kỹ sư thiết kế bảng như một bảng mạch in truyền thống với độ dày 62 mils và không có lỗ mù hoặc lỗ chôn, cuộc thảo luận về việc xếp lớp và xếp chồng bảng chỉ giới hạn ở đây. Đối với các tấm có độ dày quá khác nhau, sơ đồ phân tầng được đề xuất trong bài viết này có thể không lý tưởng. Ngoài ra, bảng mạch có lỗ mù hoặc lỗ chôn được xử lý khác nhau và phương pháp phân lớp của bài viết này không áp dụng. Độ dày của bảng, quá trình đục lỗ và số lớp, thiết kế không phải là chìa khóa để giải quyết vấn đề. Xếp chồng lớp tuyệt vời được thiết kế để đảm bảo bỏ qua và tách thanh cái cung cấp điện để điện áp thoáng qua trên mặt phẳng nguồn hoặc mặt đất không bị ảnh hưởng. Chìa khóa để che chắn tín hiệu và trường điện từ của nguồn điện. Lý tưởng nhất, nên có một lớp cách nhiệt giữa dấu vết tín hiệu và sự hình thành trở lại của nó, và khoảng cách giữa các cặp (hoặc nhiều hơn một cặp) nên càng nhỏ càng tốt. Dựa trên các khái niệm và nguyên tắc cơ bản này, bảng mạch PCB luôn có thể đáp ứng các yêu cầu thiết kế có thể được thiết kế.