Vào trong PCB tốc độ cao thiết kế và dây dẫn, đường dài khớp là thường lệ. Lúc này, Nó cần thiết phải đặt các quy tắc giới hạn và áp dụng chúng cho các nhóm lưới khác nhau.. Thí dụ như thể hiện những bước cụ thể của việc thiết lập những hạn chế này.

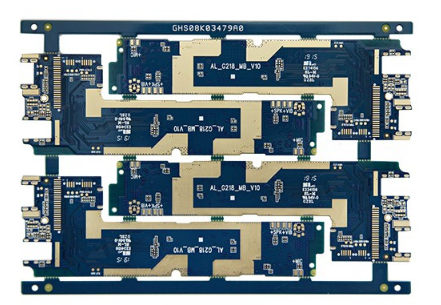

L. Thiết kế và dây dẫn PCB

Đồng hồ DDR: ngang đường 10mil, Khoảng cách nội bộ 5mil, Khoảng cách 30mil bên ngoài. Có yêu cầu thiết kế và dây dẫn khác nhau, và lỗi nối dây với cặp khác nhau phải được xác minh chính xác, cho phép bên trong..Name0mili

Thông tin DDR, chip được chọn và các đường điều khiển khác: đường rộng 5mil, nội khoảng cách 15mil, khoảng cách xa 20mil, phải nằm trong một địa hình chuỗi Daisy, mà có thể dài 1000-25000m hơn đường ddrclk, và không phải ngắn hơn

Đường dữ liệu DDR, ddmqs, ddmm lines: lines width 5mil, interior sparing 15mil, external khoảng cách 20mil, it is best to draw to drap of PCB. Khoảng cách chiều dài dòng giữa dòng dữ liệu và đồng hồ được điều khiển trong một triệu đô-la.

2. Dựa trên những yêu cầu này, đặt các giới hạn khác trong Thiết kế PCB Sắc

Đối với độ rộng dòng (vật lý) cần phải đặt chỉ có 3 các giới hạn: DDR. u CLK, DDR u ADR, DDR u dữ liệu

Sau khi đặt các hạn chế trên, bạn có thể thêm những hạn chế này vào lưới. Nhấn nút đính... trong bộ điều luật vật lý, và sau đó nhắp nhiều hơn vào bảng điều khiển bên phải,

hộp thoại pop-up

Tìm ckKo và ckp0, nhắp vào áp dụng, nó sẽ bật lên

Hãy chọn vô trong danh sách bên trái, ghi DDR u CLK trong không gian bên phải, và nhắp vào nút bật lên để bật lên.

Tức là, hai cái lưới này đã thêm vào tài năng ECT. (Hệ Tư pháp) u thuộc loại hình, và giá trị là DDRuCLK.

Cũng tương tự, bạn có thể đặt mạng lưới (trình nguyên vô tận) của dòng dữ liệu DDR, dòng điện strobe và đường dẫn màn hình cho DDR dữ liệu dữ liệu hôn nhân, và trình vô tận (đài) định dạng) của dòng địa chỉ DDR, dòng lựa chọn chip, và các đường điều khiển khác cho DDR ADR.

Sau khi những bước trên được hoàn thành, những giới hạn đã được đặt phải được áp dụng cho các nhóm lưới này.

Nhấn vào bàn phân công...

hộp thoại pop-up

Chọn các giới hạn vật lý riêng cho các nhóm tín hiệu khác nhau

Ai đó có thể hỏi, tại sao lại có vùng núi? Bởi vì có những giới hạn này không thể đạt được ở một số nơi.. Ví dụ như, trong CPU của gói Bga, khi đầu mối xuất hiện, Đường khoảng cách không thể với 30, ♪ 20 or even 10 mills. Ở những nơi này, nếu bạn làm theo điều đó, Không thể loại bỏ được Thc trong PCB. Lúc này, một giải pháp là phân loại những nơi này như một căn phòng, and then add the room attribute to it (that is, tên của khu vực căn phòng, 1, Comment.). Cho các phòng này, set appropriate constraints (ibid.).

Về khoảng cách giữa dòng, mỗi con được chia làm khoảng cách trong nhóm và khoảng cách bên ngoài nhóm, có sáu giới hạn trong tổng hợp:

Thưa ngài, đây là thứ tôi muốn nói, thứ gì đó, thứ gì đó, thứ gì đó, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai, thứ hai.

Chỉ cần đặt đường tới đường và đường theo hình dạng cho sáu giới hạn này, và đặt nó theo hai yêu cầu trên.

Những bước còn lại giống với thiết lập thể chất. Nhưng vào thời điểm này, bàn phân công trở thành như sau.

Phần trên là nội dung chi tiết về các bước thiết lập của luật lệ điều khiển Allegro cho kế hoạch PCB.