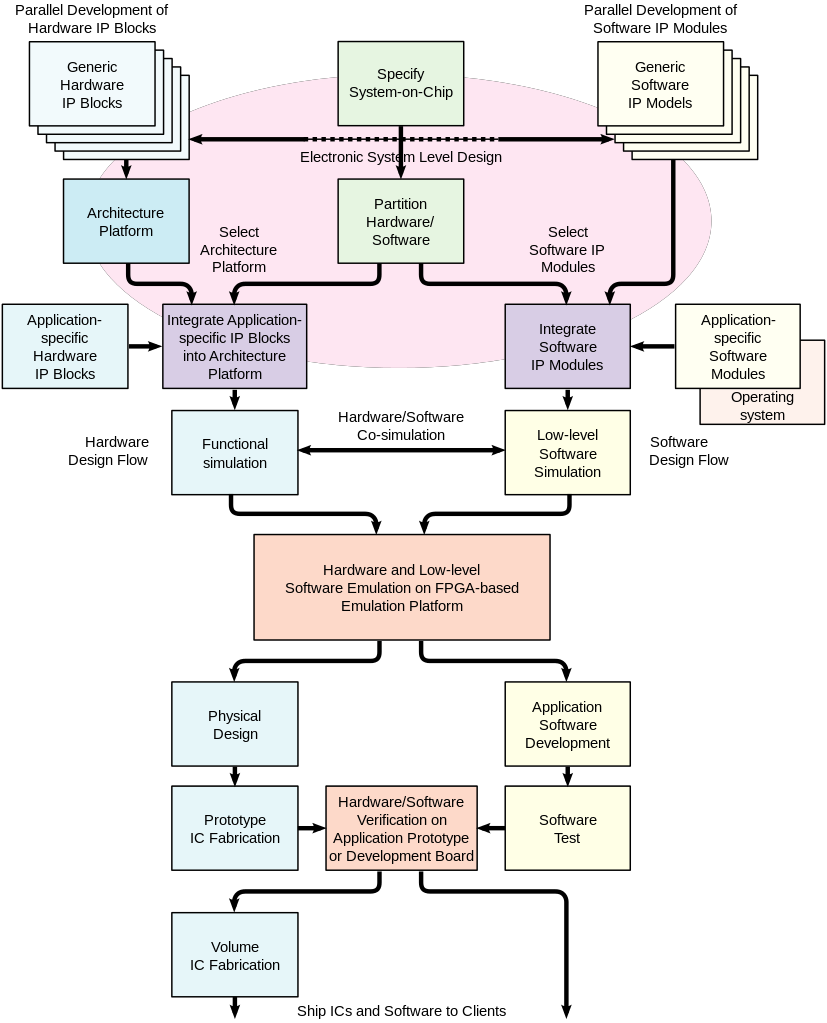

Processo di progettazione del chip IC

Il design del chip IC è diviso in design front-end e design back-end, il design front-end (noto anche come progettazione logica) e il design back-end (noto anche come progettazione fisica) non è confini rigorosi unificati, coinvolgendo il design relativo al processo è il design back-end.

Progettazione frontale del chip IC

1. Formulazione specifica

Una specifica chip, come una lista di funzionalità, è una richiesta del cliente a una società di progettazione di chip (chiamata Fabless) che include specifici requisiti funzionali e prestazionali che il chip dovrebbe soddisfare.

2. Progettazione dettagliata

Fabless propone soluzioni di progettazione e architetture di implementazione basate sulle specifiche del cliente e divide le funzioni dei moduli.

3. La codifica HDL

L'uso del linguaggio di descrizione hardware (VHDL, Verilog HDL, aziende del settore sono generalmente utilizzate in quest'ultimo) funzioni modulo per descrivere il codice per ottenere, cioè, le funzioni reali del circuito hardware sono descritte dal linguaggio HDL, la formazione del codice RTL (livello di trasferimento del registro).

4. Verifica della simulazione

La verifica di simulazione è quella di verificare la correttezza del progetto di codifica, e lo standard di verifica è la specifica formulata nel primo passo. Per vedere se il design soddisfa accuratamente tutti i requisiti della specifica. La specifica è il gold standard per un design corretto e tutto ciò che non è conforme alla specifica deve essere riprogettato e codificato. La verifica di progettazione e simulazione è un processo iterativo fino a quando i risultati della verifica non mostrano la piena conformità alle specifiche. VCS di Synopsys, e NC-Verilog di Cadence.

5. Sintesi logica -- Compilatore di progettazione

La verifica della simulazione viene superata e viene eseguita la sintesi logica. Il risultato della sintesi logica è quello di tradurre il codice HDL in netList. La sintesi deve impostare vincoli, che sono i criteri che si desidera che il circuito integrato soddisfi in termini di area, tempistica e così via. La sintesi logica deve essere basata su una libreria di sintesi specifica. In diverse librerie, i parametri di area e temporizzazione della cella standard di base del circuito gate sono diversi. Pertanto, la selezione della biblioteca completa non è la stessa, il circuito integrato nel tempo, l'area è diversa. In generale, una volta completata la sintesi, è necessaria di nuovo una verifica di simulazione (questa è anche chiamata post-simulazione, e la precedente è chiamata pre-simulazione). Compilatore di progettazione per lo strumento di sintesi logica Synopsys.

6. STA

Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA): Analisi del timing statico (STA) Statistic Timing Analysis (STA): Static Timing Analysis (STA): Static Timing Analysis (STA) Questa è la conoscenza di base dei circuiti digitali, un registro con queste due violazioni di temporizzazione, non c'è modo di campionare correttamente i dati e i dati di uscita, quindi la funzione di chip digitale basata sul registro avrà sicuramente problemi.

Lo strumento STA ha Synopsys Prime Time.

7. Verifica formale

Questa è anche una categoria di convalida, che verifica funzionalmente la netlist sintetizzata (STA è timing). Il metodo comunemente usato è il controllo di equivalenza. Prendendo come riferimento il design HDL dopo la verifica della funzione, la funzione netlist completa viene confrontata per determinare se sono funzionalmente equivalenti. Questo viene fatto per garantire che non ci siano cambiamenti nella funzionalità del circuito originariamente descritto in HDL durante il processo di sintesi logica.

Formalità La formalità è lo strumento di Synopsys.

Il processo di progettazione front-end è scritto qui per il momento. In termini di progettazione, il risultato della progettazione front-end è quello di ottenere il circuito netmeter del gate del chip IC.

Progettazione back-end di progettazione del chip IC

1. DFT

Design For Test. I chip hanno spesso circuiti di prova integrati e i DFT sono progettati pensando ai test futuri. Un approccio comune al DFT consiste nell'inserire una catena di scansione nel progetto per trasformare un'unità non-scansione (come un registro) in un'unità di scansione. Alcuni libri hanno informazioni dettagliate su DFT, quindi è facile capirlo confrontando le immagini.

Compilatore DFT dello strumento DFT Synopsys

2. FloorPlan

La pianificazione del layout consiste nel posizionare il modulo macro unità del chip e determinare il posizionamento di vari circuiti funzionali in generale, come modulo IP, RAM, pin I/O e così via.

Lo strumento è Astro per Synopsys

3. CTS

La sintesi dell'albero dell'orologio, in poche parole, è il cablaggio dell'orologio. A causa della funzione di comando globale del segnale di clock nel chip digitale, la sua distribuzione dovrebbe essere simmetrica a ogni unità di registro, in modo che l'orologio dalla stessa sorgente di clock a ogni registro, la differenza di ritardo dell'orologio sia minima. Ecco perché i segnali di clock devono essere cablati separatamente.

Strumento CTS, compilatore fisico per Synopsys

4. Luogo e percorso

Il cablaggio qui è normale cablaggio del segnale, compreso il cablaggio tra varie unità standard (cancelli logici di base). Ad esempio, solitamente sentiamo che il processo 0.13um, o processo 90nm, è in realtà la larghezza minima del cablaggio metallico qui, che è la lunghezza del canale del tubo MOS dal punto di vista micro.

Sinossi dello strumento Astro

5. Estrazione di parametri parassitici

A causa della resistenza del filo stesso, l'induttanza reciproca tra i fili adiacenti, la capacità accoppiata all'interno del chip può produrre rumore di segnale, crosstalk e riflessione. Questi effetti possono causare problemi di integrità del segnale, con conseguente fluttuazione e variazioni della tensione del segnale e, se gravi, errori di distorsione del segnale. È molto importante analizzare il problema dell'integrità del segnale estraendo i parametri parassitari e verificando di nuovo.

Strumento Synopsys star-rCXt

6. Verificare il layout fisico

Al completamento del cablaggio del Layout fisico della verifica della funzione e della temporizzazione, la verifica di molti elementi, come la verifica LVS (Layout Vs Schematic), insomma, è il Layout e la sintesi logica della verifica comparativa dello schema circuitale a livello gate; RDC (Controllo delle regole di progettazione): Controllo delle regole di progettazione, controllare la spaziatura delle linee, la larghezza della linea per soddisfare i requisiti di processo, ERC (Controllo delle regole elettriche): Controllo delle regole elettriche, controllare il cortocircuito e il circuito aperto e altre violazioni delle regole elettriche; E così via.

Strumento per Synopsys Hercules

L'effettivo processo di back-end include anche l'analisi del consumo energetico del circuito e problemi DFM (Manufacturability design) mentre il processo di produzione continua a migliorare, che non saranno menzionati qui.

La verifica del layout fisico è il completamento dell'intera fase di progettazione del chip e la seguente è la produzione del chip. Il layout fisico è dato come file GDS II a una Fonderia, o Fonderia, che crea circuiti reali su un wafer di silicio, li imballa e li testa, e si ottiene il chip reale che vedete.

Documentazione di processo per la progettazione di chip

Nei collegamenti di progettazione importanti della progettazione del chip, come analisi di sintesi e temporizzazione, disegno del layout, ecc., sono necessari file di libreria di processo. Tuttavia, le persone spesso non comprendono i documenti di processo, quindi è difficile imparare qualcosa sulla progettazione del chip da sole. Ad esempio, l'apprendimento della progettazione del layout è solo un progetto cartaceo senza un file di libreria di grafici di processo. Questo articolo introduce principalmente le conoscenze relative alla libreria di processo.

La documentazione di processo è fornita dai produttori di chip, quindi è necessario avere una comprensione generale dei produttori nazionali e internazionali di chip. A livello internazionale, ci sono importanti produttori di semiconduttori come TSMC, Intel e Samsung. In Cina, ci sono principalmente SMIC, China Resources Shanghai, Shenzhen Fondatore e altre società. Queste aziende forniscono documenti pertinenti della biblioteca di processo, ma la premessa è quella di cooperare con queste aziende per ottenere, questi documenti di processo sono documenti riservati.

Il file completo della libreria di processo è composto principalmente da:

1, libreria di processo di simulazione, supporta principalmente i due spettri software e hSPICE, suffisso SCS -- Spectre, lib -- uso hSPICE.

2, la versione analogica del file della libreria di mappe, principalmente per il software di disegno della mappa cadenza, il suffisso tf, DRF.

3. Biblioteca completa digitale, che comprende principalmente la libreria di serie di timing, i componenti di netlist di base e altri relativi file di libreria completi e cronologici richiesti di analisi. Pricipalmente è utilizzato per la sintesi del software DC e l'analisi del tempo del software PT.

4. libreria di mappe digitali, principalmente per il software di incontro di cadenza per il layout automatico e l'instradamento, naturalmente, gli strumenti automatici di layout e routing utilizzeranno anche la libreria di temporizzazione, i file di vincolo integrati e così via.

5, biblioteca di verifica della mappa, principalmente RDC, controllo LVS. Alcuni Calibro di supporto specializzato e alcuni supporti specializzati Dracula, Diva e altri strumenti di ispezione delle mappe. Ogni file di libreria ha un documento di descrizione PDF corrispondente.

Il disegno inverso utilizzerà i file della libreria di processo 1, 2, 5, 3 e 4 non saranno utilizzati. Un disegno in avanti (un disegno in avanti che inizia con il codice) richiede tutti i file. La documentazione di due processi occupa una posizione molto importante nella progettazione del chip, la progettazione chiave ad ogni link viene utilizzata, più la sua proprietà riservata, quindi è difficile trovare i documenti completi di processo sulla rete per l'apprendimento individuale, avere una cadenza EETOP aperta per i file di libreria di processo di apprendimento personale può essere conveniente per tutti da imparare, ma sembra anche essere incompleta.

Sintesi della progettazione del chip

Che cos'è la sintesi? La sintesi è il processo di trasformazione/mappatura del codice Verilog a livello RTL in circuiti rappresentati da unità di base a livello gate utilizzando lo strumento Design Compiler. Le unità di base sono i cancelli nand, o cancelli nand, registri, ecc., ma queste unità di gate sono state trasformate in una libreria standard di unità che possiamo chiamare direttamente con il software, piuttosto che dover chiamare le unità di gate noi stessi per costruire il circuito. In termini semplici, il software Design Compiler fa il lavoro di tradurre il codice in circuiti reali, ma non si tratta solo di tradurre, si tratta di ottimizzare i circuiti e i vincoli di temporizzazione per renderli adatti ai requisiti prestazionali che abbiamo impostato. Come accennato in precedenza, il software è guidato da vincoli, quindi da dove viene il vincolo? La risposta è: specifiche progettuali. Ogni progetto di progettazione del chip avrà una specifica del progetto, che viene sviluppata all'inizio della progettazione del chip, nelle fasi di pianificazione generale (vedi sopra). I vincoli specifici devono essere attentamente presi in considerazione durante il processo di integrazione. Processo generale di sintesi:

1. processo di pre-sintesi;

2. Imporre processo di vincolo di progettazione;

3. Processo di sintesi progettuale;

4. Processo post-sintesi.

PS, un prerequisito per l'utilizzo del software Design Compiler è imparare a usare gli script DC TCL.

Processo di pre-sintesi. Questa parte consiste principalmente nella preparazione dei file della libreria (compresa la libreria di processo, la libreria di collegamenti, la libreria di simboli e la libreria completa) utilizzati dal processo completo, i file di input di progettazione e l'impostazione dei parametri ambientali.

Imporre vincoli progettuali al processo. Questa parte riguarda principalmente la scrittura di file di vincolo utilizzando script DC TCL. Gli elementi di vincolo specifici possono essere suddivisi in tre categorie:

A, vincolo di area, definire orologio, vincolo input / output path;

B. (attributo ambiente), vincola il driver di ingresso, vincola il carico di uscita, imposta le condizioni di lavoro (migliore, tipico, peggiore) e imposta il modello di carico di linea;

C. (vincolo avanzato dell'orologio), il jitter dell'orologio, offset, ritardo della sorgente dell'orologio, multi-clock sincrono, orologio asincrono, percorso multi-ciclo, queste categorie di vincoli dettagliati.

Alla faccia dei vincoli. Un file di vincolo di script TCL dettagliato contiene quasi tutti i vincoli di cui sopra. C'è un vincolo dietro il modello.

Progettare il processo integrato. Introduce principalmente il modulo di progettazione del circuito (per un migliore vincolo), il processo di ottimizzazione completa del compilatore di progettazione (tre fasi di ottimizzazione, livello della struttura, livello logico, livello del gate), il processo specifico di analisi della sequenza temporale e altre informazioni dettagliate nel processo completo.

Processo post-sintesi. Come si guarda ai risultati della sintesi? Come risolvi le violazioni dei tempi? Questo è ciò che riguarda il processo di post-sintesi. Dopo la sintesi, attraverso l'analisi del rapporto di sintesi, possiamo sapere come risulta la sintesi del circuito, secondo i requisiti che non soddisfano, ri costringono, o addirittura ridisegnano il circuito. In particolare in questa fase è una previsione completa, perché quando si scrive vincolo completo dello script, è necessario determinare il vincolo, la specifica generalmente non è in grado di coinvolgere così dettagli sezione, quindi bisogno di una previsione completa in base al circuito effettivo, dopo questo passaggio è nel codice, e testare allo stesso tempo, Per stimare approssimativamente il circuito è in linea con i requisiti, in questo caso, il processo di pre-sintesi è lo stesso della sintesi formale, ma i requisiti sono molto più rilassati. Il requisito di violazione della tempistica è di circa il 10% -15%, vale a dire, non importa se il 10% -15% del circuito non soddisfa la tempistica.

conclusione(iPCB.com)

Il processo di progettazione del chip è molto complesso, questo articolo è anche un semplice pettine del processo di progettazione del chip di nuovo, il complesso non si ripeterà.