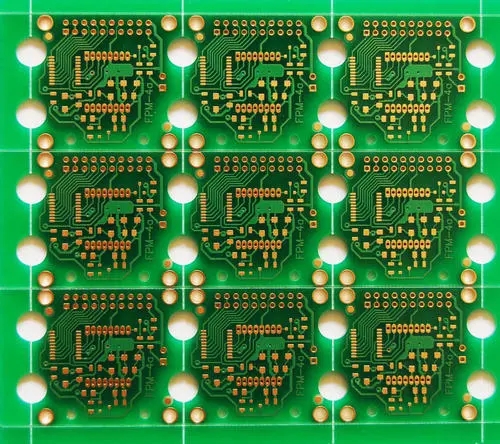

Regole di layout della scheda PCB DDR

Nel cablaggio dei circuiti stampati ordinari PCB, poiché il segnale è un segnale a bassa velocità, è generalmente collegato secondo la direzione di flusso del segnale sotto la regola di cablaggio di base del principio 3W e non c'è generalmente alcun problema. Ma se il segnale è superiore a 100M, il cablaggio è molto particolare. Poiché i segnali DDR con velocità fino a 300M sono stati implementati recentemente, spiegherò i principi e le tecniche di cablaggio dei segnali DDR in dettaglio.

I sistemi ad alta velocità utilizzano generalmente segnali a bassa tensione, che hanno bassa tensione e piccola oscillazione, che è facile aumentare la velocità e ridurre il consumo energetico. Ridurre al minimo la resistenza interna, come l'uso di piani elettrici, punzonare più fori, accorciare la distanza di cablaggio e utilizzare resistenze per dividere i segnali alla fine della trasmissione ad alta tensione per produrre segnali di tensione inferiore. Le tensioni del segnale di SDRAM, DDR-I, DDR-II e DDR-III sono inferiori a uno, rendendo sempre più difficile la stabilizzazione. Prestare attenzione anche all'alimentazione elettrica, se l'alimentazione elettrica è insufficiente, la memoria non funzionerà stabilmente. Il concetto di integrità del segnale e linea di trasmissione è una conoscenza relativamente professionale del sistema e non sarà descritto in dettaglio qui. Ora, anche se non comprendi il concetto di integrità del segnale e linee di trasmissione, segui le regole generali di base qui sotto. La scheda di segnale DDR ad alta velocità utilizzata non causerà problemi.

1) DDR e il chip di controllo principale sono il più vicino possibile. Tutte le coppie di segnali differenziali nei segnali DDR ad alta velocità devono essere rigorosamente uguali in lunghezza (è consentito fino a 50 mil di ridondanza) e la lunghezza di tutte le linee di segnale e le linee di clock non deve superare 2500 mil. Prova a 0 vias. Ci deve essere uno strato di terra ben messo a terra sotto lo strato componente e tutte le tracce non possono attraversare lo slot di divisione del suolo, cioè la linea di divisione del suolo che attraversa la linea del segnale non può essere vista dallo strato componente attraverso lo strato di terra. In questo caso, 400M DDR non è fondamentalmente un problema. Alcune altre regole 3W, 20H possono essere fatte il più possibile.

2) Indirizzo e gruppo di segnale di comando: mantenere un piano completo di terra e potenza. L'impedenza caratteristica è controllata a 50ï½60 Ω. Mantenere la distanza tra il gruppo di segnali e altri segnali non DDR almeno 20 mil. Il segnale nel gruppo dovrebbe corrispondere alla lunghezza della linea di clock DDR e il divario dovrebbe essere almeno entro 500 mil. Il valore della resistenza di corrispondenza della serie RS è 0ï½33 Ω, e il valore della resistenza di corrispondenza parallela RT dovrebbe essere 25ï½68 Ω. I segnali in questo gruppo non dovrebbero essere nella stessa riga di resistenza del gruppo di segnali dati.

3) Gruppo del segnale di controllo: Il gruppo del segnale di controllo ha il minimo segnale, con solo due segnali, clock abilita e chip select. Ancora bisogno di avere un piano di terra completo e piano di potenza per riferimento. Il valore della resistenza RS corrispondente alla serie è 0ï½33 Ω, e il valore della resistenza terminale corrispondente parallela RT è 25ï½68 Ω. Per evitare il crosstalk, i segnali in questo gruppo non possono trovarsi nella stessa riga di resistenza dei segnali dati.

4) Gruppo di segnale dati: Prendere il piano di terra come riferimento per fornire un piano di terra completo per il ciclo di segnale. L'impedenza caratteristica è controllata a 50ï½60 Ω. La larghezza della linea può essere la stessa della larghezza del segnale dell'orologio. Separare almeno 20 mil da altri segnali non DDR. La corrispondenza della lunghezza è impostata nell'unità del canale byte. La differenza di lunghezza del segnale dati DQ, dello strobo dati DQS e del segnale della maschera dati DM in ogni canale di byte dovrebbe essere controllata entro ±100mil (molto importante) e la differenza di lunghezza del segnale dei diversi canali di byte dovrebbe essere controllata entro 500 mil. La resistenza corrispondente RS in serie con DM e DQS è 0-33 Ω, e il valore della resistenza terminale corrispondente RT è 25-68 Ω. Se la riga di resistenza viene utilizzata per la corrispondenza, non dovrebbero esserci altri segnali DDR nella riga di resistenza dei dati.

5) Segnale dell'orologio: Prendere il piano di terra come riferimento per fornire un piano di terra completo per il cablaggio dell'intero ciclo dell'orologio e fornire un percorso a bassa impedenza per la corrente del ciclo. Poiché si tratta di un segnale differenziale di clock, la larghezza della linea e la spaziatura dovrebbero essere pre-progettati prima del routing e i requisiti di impedenza differenziale della CPU dovrebbero essere compresi e quindi il routing dovrebbe essere eseguito secondo questo vincolo. Tutti i segnali differenziali di clock DDR devono essere instradati sul piano chiave per evitare la conversione layer-to-layer. La larghezza della linea e la spaziatura differenziale devono garantire il principio 3W, l'impedenza singola della linea di segnale deve essere controllata entro 50-60 Ω, e l'impedenza differenziale deve essere controllata entro 100-120 Ω. La distanza tra il segnale dell'orologio e gli altri segnali deve essere mantenuta almeno 20 mil* per evitare interferenze con altri segnali. La distanza tra le tracce del serpente non dovrebbe essere inferiore a 20 mil. Il valore RS della resistenza terminale di serie è 15ï½33Ω, e il valore della resistenza terminale parallela opzionale RT è 25ï½68Ω. (Il valore della resistenza di terminazione dovrebbe essere collegato alla resistenza durante la progettazione del diagramma schematico)

6) Il condensatore di disaccoppiamento dovrebbe essere posizionato vicino al perno di alimentazione del chip nella sezione dell'alimentazione elettrica. Ci dovrebbero essere strati separati per l'alimentazione e la terra per i segnali di ritorno con bassa resistenza nelle vicinanze. L'alimentatore e lo strato di terra devono essere perforati il più possibile per garantire che il collegamento elettrico sia abbastanza buono e sbloccato.

Finché le regole e le tecniche di cui sopra saranno seguite, non ci saranno problemi con i segnali DDR ad alta velocità da LAYOUT. Nell'elaborazione a pari lunghezza di ogni segnale, al fine di garantire l'errore ammissibile della lunghezza della linea del segnale, è possibile utilizzare deliberatamente l'elaborazione del percorso a lunga distanza, di solito una linea serpentina è utilizzata per instradare la linea. Spesso vediamo "cavi di lunghezza uguale". Infatti, la stessa lunghezza non è lo scopo. Lo scopo reale è quello di soddisfare il tempo di installazione e di attesa, la stessa frequenza e fase, e il campionamento è corretto. La lunghezza uguale è solo il modo più semplice per raggiungere questo scopo e la lunghezza della linea dovrebbe essere analizzata quantitativamente. In termini di controllo dell'impedenza caratteristica online, lo spessore della linea dovrebbe essere generalmente richiesto, ma il processo di produzione e la costante dielettrica di ogni produttore di schede sono diversi, quindi è necessario chiedere al produttore di schede di controllare l'impedenza caratteristica della linea di segnale.