C'è qualche modo per SMT patch per ridurre alcuni problemi di guasto?

SMT patch si riferisce all'abbreviazione di una serie di processi tecnologici elaborati sulla base del PCB. PCB (Printed Circuit Board) è un circuito stampato. Quindi, c'è qualche modo per SMT patch per ridurre alcuni problemi di guasto?

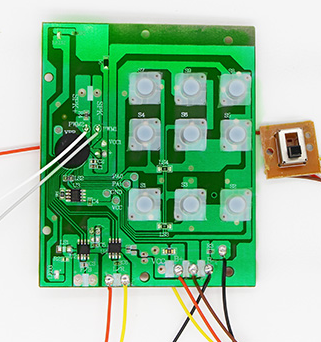

Patch SMT

Il processo di produzione, la manipolazione e i test di assemblaggio dei circuiti stampati (PCA) sottopongono il pacchetto a molte sollecitazioni meccaniche, che possono causare guasti. Man mano che il pacchetto grid array diventa sempre più grande, come impostare il livello di sicurezza per questi passaggi diventa sempre più difficile.

Per molti anni, il metodo di prova monotonico del punto di piegatura è una caratteristica tipica del pacchetto. La prova è descritta in IPC/JEDEC-9702 "Caratteristiche di piegatura monotonica delle interconnessioni a livello di bordo". Questo metodo di prova descrive la resistenza alla rottura dell'interconnessione orizzontale dei circuiti stampati sotto carico di flessione.

Tuttavia, questo metodo di prova non può determinare la tensione massima ammissibile.

Per il processo di produzione e il processo di assemblaggio, in particolare per il PCA privo di piombo, una delle sfide che deve affrontare è l'incapacità di misurare direttamente lo stress sui giunti di saldatura. La metrica più utilizzata per descrivere il rischio di componenti interconnessi è la tensione del circuito stampato PCB adiacente al componente, che è descritta in IPC / JEDEC-9704 "Linee guida per la prova di deformazione della scheda di cablaggio stampata".

Qualche anno fa Intel si rese conto di questo problema e iniziò a sviluppare una strategia di test diversa per riprodurre la peggiore situazione di flessione nella pratica. Altre aziende come Hewlett-Packard hanno anche capito i vantaggi di altri metodi di test e hanno iniziato a considerare idee simili a Intel. Poiché sempre più produttori e clienti di chip si rendono conto che la determinazione del limite di tensione utilizzato per ridurre al minimo i guasti meccanici durante la produzione, la movimentazione e il collaudo è di grande valore, questo metodo ha causato sempre più attenzioni. interessi.

Man mano che l'uso di apparecchiature senza piombo si espande, gli utenti sono sempre più interessati; perché molti utenti devono affrontare problemi di qualità.

Con l'aumento dell'interesse da parte di tutte le parti, IPC ritiene necessario aiutare altre aziende a sviluppare vari metodi di prova in grado di garantire che i BGA non siano danneggiati durante la produzione e i test. Questo lavoro è svolto congiuntamente dal gruppo di lavoro IPC 6-10d SMT Attachment Reliability Test Method e dal sottocomitato JEDEC JC-14.1 Packaged Equipment Reliability Test Method e il lavoro è stato completato.

Il metodo di prova specifica otto punti di contatto disposti in una matrice circolare. Il PCA con un BGA installato al centro del circuito stampato PCB è posizionato in questo modo: il componente è montato a faccia in giù sui pin di supporto e il carico viene applicato sul retro del BGA. Posizionare lo estensimetro adiacente alla parte secondo il layout raccomandato di IPC/JEDEC-9704.

Il PCA sarà piegato al livello di tensione pertinente e l'analisi dei guasti può determinare il grado di danno causato dalla deviazione a questi livelli di tensione. Il metodo iterativo può essere utilizzato per determinare il livello di tensione che non causa danni. Questo è il limite di tensione.