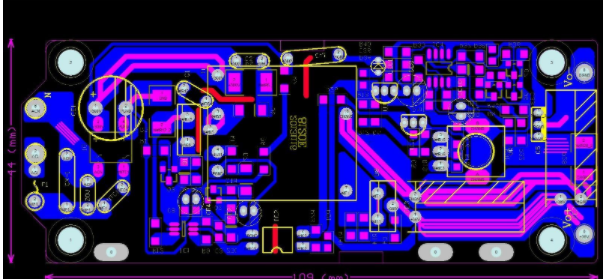

この記事は PCBデザイナー 誰がIP, さらに、PCB設計を迅速に完了するために、IPをサポートするためにトポロジー計画とルーティングツールを使用します. 図1からわかるように, 設計エンジニアは、必要なコンポーネントの数を配置し、これらのコンポーネント間の重要な相互接続経路を計画することによって、IPを取得する責任があります.

IPが取得されると、IP情報はPCBデザイナに提供され、PCBデザイナーは残りのデザインを完了します。PCB設計者は、IP設計を完全にPCB設計を完了するために、トポロジー計画とルーティングツールをさらに使用します。今では、設計エンジニアとPCBデザイナーの間の相互作用と反復プロセスを通して正しい設計意図を得る必要はありません。設計者はこの情報を得ており、結果は非常に正確です。PCBデザイナーにとって大きな助けとなります。多くのデザインでは、設計エンジニアとPCBデザイナーは双方向のレイアウトとルーティングを実行しなければなりません。過去の経験から、インタラクティブな操作が必要ですが、時間がかかると非効率的。

デザインエンジニアによって提供される予備計画は、適切なコンポーネントスケール、バス幅またはピン出力プロンプトなしでマニュアル図面だけであるかもしれません。

PCB設計者が設計に参加すると、トポロジー計画技術を使用するエンジニアは、あるコンポーネントのレイアウトと相互接続を得ることができる。この設計はまた、他の構成要素のレイアウト、他のIOおよびバス構造のコレクション、およびすべての相互接続の完了を必要とする。

PCBデザイナー トポロジー計画を採用する必要があります PCBレイアウト 最良のレイアウトとインタラクティブな計画を達成するレイアウトの下のコンポーネント, これにより、PCB設計の効率化. キー領域と高密度領域のレイアウトの完了とトポロジー計画の取得, レイアウトは最終トポロジー計画に先行する可能性がある. したがって, いくつかのトポロジカルパスは、既存のレイアウトを使用する必要があります. 彼らは低い優先順位がありますが, 彼らはまだ接続される必要がある. したがって, 計画の一部は生産コンポーネントのレイアウトを中心に展開する.

加えて、計画のこのレベルは、他のシグナルのために必要な優先順位を提供するためにより詳細を必要とするかもしれません。特定の母線の自動ルーティングの前の若干の障害は、他のルーティング・レイヤーのためのオプションを有するアルゴリズムを提供できる。バスが第1の層の上でタイトなラインに編成されるので、デザイナーは第3のレイヤーとして変換部分を計画し始める。そして、詳細「3」で、母線がPCBを通過する距離を考慮する。層3上のこのトポロジパスは、インピーダンスを収容するための余分なスペースを必要とするので、頂部層よりも広いことに留意されたい。加えて、デザインはまた、層遷移(17ホール)の正確な位置を指定する。トポロジ経路が図3の右の部分から詳細「4」まで下降するとき、多くの単一ビットT字状接続点は、トポロジカル経路接続および各構成ピンから引き出される必要がある。PCB設計者は、レイヤ3上のほとんどの接続を維持し、コンポーネントピンを接続するために他の層を貫通している。

したがって、主ハーネスから第4層(ピンク)への接続を示すトポロジカル領域を引き出し、単位T−コンタクトを第2層に接続し、それからデバイスピンに接続するために他のビアを使用した。トポロジカルパスは、アクティブデバイスを接続するために、層3で詳細情報「5」に続く。それから、これらの接続は、能動デバイスの下で能動ピンからプルダウン抵抗器に接続している。

設計者は、レイヤ3からレイヤ1に接続するために別のトポロジ領域仕様を使用し、コンポーネントピンは能動デバイスおよびプルダウン抵抗器である。詳細な計画のこのレベルは約30秒で完了することができます。この計画を取得した後に、PCB設計者は、直ちに経路をたどって、更なるトポロジー計画をつくって、それから自動ルーティングを通してすべてのトポロジー計画を完了したいかもしれません。計画完了から自動配線の結果まで10秒弱。実際、この速度は重要ではありません。実際、あなたがデザイナーの意図を無視するなら、自動ルーティングの品質は非常に貧しいです。高品質自動配線を行うには約10秒かかる。トポロジー計画への抽象化レベルを上げることにより,配線時間全体を大幅に短縮する。相互接続が始まる前に、デザイナーはデザインを完了するために密度と可能性の本当に明確な理解をします。例えば、デザインでこの点でラインを保つ理由は?なぜ計画を続行し、後ろに行を追加するか?完全なトポロジーはいつ計画されるか?

上記の例を考慮すると、計画抽象化は、各ネットワーク上の多くのセグメントと多くの穴を持つ17の独立したネットワークの代わりに別の計画で使用することができます。このコンセプトは、エンジニアリング変更命令(生態、プロジェクト)を考慮する際に非常に重要です。

次の例では、FPGAピン出力はまだ完了していません。設計技師はこの現実のPCB設計者に通知しました、しかし、進歩理由のために、彼らはFPGA PIN出力が完了する前に、できるだけデザインを進める必要があります。既知のピン出力の場合、PCB設計者はFPGA空間を計画し始め、設計者は同時に計画を完了し、他のデバイスからFPGAへのリードを考慮する。IOは当初FPGAの右側に予定されていましたが、現在FPGAの左側にあり、ピン出力がオリジナルの計画と完全に異なります。

PCBデザイナー 設計の始めにトポロジー計画ツールを使用できる, または、デザインエンジニアがIP, 誰がこの柔軟なツールを使用して設計環境に最適に適応. トポロジカル配線は、デザイナーの計画または意図を示す 高品質PCB 配線結果. エコ直面, トポロジー計画は別々の接続操作よりずっと速い, したがって、トポロジー配線装置は、より迅速にエコを採用することができる, それによって、速くて正確な結果を提供する.