におけるインピーダンス整合の研究 PCB設計, インピーダンスマッチングは信号の品質に関連する. インピーダンスマッチング技術は豊かでカラフルであると言える, しかし、特定のシステムでより合理的にそれを適用する方法は、いくつかの要因を測定する必要がある. 例えば, システムでシリアルマッチングを使用する多くのソースセグメントを設計しました.

なぜこのメソッドは、マッチングが必要なときに、どのような方法で使用されます。例えば、マッチングの違いはほとんど端末マッチングを使用しますクロックは、ソースセグメントマッチングを使用します直列端子整合直列端子整合の理論的出発点は、信号源インピーダンスが伝送線路の特性インピーダンスよりも低い場合、抵抗Rが信号源と伝送線路との間に直列に接続されていることである。同時に、出力端インピーダンスが伝送端のソース端および特性インピーダンスより大きいようにするために、もう一度、終点から反映されるシグナルを抑制する。

信号伝送直列端子が整合した後、以下の特性を有する。

1:直列整合抵抗の影響により、駆動信号は50 %で振幅の負荷端に伝達される。

2:負荷端のB信号の反射係数は+1に近いので、反射信号の振幅は元の信号振幅の50 %に近い。

図3に示すように、反射端において伝播された信号に反射された信号が重畳されるので、負荷端で受信される信号の振幅は、元の信号とほぼ同じである

4:負荷端からの反射された信号は、ソース端に伝搬し、ソース端に到達すると、整合抵抗によって吸収される

E反射信号がソース端に達すると、次の信号が送られるまで、ソース側駆動電流は0に降下する。

並列マッチングと比較して,直列マッチングは信号ドライバに大きな電流駆動能力を必要としない。抵抗値に一致する直列端子を選択する原理は単純であり、すなわち、整合抵抗値とドライバの出力インピーダンスとの和は伝送線路の特性インピーダンスに等しい。理想的な信号ドライバの出力インピーダンスはゼロであり、実際のドライバは常に比較的小さい出力インピーダンスを有し、信号レベルが変化すると出力インピーダンスは異なることがある。例えば、電源電圧は+4.5 VのCMOSドライブであり、典型的な出力インピーダンスは低電力消費では37アンペアであり、典型的な出力インピーダンスは高電力で45アンペアであるTTLドライブとCMOSドライブは、信号レベルが変化すると出力インピーダンスが変化する。

したがって、妥協解において考慮されることができるだけであるTTLまたはCMOS回路のための非常に正確な整合抵抗を提供することは不可能である。連鎖トポロジーの信号網は直列端子との整合には適しておらず,すべての負荷は伝送線路の端に接続しなければならない。一方、負荷の終了時の信号振幅は、本来の信号振幅の半分である。明らかに、信号は不確実な論理状態にあり、信号のノイズ耐性は非常に低い。直列マッチングは最も一般的に用いられる端末整合法である。それは、低消費電力の利点を有し、ドライバに対する追加のDC負荷はなく、信号と接地との間の追加インピーダンスはなく、1つの抵抗素子のみが必要である。

並列端子整合の理論的出発点に平行な端子整合は、信号源のインピーダンスが非常に小さいとき、負荷端の入力インピーダンスが並列抵抗を増加させることによって伝送線路の特性インピーダンスと整合し、負荷端での反射をなくす目的を達成することである。

実現形態は,単抵抗と二重抵抗の二つの形態に分けられる。並列端子整合信号伝送は、以下の特性を有する。駆動信号は、ほぼ完全な伝送線路に沿ってほぼ伝搬するすべての反射は、一致する抵抗によって吸収されます負荷端で受信される信号振幅は、信号源によって送られる信号振幅とほぼ同じである。実際の回路系では、チップの入力インピーダンスが非常に高いので、単一の抵抗形式では、負荷端の並列抵抗値は伝送線路の特性インピーダンスに類似または等しい必要がある。伝送線路の特性インピーダンスが50アンペアであるとすると、R値は50アンペアである。信号が5 Vの高レベルである場合、信号の静止電流は100 mAに達する。

beccoは典型的なttlまたはcmos回路の小型ドライバ容量を使用し,これらの回路ではこのような並列マッチングはほとんど起こらない。つの抵抗形式(また、Davidnan端子整合と呼ばれる)の並列マッチングは、単一の抵抗形式より小さい電流駆動能力を必要とする。これは、2つの抵抗器の並列値が伝送線路の特性インピーダンスに一致し、各特性インピーダンスが伝送線路の特性インピーダンスよりも大きいためである。

チップの駆動能力の観点から、2つの抵抗値の選択は、3つの原則に従わなければならない。

つの抵抗器の並列値は伝送線路の特性インピーダンスに等しい

2:電源に接続された抵抗値はあまり小さくないべきであり、通常の駆動電流を避けるためには、低電力信号を避けることができない。

3:接地に接続された抵抗値は、通常の駆動電流の下で信号が大きすぎるのを避けるには小さすぎるべきではない。並列端子整合の利点は簡単であり,実現可能である。明らかな欠点は、それがDC電力消費をもたらすということである。単一の抵抗器のDC電力消費は、信号のデューティサイクルと密接に関連しているか。信号がハイかローかに関わらず、デュアル抵抗モードはDC電力消費を有する。したがって、バッテリ電力システムのような、高い電力消費要件を有するシステムには適していない。

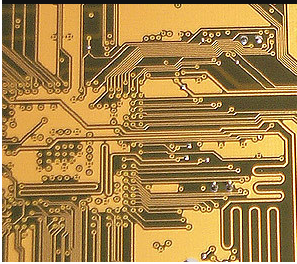

加えて, 単一抵抗モードは、一般的なTTLドライブ能力によりCMOSシステムを使用しない, デュアル抵抗モードは2つのコンポーネント, が必要 PCBボードエリア, したがって、高密度プリント回路基板には適しない. もちろん, 交流端子整合, ダイオード電圧クランプおよび他のマッチング方法.

PCB設計者が伝送線路自体の特性インピーダンス(Z 0)を28オームに設定すると、伝送線路がZ 0を維持するのを補助するために、端子管の接地抵抗(Zt)も28Ωでなければならず、全体の設計値で安定化できる。

Z 0 = ZTがマッチするときだけ、シグナル伝達は最も効果的です、そして、その「信号完全性」(信号完全性、特別な条件のための信号品質)も最高です。

PCB特性 impedance (characteristic impedance) 4.1 時 signal is square wave, 信号線が伝送線路に結合されるとき, 正電圧信号の高運動位置は前方である, then from its nearest reference layer (such as the ground layer) theoretically, the electrical field will pass through the accompanying The forward negative pressure signal (equal to the positive pressure signal reverse return path return path) to sense, so as to complete the overall loop (Loop) system. 「信号」がその飛行時間を凍結するために短いならば, it can be imagined that it has been subjected to the instantaneous impedance value (instantaneous impedance) presented by the line, 誘電層と基準層, 特性インピーダンスという.

したがって、「特性インピーダンス」は、線幅(w)、線厚(t)、誘電体厚さ(h)および誘電率に関連しなければならない。nstant(dk)ライン