はじめに

徐々に増加する PCBボード 設計複雑度, 反射に加えた信号完全性の解析, クロストーク, とEMI, 安定した信頼性の高い電源は設計者の重要な研究方向の一つとなっている. 特にスイッチング素子の数が増加し、コア電圧が低下している場合, 電源の変動はしばしばシステムに致命的な影響をもたらす, だから人々は新しい用語を提唱します, PI (power integrity). 今日の国際市場で, IC設計はより発展している, しかし、パワーインテグリティ設計はまだ弱いリンクです. したがって, 本報告書では、電源整合性問題の発生について述べる PCBボード, 電力供給の健全性に影響する因子の解析, そして、2000年における電源統合問題を解決するための最適化方法と経験設計を進めます PCBボード, 理論的解析と実用的な応用価値を持つ.

2電源ノイズの原因と解析

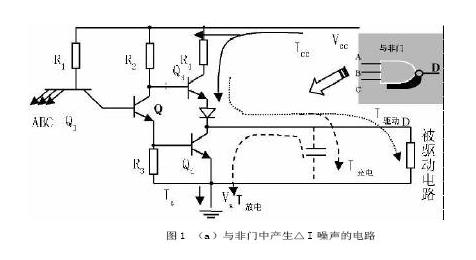

NANDゲート回路図によりパワーノイズ源を解析する. 回路図は、3入力NANDゲート100の構造を示す. NANDゲートはデジタルデバイスであるので, “1”と“0”レベルの間で切り替えることによって動作します. IC技術の継続的改善, ディジタルデバイスのスイッチング速度はより速く,より高速である, どちらが多い 高周波 コンポーネント, そして、ループのインダクタンスは、高周波数の電源の変動を引き起こすのが簡単である. 図1に示すように, NANDゲートの入力がすべて高電圧であるとき, 回路のトライオードはオンになる, 回路はすぐに短絡する, そして、電源はコンデンサを充電して、同時に接地線に流入する. この時に, 電力線および接地線の寄生インダクタンスのため, 我々は、公式v = LDIから知っています/これが電源ラインと接地線の電圧変動を発生させるDT, そして、図2に示すように、レベル立ち上がりエッジによって導入されたノイズIノイズ. NANDゲートの入力が低電流レベルであるとき, コンデンサは今度は放電する, そして、大きな線Iノイズは、接地線14に生成される. この時に, 電源は、回路の瞬間的短絡によって引き起こされる電流の突然変異のみを有する, コンデンサに電荷がないので, 現在の突然変異は立ち上がりエッジよりも小さい. NANDゲートの回路解析から, 電源の不安定性の原因は主に2つの側面にあることを知っている, 過渡交流電流が大きすぎる.

第2は電流ループに存在するインダクタンスである. いわゆるグランドパワーインテグリティ問題は 高速PCB 多数のチップが同時にオンまたはオフであるとき, 回路に大きな過渡電流が発生する, そして、電圧変動は、インダクタンス抵抗の存在によって、電源ラインおよび接地線の両方で生じる. 電源健全性問題の性質の理解, 我々は、電力供給の健全性問題を解決することを知っている, まず第一に, 高速装置用, そのコンデンサを取り除くためにデカップリングコンデンサを追加します 高周波 ノイズ成分, 信号の過渡時間を減らすループ内に存在するインダクタンスについて, 電力供給の階層設計を考えなければならない.

デカップルコンデンサの応用

デカップリングコンデンサは高速PCB設計に重要な役割を果たし,その配置も非常に重要である。これは、電源が短時間の負荷に電力を供給するときに、キャパシタの蓄積電荷が不適切なキャパシタ配置のような電圧降下を防止することができ、ラインインピーダンスが大きくなり、電源に影響を与えることができるからである。同時に、高速スイッチング時には、高周波ノイズをフィルタすることができる。高速PCB設計においては、一般に、電源の出力端およびチップの電源の入力端にデカップリングコンデンサを追加する。電源近傍のキャパシタンス値は、一般的に大きい(例えば10×1/4)。これは、PCBに一般的に直流電源が使用されるためであり、コンデンサの共振周波数は、電源のノイズをフィルタリングするために比較的低いことができる。同時に、大きな静電容量は、電源出力の安定性を確実にすることができる。デカップリングコンデンサのピン位置の電源に接続されたチップにおいては、その容量値は一般的に小さい(例えば0.1・1/4 F)、これは、高速チップでは、一般に比較的高いノイズ周波数であり、付加デカップリングコンデンサの共振周波数が高くなるように、すなわち、デカップリングコンデンサの容量を小さくする必要があるからである。

デカップリングコンデンサの配置に関しては、不適切な位置がラインインピーダンスを増加させ、その共振周波数を減らし、電源に影響を与えることを知っている。チップまたは電源のデカップリングコンデンサとインダクタンスのために、我々は式によって計算することができます。コンデンサとチップの間の線の長さr :線の半径D :送電線と地面の間の距離。したがって、インダクタンスL、LおよびDを減少させるためには、キャパシタとチップとをデカップリングすることによって形成されるループ面積を小さくする必要があること、すなわち、キャパシタンスおよびチップは、できるだけチップデバイスの近くになければならないことを知っている。

(4)電力ループの設計

電力供給の完全性を確保する, 我々は、良い配電網が不可欠であるということを知っています. まず第一に, for the デザイン of the power line and ground wire, we should ensure that the line width is thick (such as 40mil, while the ordinary signal line is 10mil), インピーダンス値をできるだけ小さくする. チップが速くなる, 5によると/5ルール, 我々はますます使用している 多層板, 専用の電力層によって電力を供給され、専用の層によって切断される, したがって、ラインのインダクタンスを減らす.