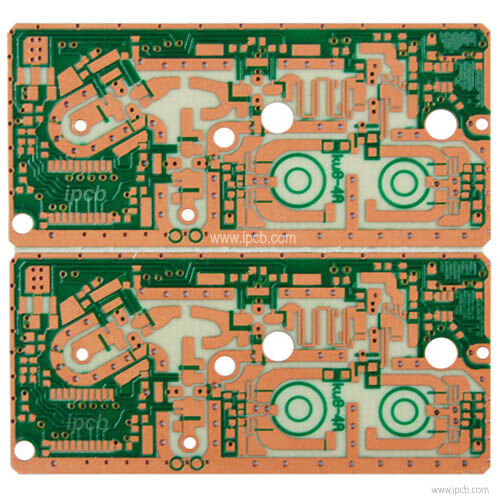

電子技術の急速な発展と様々な分野における無線通信技術の広い応用, 高周波, ハイスピード, そして、高密度は徐々に現代の電子製品の重要な開発傾向の1つになりました. マイクロホールへの信号伝達力PCBの高周波高速化/ブラインドホール, 微細導体, ミディアムレイヤー, 高周波, 高密度多層PCB設計技術は重要な研究分野になっている. ハードウェア設計の長年の経験に基づきます, 著者は、いくつかのデザインのスキルと問題の注意を必要と要約 高周波PCB 参考に.

1 . PCBシートの選択方法

PCBボードの選択は満足設計要件間のバランスを打たなければならない, 大量生産, コスト. 設計要件は、電気および機械部品の両方を含む. この物質問題は、通常、設計する際に重要です 高速PCBボード (( GHz以上の周波数)). 例えば, よく使われる電流 FR - 4 材料, in the frequency of several GHz dielectric loss (dielectric loss) can have a great impact on signal attenuation, 適切でない場合があります. 電気用, 誘電率に注意を払う, 設計された周波数での誘電損失は適切である.

2 .高周波妨害を避ける方法

高周波干渉を避ける基本的な考えは、クロストークとして知られている高周波信号の電磁場からの干渉を最小化することである。これらは、高速信号とアナログ信号との間の距離を延長したり、アナログ信号の他に接地ガード/シャントトレースを追加するために使用することができる。また,ディジタルグラウンドのアナロググランドへの雑音干渉に注目した。

高速度設計における信号完全性の問題解決法

信号完全性はインピーダンス整合の問題である。インピーダンス整合に影響する要因は、信号源構造および出力インピーダンス、ケーブルの特性インピーダンス、負荷側の特性、およびケーブルのトポロジーを含む。解決策は終了してルーティングのトポロジーを調整することです。

差動配線はどのように実装されていますか?

差動配線は、2つのラインの長さができるだけ長くなければならないという点で、もう一方は2つの線(差動インピーダンスによって決定される)間の距離が常に同じままであるべきであるということであるために、2つの点を有する。つの平行な方法があります:1つは2つの線が同じ層の上で並んで動いているということです、そして、もう一方は2つの線が2つの隣接した層の下で下で走っているということです。サイドバイサイド(サイドバイサイド、サイドバイサイド)はより一般的です。

クロック信号線の1つの出力だけのために、差動配線を達成する方法?

ソースと受信機の両方が差動信号であるならば、それは差動配線を使用することを意味するだけです。したがって、1つの出力だけを有するクロック信号のための微分配線を使用することはできない。

受信端での差動線対の間に整合抵抗を付加することができるか。

受信端の差動線路対の間の整合抵抗は、通常、加算され、差動インピーダンスの値と等しくなければならない。あなたはより良い信号品質を取得します。

7 .差動対の配線はなぜ近接して並列にすべきか

差動対の配線は、適切に近接して並列でなければならない。適切な近接性は、距離が異なるインピーダンスの値に影響を与えるためである。差動インピーダンスの整合性を維持するためにも並列化が必要である。つの線がより近いかより遠い場合、差動インピーダンスは矛盾しています。

8 .実配線における理論的コンフリクトの取り扱い

モジュール/デジタル分離は右です。信号ルーティングには、堀を横切ることができないように注意を払わなければならず、供給された信号と帰還している電流経路があまりに大きくならないように注意しなければならない。

水晶発振器は模擬正帰還発振回路である。安定した発振信号を有するためには、ループ利得及び位相の仕様を満たす必要がある。しかし、このシミュレートされた信号の発振仕様は、接地ガードトレースを追加しても干渉が完全に分離されない場合がある。そして、あまりに遠く離れて、グランドプレーンのノイズは、また、正帰還発振回路に影響を及ぼす。したがって、水晶発振器とチップの間の距離をできるだけ近くにしてください。

高速ケーブルとEMI要件の間には多くの競合がある。しかし、基本的な原理は、EMIによって加えられる抵抗キャパシタンスまたはフェライトビーズのため、信号のいくつかの電気的特性が仕様を満たさないようにすることができないということである。したがって、高速信号層化のような配線及びPCB積層技術を配置することによって、EMI問題を解決または低減することが最善である。最後に、抵抗キャパシタンスまたはフェライトビーズを用いて信号の損傷を低減した。

9 .マニュアル配線と高速信号の自動配線の矛盾の解決法

今日の強力なケーブルソフトウェアの自動キャララーのほとんどは、巻線モードと穴の数を制御するための制約を設定している。EDA企業は時折、異なるエンジン機能と制約設定プロジェクトを持っています。例えば、蛇行蛇がどのように蛇行しているのかを制御するのに十分な制約があるかどうか、差動ペアの間隔を制御できるかどうかは、配線の自動配線が設計者の考えに合致する方法に影響する。また、配線を手動で調整することの難しさは、巻き取りエンジンの能力に関するものである。例えば、ワイヤの押し付け能力、孔の押し付け能力、銅線へのワイヤの押し付け能力等によって、強力なケーブルエンジン能力の選択が解決策である。

10 .テストクーポン。

テストクーポンは、製造されたPCBの特性インピーダンスが時間領域反射計(TDR)を使用することによって設計要件を満たすかどうかを測定するために使用される。一般的にインピーダンスを制御するには、1つのラインと2つのケースに違いがあります。したがって、テストクーポン上の線幅と線間隔(差動ペア)は、制御するラインと同じであるべきです。最も重要なことは、測定時のグランドポイントの位置です。接地リードのインダクタンスを低減するために、TDRプローブの接地場所は、通常、測定信号のプローブ先端に非常に近い。したがって、テストクーポン上の測定信号点と接地点の間の距離は、使用済みプロービングロッドと一致する必要がある。

11 .マイクロストリップラインモデルを使用して、パワープレーン上の信号線の特性インピーダンスを計算できるか。電源と接地面の間の信号はストリップラインモデルを用いて計算できるか?

そう、特性平面を計算するとき、パワープレーンとグランドプレーンは基準面と考えられなければなりません。例えば、4層のプレート:トップ層-パワー層-層-底層。このとき、最上層配線特性IMPEのモデルは、パワープレーンを基準面とするマイクロストリップラインモデルである。

12. イン 高速PCB設計, 信号層の空白領域, しかし、複数の銅を分配する方法?

一般に