イーサネットは1970年代に生まれた, そして、我々は今日それを知らない. それは現代生活の隅々に現れた. おそらく、それはそれを神秘的にするその遍在性のためです. 今日, 編集者 サーキットボードファクトリー 角度の1つは、その謎を明らかに.

我々が今日使用するネットワークインターフェースはすべてのイーサネットインターフェースです, ほとんどのプロセッサは現在イーサネットインターフェースをサポートしている. 現在, イーサネットは主に10 M, 10/100 m, 料金に応じて1000 m. 10 Mアプリケーションは非常に少ない, そして、彼らは基本的に10に置き換えられます/100 m. 現在, 当社の製品のイーサネットインターフェイスの種類は主にツイストペアRJ 45インターフェイスを採用, そして、それは基本的に産業管理分野で使われます. 産業管理分野の特殊性により, 我々は非常にイーサネットデバイスの選択に精通している PCB設計. ハードウェアの観点から, the Ethernet interface circuit is mainly composed of MAC (Media Access Controlleroler) control and physical layer interface (Physical Layer, PHY). ほとんどのプロセッサはイーサネットMAC制御を含む, 物理層インタフェースを提供しない, それで、外部の物理的なチップはイーサネットアクセス・チャンネルを提供するために必要です. このような複雑なインターフェース回路に直面, すべてのハードウェアエンジニアは、ハードウェア回路がPCB上でどのように実装されているか知りたいと思う.

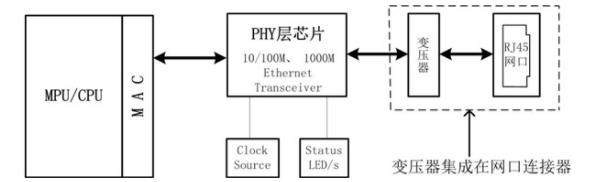

イーサネットの典型的なアプリケーションを示す. 我々 PCB設計 基本的にレイアウトされ、このブロック図に従ってルーティングされます. イーサネット関連のレイアウトとルーティングの主なポイントを詳細に説明するために、このブロック図を使用します.

イーサネットの典型的なアプリケーション

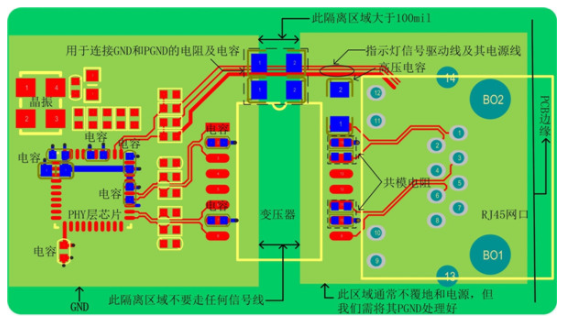

1. 図2 PCBレイアウト そして、ネットワークポート・コネクタの基準回路の配線ダイヤグラムは、ネットワークポートコネクタ. 以下の図2はイーサネット回路のレイアウトと配線に注意を要するポイントを紹介する.

Figure 2 PCBレイアウト and wiring reference of the circuit where the transformer is not integrated in the network port connector

RJ 45とトランスとの距離はできるだけ短いはずです。水晶発振器は、インターフェース、PCBおよび他の高周波デバイス、トレースまたは磁気コンポーネントのエッジから遠く離れているべきです。PHY層チップと変圧器との間の距離は、できるだけ短くなければならない。全体的なレイアウトを考慮すると、これは満足するのがより難しいかもしれません、しかし、それらの間の最大距離はおよそ10~12 cmです。デバイスのレイアウトの原理は、通常、信号の流れ方向に従って配置され、回避する必要はありません

b)phy層チップのパワーフィルタはチップの要求に従って設計される。通常、各電源端子にはデカップリングコンデンサが配置される。それらは信号の低インピーダンス経路を提供し、電源と接地面との間の共振を低減することができる。デカップリングおよびバイパスの役割を果たすので、コンデンサ、トレース、ビア、およびデカップリングおよびバイパスコンデンサのパッドからなるループ領域ができるだけ小さく、リードインダクタンスができるだけ小さいことを保証する必要がある

ネットワークポートトランスのPHY層のチップ側の中央タップのフィルタコンデンサは、最短のリード線と最小の分布インダクタンスを確実にするために変圧器ピンに可能な限り近くなければならない

ネットワークポートトランスのインターフェース側のコモンモード抵抗および高電圧コンデンサは、センター・タップの近くに置かれる。そして、ワイヤリングは短くて、厚い

変圧器の2つの側面はグラウンドを切断する必要がある。すなわち、変圧器のRJ 45接続ベースと二次コイルは別々の孤立グラウンドを使用し、分離領域は100ミル以上であり、この分離領域の下には電源および接地層は存在しない。このセグメンテーションプロセスは、一次側と二次側との間の分離を達成することであり、制御源からの干渉は、参照平面を通じて二次側に結合される

f)インジケータ光及び駆動信号線の電源ラインは、ループ領域を最小化するために互いに隣接してルーティングされる。インジケータ光と差動線は必要に応じて分離し、十分な距離に保つ必要がある。空間があれば、GNDで区切ることができます

g)GNDとpGNDとを接続するための抵抗とコンデンサをグランド分割領域に配置する。

2 .イーサネット信号線は、差動対(Rx - TRACE±、TX≒±)の形である。差動線は強いコモンモード除去と強い干渉防止能力を持ちます、しかし、配線が不適当であるならば、それは重大な信号完全性を持ってきます。性的問題。差動線の処理点を一つずつ紹介しましょう。

a)rx≠±tx tx±差動対を優先して,差動対を平行,等長,短距離に保ち,ビアとクロスを避ける。ピン分布、ビア、および配線スペースのような要因により、差動ラインの長さが不整合となり、タイミングがシフトされ、コモンモード干渉が導入され、信号品質が低下する。このため、差動対の不整合を補償してライン長と一致させる必要がある。長さ差は通常5 mil以内に制御される。補償原理は、長さ差が補償されるところです

b)速度要件が高い場合には,rx≒±txの微分インピーダンスペアのインピーダンス制御が必要となり,通常,インピーダンスは100 hz/10±10 %で制御される。

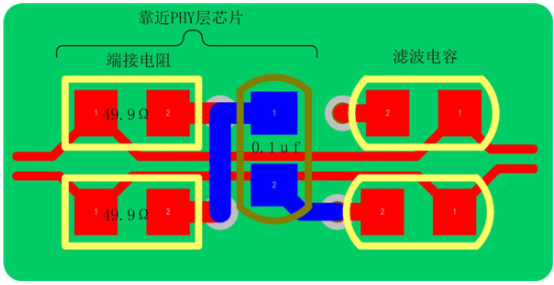

差動信号端子抵抗(49.9アンペア、いくつかのPHY層チップがない場合がある)は、PHY層チップのRx≒±Tx≒ピンに近接して配置されなければならず、これは通信ケーブルにおける信号反射をより良く除去することができる

D)差動ペア上のフィルタキャパシタを対称的に配置しなければならず、そうでなければ差動モードをコモンモードに変換し、コモンモードノイズを生じさせ、高周波ノイズの良好な抑制を行うために、ルーティング時にスタブはない。

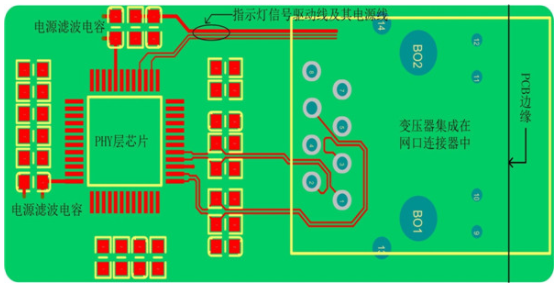

3. The PCBレイアウト そして、トランスに統合されたトランスを有するイーサネット回路の配線は、集積のないそれらより非常に単純である. 下の図3は PCBレイアウト and wiring reference diagram of the network port circuit with the integrated connector:

Figure 3 Network port PCBレイアウト and wiring reference diagram of the integrated connector

上記の図から分かるように、図3と図1との間の違いは、ネットワークポートトランスが省略され、その他がほぼ同じであるということである。違いは主にネットワークポート変圧器に反映されているコネクタに組み込まれているので、グランドプレーンは分割する必要はありませんが、我々はまだ連続したグランドプレーンに統合されたマシンのシェルを接続する必要があります。

イーサネットのレイアウトとルーティングはほぼ同じです. 良い PCBラウ Tは、回路性能を確実にすることができません, しかし、回路性能を改善する.