回路によって処理される信号の周波数は十分に高く、この周波数での伝送線路のインピーダンスは信号に影響を及ぼすのに十分である. この周波数で動作する回路を 高速回路.

1. 何が 高速回路

一般に、ディジタル論理回路の周波数が45 MHz〜50 MHzに達した場合には、この周波数以上で動作する回路は、電子システム全体の一部(例えば1/3)を占めていると一般に考えられている。実際、信号エッジの高調波周波数は、信号自体の周波数より高い。信号伝送の予期しない結果を引き起こす信号(または信号ジャンプ)の立ち上がりエッジと立ち下がりエッジである。したがって、回線伝搬遅延がデジタル信号駆動端の立ち上がり時間の1/2よりも大きい場合には、高速信号と考えられ、伝送線路効果を生じることが一般的に認められる。

信号の伝送は、立ち上がりまたは立ち下がりのような信号状態が変化した瞬間に発生する。信号は駆動端から受信端まで一定時間経過する。送信時間が立ち上がりまたは立ち下がり時間の1/2未満であれば、受信端からの反射信号は信号が変化する前に駆動端に到達する。逆に、信号が状態を変化させた後、反射信号は駆動端に到達する。反射信号が強い場合、重畳波形は論理状態を変化させることができる。

高速信号の決定

以上のことから、伝送線路効果の発生条件を定義したが、ライン遅延がドライブ端の信号立ち上がり時間の1 / 2より大きいかどうかを知ることができた。一般に、デバイスのマニュアルでは信号立ち上がり時間の典型的な値を与えることができ、信号伝搬時間は、PCB設計における実際の配線長で決まる。信号立ち上がり時間と許容配線長(遅延)との対応関係を以下の図に示す。

基板上の単位インチ当たりの遅延は0.167 nsである。しかし、多くのビア、多くのデバイスピン、および多くの制約がネットワークケーブルに設定されている場合、遅延は増加します。一般に、高速論理デバイスの信号立ち上がり時間は約0.2 nsである。基板上にgaasチップがある場合,最大配線長は7.62 mmである。

TRは信号立ち上がり時間、TPDは信号線伝搬遅延である。trが4 Tpdである場合、信号は安全領域に落ちる。2 tpdのアノイリックtrが4 Tpdの場合,信号は不確定領域に落ちる。tr≒2 tpdならば、問題領域に信号が落ちる。不確実な領域や問題領域に陥る信号については,高速配線法を用いるべきである。

簡単なレイアウト設計は手で実現でき,複雑なレイアウト設計はコンピュータ支援設計(cad)の助けで実現する必要がある。優れたレイアウト設計は、生産コストを節約し、良好な回路性能および放熱性能を達成することができる。

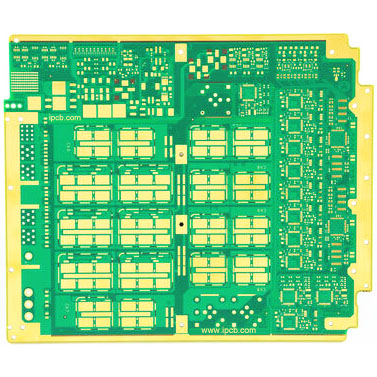

上記は 高速回路基板, IPCBも提供 PCBメーカー and PCB製造 テクノロジー