LVDS 高速信号PCB 配線 requirements:

1. トランシーバは、ボード上の高速信号トレースの長さを減少させるために可能な限りコネクタに近いはずである.

2. 差動線路の幾何学的寸法は、差動インピーダンスによって決定される. LVDSは100オームマッチングを内蔵, 差動線インピーダンスは約100オームで制御される, そして、単一の線インピーダンスは約50オームである.

3. コモンモード除去比を改善するのを助けるために、差動ライン間の距離をできるだけ小さくする.

4. 面内配線, 差動ワイヤ対を接地線と分離する方がよい. グランドワイヤーがなければ, 差動線対の間の距離は、差動線20間の距離の2倍以上でなければならない.

5. TTL/CMOS信号線はLVDS信号線から遠く離れていなければならない, そして、距離は少なくとも3つの差線間の距離でなければならない.

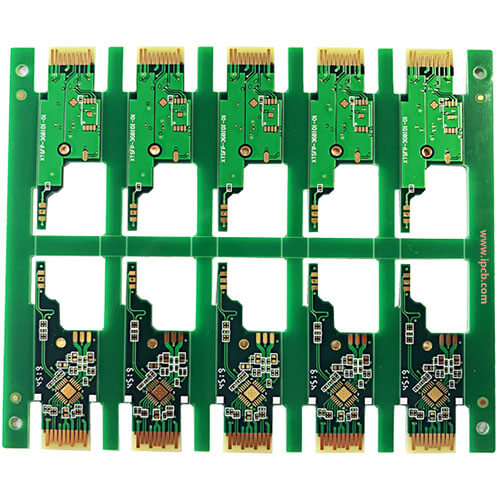

上記はLVDSの要件の導入です 高速信号PCB wiring. IPCBも提供されて PCBメーカー and PCB製造 テクノロジー. 6. LVDS差動信号線は、長さで厳密に等しくなければなりません.

7. 地面と電力面を横切る配線を避ける.

8. 90度回転を避ける.

9. ビアの数を最小にする.

10. トレースインピーダンスの連続性を維持する, 隣接する層の配線は垂直に交差する必要がある.

11. LVDSデバイスの各々の電源ピンは、厳しく切り離されなければなりません.

配線戦略を決定するために各ボードの実際の状況を考慮. 高速トランシーバはコネクタに近い, そして、伝送線上の高速信号の減衰を減らすために、配線はできるだけ短い. より細く長い跡, 減衰が大きい, したがって、高速LVDSのトレース幅は. 差動線の間の距離は、8マイル, そして、接地線は、差動線対間に追加され得る, そして、いくつかの地面のビアは、接地線上の距離で作られるべきである. ボードルーティングが難しいなら, 短い高速ルーティングの場合, 差動線対間の距離は、ルーティングのクロストークを低減するために、16ミルを超えることができる. 後方クロストークが前方クロストークより大きいので、受信および送信線は分離されるべきである. Veriestの測定ツールは弱い, そして、高速線のアーク角度が進むとき、差動線の等しい長さを制御することは、難しい, そして、線は鈍角で発送されることができます.