無線周波数(RF)PCB基板設計は、その理論上の不確実性から「ブラックアート」としてよく記述されるが、このような観点は部分的に正しいだけであり、多くのRF基板設計ガイドラインが遵守したり無視したりするべきではない。しかし、実際の設計に関わる場合、真のコツは、様々な設計制約によりこれらのガイドラインや法律を正確に実施できない場合に、どのように妥協するかである。もちろん、インピーダンスとインピーダンスの整合、絶縁材料と積層板、波長と定在波を含む多くの重要な無線周波数設計テーマが議論に値するが、本文は無線周波数板の遮断設計に関連する様々な問題を重点的に討論する。今日の携帯電話のデザインはすべてのものをさまざまな方法で統合しており、無線周波数板の設計には不利である。この業界は現在、競争が激しく、さまざまな機能と規模とコストを組み合わせる方法を探しています。アナログ、デジタル、RF回路は、それぞれの問題領域を分離するための空間がほとんどなく、コストの観点からレイヤの数は通常減少します。驚くべきことに、1つの多目的チップは1つの非常に小さなチップに複数の機能を統合することができ、RF、IF、アナログ、デジタル信号が非常に緊密に配置されているが、一般的には電気的には無関係である。配電はデザイナーにとって悪夢かもしれないが、回路の異なる部分は必要に応じて時間を共有し、ソフトウェア制御スイッチを通じて電池の寿命を維持する。これは、あなたの携帯電話には5~6個の動作電源が必要になる可能性があることを意味します。

無線周波数配置の概念

無線周波数配置を設計する際には、高出力無線周波増幅器(HPA)を低雑音増幅器(LNA)からできるだけ分離し、簡単に言えば、高出力無線周波送信回路を低電力無線周波受信回路から遠ざけることを優先しなければならないいくつかの一般的な原則がある。もしあなたのPCBに大きな物理空間があれば、あなたは簡単にそれをすることができますが、通常、PCBには多くのコンポーネントがあり、空間が小さいため、これは通常不可能です。PCBボードの両側に置いたり、同時に作業するのではなく交互に作業させたりすることができます。高出力回路は、RFバッファ及び電圧制御発振器(VCO)を含むこともある。穴が開いていないPCB上の高電力領域に少なくとも1つの完全な接地があることを確認します。もちろん、銅は多ければ多いほどいいです。後で、必要に応じてこの設計原則を打破する方法と、それによる問題を回避する方法についてお話しします。チップと電源のデカップリングも非常に重要で、この原則を実現するいくつかの方法については後でお話しします。無線周波数出力は通常、無線周波数入力から遠ざかる必要があり、後で詳細に議論します。敏感なアナログ信号はできるだけ高速デジタル信号とRF信号から離れなければならない。

分割方法

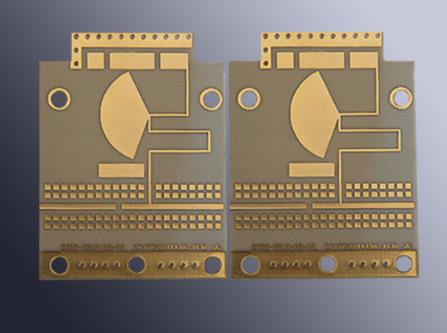

設計パーティションは物理パーティションと電気パーティションに分割できます。物理パーティションは主にコンポーネントの配置、方向、シールドなどの問題に関連し、電気パーティションは、配電、RFトレース、感受性回路および信号、および接地のためのパーティションに分解され続けることができる。まず物理的なパーティション化についてお話しします。素子配置は無線周波数設計を実現する鍵である。1つの効果的な技術は、まず無線周波数経路上に位置するコンポーネントを固定し、入力を出力から遠ざけ、コンポーネントをできるだけ分離するために無線周波数経路の長さを最小化するためにそれらの方向を調整することである。電力回路と低電力回路。有効なプレート積層方法の1つは、主接地面(主接地)を表面層の下の第2層上に配置し、できるだけ多くの表面層上でRF線を運転することである。RF経路上のビア寸法を減少させることは、経路インダクタンスを減少させるだけでなく、主接地上のゴースト溶接点を減少させ、RFエネルギーがスタック内の他の領域に漏れる機会を減少させる。物理空間において、多段増幅器のような線形回路は通常、複数のRF領域を互いに分離するのに十分であるが、デュプレクサ、ミキサ、IF増幅器/ミキサは常に複数のRF/IFを有する。信号は互いに干渉するので、この影響を最小限に抑えることに注意しなければならない。RFとIFトレースはできるだけ交差し、できるだけそれらの間に接地空間を残すべきである。正確な無線周波数ルーティングはPCB全体の性能にとって非常に重要であり、それは携帯電話PCB設計において、要素配置が通常ほとんどの時間を占める理由である。携帯電話PCBでは、通常、LNA回路をPCBの片側に置き、高電力増幅器を他方側に置き、最後にデバイスアンテナ上のデュプレクサを介して同じ位置のRF側とベースバンド処理に接続することができる。直通孔が回路基板の一方の側から他方の側に無線周波数エネルギーを移動させないようにするには、いくつかの技術が必要であり、一般的な技術は両側にブラインドビアを使用することである。スルーホールの有害な影響は、PCBの両側にRF干渉のない領域にスルーホールを配置することによって最小化することができる。

複数の回路ブロック間の十分な分離を確保することはできない場合があり、この場合、RF領域におけるRFエネルギーを遮蔽するために金属遮蔽を考慮しなければならないが、金属遮蔽は自己コストや組立コストが非常に高価であるなどの問題もある。不規則な形状を有する金属シールドは製造過程で高精度を確保することが困難であり、矩形または四角形の金属シールドは部品のレイアウトを制限し、金属シールドは部品の交換と故障の位置決めに不利である、金属シールドは床に溶接しなければならず、コンポーネントと適切な距離を維持しなければならないため、貴重なPCBボード空間を占有することができます。シールドカバーの完全性をできるだけ確保することが重要です。金属シールドカバーに入るデジタル信号線はできるだけ内層に向かうべきであり、配線層の下のPCB板は接地層である。RF信号線は金属シールドの底部の小さな隙間と接地隙間の配線層から引き出すことができるが、隙間の周囲にできるだけ多くの接地が分布し、異なる層の接地は複数のビアを介して接続することができる。上記の問題があるにもかかわらず、金属遮蔽は非常に効果的であり、通常は重要な回路を隔離するソリューションである。また、チップ電源の適切な効率的なデカップリングも重要である。集積された線形線路を有するRFチップの多くは電源ノイズに非常に敏感であり、通常、各チップは4つまでのコンデンサと1つの分離インダクタを必要とし、すべての電源ノイズがフィルタリングされることを保証する)。

キャパシタの値は通常、その自己共振周波数と低リードインダクタンスによって決定され、C 4の値もそれに応じて選択される。C 3とC 2の値は、それ自体のピンインダクタンスにより相対的に大きいため、RFデカップリング効果は小さいが、低周波ノイズ信号をフィルタリングするのに適している。インダクタL 1は、電源線からチップへのRF信号の結合を防止する。すべてのトレースは潜在的なアンテナであり、無線周波数信号を受信したり送信したりすることができ、誘導無線周波数信号をキー配線から分離する必要があります。これらのデカップリングコンポーネントの物理的な位置も通常は重要です。これらの重要なコンポーネントのレイアウトの原則は、C 4はできるだけICピンに近づき接地しなければならず、C 3はC 4に近づかなければならず、C 2はC 3に近づかなければならず、ICピンはC 4に近づかなければならない。接続トレースはできるだけ短くなければならず、これらのコンポーネント(特にC 4)の接地端子は通常、次の接地面を介してチップの接地ピンに接続されなければならない。コンポーネントを接地層に接続するための貫通孔は、PCB上のコンポーネントパッドにできるだけ近づける必要があります。パッドのブラインドホールは接続線のインダクタンスを低下させ、C 1に接近するように誘導する。集積回路または増幅器は通常、オンドレイン出力を有するので、高インピーダンスRF負荷と低インピーダンスDC源を提供するためにインダクタを引き上げる必要がある。同様の原理は、インダクタ側で電源をデカップリングするのにも適している。動作するには複数の電源が必要なチップもあるため、チップの周囲に十分なスペースがない場合は、2~3セットのキャパシタとインダクタが必要になる可能性があります。インダクタは、中空変圧器を形成し、干渉信号を誘導するため、少なくとも1つのデバイスの高さと同じ高さになるか、直角に間隔を空けて相互誘導を減らす必要があるため、並列に接続されることは少ないことを覚えておいてください。

電気パーティションの原理は通常、物理パーティションと同じですが、他の要素も含まれています。現代の携帯電話の一部の部品は異なる電圧で動作し、ソフトウェアによって制御されて電池の寿命を延長している。これは、携帯電話が複数の電源を動作させる必要があることを意味し、より多くの隔離問題が発生しています。電源は一般的にコネクタに導入され、スイッチまたはボルテージレギュレータのセットを介して割り当てる前にすぐに切り離されて、プレート外のノイズをフィルタリングします。携帯電話のほとんどの回路にはかなり小さな直流電流があるので、トレース幅は通常問題ではありませんが、高電力増幅器の電源のためにできるだけ広い単独の高電流トレースを実行して、伝送電圧降下を最大限に減らす必要があります。過剰な電流損失を回避するためには、複数のビアが1つの層から別の層に電流を伝達する必要があります。さらに、高電力増幅器が電源ピンで十分にデカップリングされていない場合、高電力ノイズはプレート全体に放射され、様々な問題を引き起こす。大電力増幅器の接地は重要であり、通常は金属遮蔽が必要である。ほとんどの場合、RF出力をRF入力から遠ざけることも重要である。これは増幅器、バッファ、フィルタにも適用されます。最悪の場合、増幅器とバッファの出力が適切な位相と振幅で入力端にフィードバックされると、それらは自励発振する可能性がある。いずれの場合も、温度と電圧のいずれかの条件で安定して動作します。実際には、不安定になり、RF信号にノイズと相互変調信号を追加することがあります。

RF信号線がフィルタの入力端から出力端にループバックしなければならない場合、フィルタのバンドパス特性が大きく損なわれる可能性があります。入出力間で良好な分離を得るためには、まず、フィルタの周囲に接地を配置しなければならない。次に、接地はフィルタの下部領域に配置し、フィルタの周囲の主接地に接続しなければならない。フィルタを通過する必要がある信号線をフィルタピンからできるだけ遠ざけるのも良いアイデアです。また、プレートの上のどこにも接地しないように注意してください。そうしないと、知らないうちに起こりたくない結合チャネルが導入される可能性があります。図3は、このような接地方法を詳細に説明している。シングルエンドまたは平衡RF信号線を選択することができ、交差干渉とEMC/EMIに関する同じ原理もこれに適用されることがあります。適切に配線すれば、平衡RF信号線はノイズと交差干渉を低減することができるが、それらのインピーダンスは一般的に高く、ソース、トレース、負荷に一致するインピーダンスを得るために合理的な線幅を維持しなければならない。実際に配線するのは難しいかもしれません。バッファは、同じ信号を2つの部分に分割し、異なる回路、特にLOが複数のミキサを駆動するためにバッファを必要とする場合に使用することができるので、分離性を高めるために使用することができます。ミキサが無線周波数でコモンモード分離に達すると、正常に動作しなくなります。バッファは、異なる周波数でのインピーダンス変化をうまく分離することができ、回路が干渉しないようにすることができる。バッファは、駆動する必要がある回路の後ろに置くことができる設計において、バッファの入力信号レベルが相対的に低いため、基板上の他の回路の影響を受けにくい高出力トレースが短いため、バッファは駆動する必要がある回路の後ろに置くことができます。回路が干渉する。非常に敏感な信号や制御回路の多くは特に注意する必要がありますが、それらは本文の範囲を超えているので、ここでは簡単に議論するだけで、詳細には説明しません。

電圧制御発振器(VCO)は、絶えず変化する電圧を絶えず変化する周波数に変換する。これは高速チャネル切替のための機能であるが、制御電圧上の少量のノイズを微小な周波数変化に変換し、RF信号にノイズを増加させる。一般的には、この後、RF出力信号からノイズを除去することはできません。では困難はどこにあるのでしょうか。まず、制御線の所望の帯域幅はDCから2 MHzの範囲であり、そのような広い帯域でフィルタリングしてノイズを除去することはほとんど不可能である。第二に、VCO制御線は通常、周波数を制御するフィードバック回路の一部であり、多くの場合そうである。ノイズはどこにでもある可能性があるので、VCO制御線を非常に注意して処理しなければならない。RFトレースの下の接地がソリッドであり、すべてのコンポーネントが主接地にしっかりと接続され、ノイズを導入する可能性のある他のトレースから隔離されていることを確認します。また、VCOのRF出力は比較的高いレベルにあることが多く、VCO出力信号は他の回路と干渉しやすいので、VCOの電源が十分にデカップリングされていることを確認してください。実際、VCOは通常RF領域の末端に配置され、時に金属遮蔽を必要とする。

共振回路(1つは送信機、もう1つは受信機)はVCOに関連していますが、独自の特性もあります。簡単に言えば、共振回路は、VCOの動作周波数を設定し、音声またはデータをRF信号に変調するのに役立つ容量ダイオードを備えた並列共振回路である。すべてのVCO設計原則は共振回路にも適用される。共振回路は一般的にノイズに非常に敏感である。なぜなら、それらのコンポーネントの数は非常に多く、プレート上に広く分布し、通常は非常に高いRF周波数で動作するからである。信号は通常、チップの隣接ピン上に配置されるが、これらの信号ピンは比較的大きなインダクタとキャパシタと一緒に動作する必要があり、逆にこれらのインダクタがキャパシタと緊密に配置され、ノイズ感受性制御回路に接続されることが必要である。それを実現するのは容易ではない。自動利得制御(AGC)増幅器も問題が発生しやすく、送受信回路にAGC増幅器が存在する。AGC増幅器は一般的にノイズ除去に有効であるが、携帯電話が送受信信号強度の急速な変化を処理する能力はAGC回路がかなりの帯域幅を持つことを必要とし、これによりいくつかのキー回路上のAGC増幅器がノイズを導入しやすくなる。AGC回線を設計する際には、非常に短いオペアンプ入力ピンと非常に短いフィードバック経路に関連する良好なアナログ回路設計技術に従う必要があり、どちらもRF、IF、または高速デジタル信号トレースから離れなければなりません。また、良好な接地も不可欠であり、チップの電源はよく切り離さなければならない。入力端子または出力端子に長い電線を接続しなければならない場合は、出力端子では、通常インピーダンスがはるかに低く、インダクタンスノイズも発生しにくい。通常、信号レベルが高いほど、ノイズを他の回路に導入しやすくなる。すべてのPCB設計において、デジタル回路をアナログ回路からできるだけ遠ざけることは共通の原則であり、RF PCB設計にも適している。一般的なアナログ接地は、通常、信号線を遮蔽して隔離するための接地と同様に重要であり、問題は、遠見と注意深く計画しなければ、毎回この点ではほとんど無力であることです。そのため、設計の初期段階では、意図しない設計変更によって完成に近い設計が再構築されなければならない可能性があるため、綿密な計画、周到なコンポーネント配置、徹底的な配置評価が重要です。いずれにしても、このような不注意の深刻な結果はあなたの個人の職業発展にとって良いことではありません。また、RF回線をアナログ回線や非常に重要なデジタル信号から遠ざけてください。すべてのRFトレース、パッド、コンポーネントは、できるだけ接地銅を充填し、できるだけ主接地に接続しなければなりません。パンなどの微多孔性ビルディングボードは無線周波数回路の開発段階で有用であり、ビルディングボードを選択すると、希望する多孔性の数を無料で使用できます。そうしないと、通常のPCBに穴をあけると開発コストが増加し、大規模な生産時のコストが増加します。

RFトレースが信号線を通過しなければならない場合は、それらの間のRFトレースに沿ってプライマリ接地の接地に接続する層を配線してみてください。不可能な場合は、容量結合を最小限に抑えるために交差していることを確認し、各RFトレースの周りにできるだけ多くの接地を行い、それを主接地に接続してください。さらに、平行RFトレース間の距離を小さくすることにより、インダクタンス結合を低減することができる。ソリッドな1枚の接地面が直接表層の下に置かれ、効果を隔離します。少し丁寧な設計を経ても、他の方法も有効です。接地面を複数の部分に分割してアナログ、デジタル、RF回線を隔離しようとしましたが、結果に満足したことはありません。これらの個別の接地を通過する高速信号線が常にあるので、これは良いことではありません。PCBボードの各層には、できるだけ多くの接地を敷設し、主接地に接続します。トレースをできるだけ近くに配置して、内部信号と配電層上のパッドの数を増やし、接地接続ビアを表面上の分離パッドに配線できるようにトレースを調整します。小型アンテナのようにノイズを拾ったり注入したりするので、PCBボードの各層の自由接地は避けなければならない。