コンピュータ産業が1 Vで最高200 Aを届けることができるDC - DCコンバータに向かって、PCBボード レイアウト技術は、このチャレンジングな新興コンバータの要件を満たす必要がある。種々の配線欠陥の影響を比較する。回路における寄生インダクタンスの影響に焦点を合わせる。特にソースに関連するもの、ドレイン、スイッチングMOSFETのANDゲートを指す。私たちは PCBボード12 VのDCを取って、それを1に変えるDC - DCコンバータをテストすることのために、3 Vと20 Aまでの出力になる。我々は、アセンブリのためのプラグインボードを使用して、個々のまたは同時に同時に各MOSFET電極のインダクタンスを変更することができる。インダクタンス値を特別に設計した2インチボードのインダクタンスのパーセンテージとして使用することを選んだ。実際の値ではなく、配線の人は、特定のトレースの長さを知っていて、必ずしもそのインダクタンスの値を知らないからだ。

試験設計

これらの寄生インダクタンスの有効性を測定するためにコンバータ効率を使用した。これは、効率がDC-DCコンバータ性能の標準的な尺度であるからだ。試験は、mosfetドレイン、ソース、ゲートの各インダクタンス値の比例係数を調整し、変換効率を測定することにより同期整流器への影響を観測する。上記のいずれかの組み合わせを通じて、それらの間の関係を理解する。インダクタンステストボードは、43nHのインダクタンスを有し、典型的には0 %、25 %、50 %、100 %に設定される。実験では、インダクタンス試験ボードの寄生抵抗はほとんど効果がなく無視できる。寄生インダクタンスの有害な影響は周波数依存性であるので,我々は3つのプリセットスイッチング周波数で実験した。これにより、設計が通常のスイッチング周波数から将来においてより高い周波数に移動することが重要であることがわかる。電力回路では、電圧と電流のリンギングを避けるために、すべてのトレースの長さを短くしなければならず、基板の全体的なEMIを減少させ、回路(特にアナログ制御回路および関連コンポーネントのための)における「より安定した」コンポーネントに悪影響を及ぼすことを避ける。加えて、基準材料は、制御MOSFETのソースインダクタンスが、ソース電流降下時間の増加に非線形効果を有することを示し、結果として、より高い電力損失および低い変換効率をもたらす。上記の現象に加えて、ソース・インダクタンスもスイッチ・ノードでリンギングを生じることがありえる。

テスト回路と回路基板

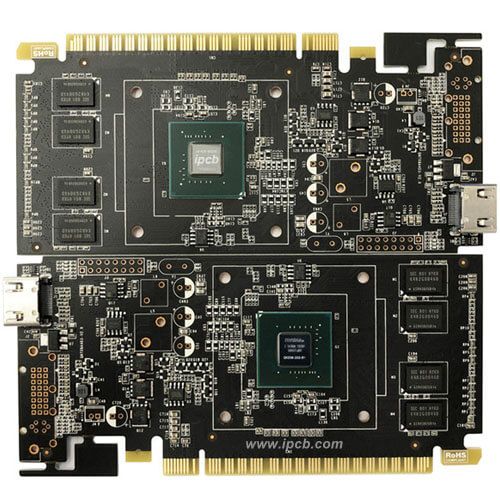

回路はオープンループで動作する同期整流トポロジーだ。これは、制御ループが回路性能に及ぼす影響を除外し、電力変換効率、特にMOSFET性能に焦点を合わせることを可能にすることだ。我々は、高いインダクタンス条件が特にスイッチノードで厳しいリンギングを引き起こすことができることを知っている。悪影響なしでこのリンギングを許容することができるゲートドライバICを選択してください。この4層の回路基板は、2つのオンスの銅材料を使用し、内側の2つの層は接地および電力面だ。配線時には良好な配線のルールをすべて観察しなければならない。

ゲートインダクタンスの効果

ゲートインダクタンスはスイッチング周波数300 khzでの効率にほとんど影響しない。600 kHzのスイッチング周波数では、ゲートインダクタンスの効果は、20 %の効率の1.2 %の変化で、より顕著だ。1 mhzでは、効率の劣化はほぼ完全に消失する。我々はこの理由を調査しておらず、共鳴係数がその損失を相殺する50 %の確率があると推測することができる。MOSFETゲートドライブの共振現象をさらに検討する必要がある。ゲートインダクタンスは制御と同期mosfetの効率にほとんど影響しないことを観測した。

ソースインダクタンスの効果

ソースインダクタンスは、効率に対してより顕著な効果を有する。場合によっては、MOSFETの温度が130°Cより大きいため、電流に達する前にテストを中止しなければならなかった。図5は、制御MOSFETの研究の結果を示す。これらの結果をより詳しく調べると、300 kHzの周波数と100 %のインダクタンスでは、MOSFETの温度が130℃程度を超えるため、DC−DCコンバータは十分に動作できないことがわかる。50 %インダクタンス、600 kHz、1 MHzでも同様だ。ソースインダクタンスによる効率劣化は、ソースインダクタンスなしよりも厳しいことが分かった。インダクタンスが50 %、電流が15 Aの場合、スイッチング周波数300 kHzでも効率が7 %低下する。インダクタンスが100 %の場合、効率は11 %に低下する。600 kHzと1 MHzのスイッチング周波数では、効果がより顕著であり、効率の低下は、ソースインダクタンスがないよりも厳しい。明らかに、低ソースインダクタンスであっても、特に周波数を変化させるために効率が低下する。

ドレインインダクタンス効果

ドレインインダクタンスは、極端な条件の下でMOSFETを破壊させるのに十分であるような厳しいリンギングを引き起こすことがある(図3)。また、効率に悪影響を及ぼす。効率は、異なる周波数での負荷電流とドレインインダクタンスの関数である。さらに、電流が15 A、300 kHz、50 %のインダクタンスでは、MOSFETの温度が130立方センチメートルを超えるためテストを中止しなければならない。同じ周波数で、100 %のインダクタンスで、リンギングがあまりに厳しいので、我々はどんな測定も得ることができなかった。300 kHz、12 Aでは、ドレインインダクタンスの50 %が0 %より7 %効率が悪い。MOSFETの高温により、15 aを超えるテストはできない。600 kHzでは、ドレインインダクタンスの50 %は、0 %より8.5 %低い効率である。MOSFETの温度が高すぎるので、テストは12.5 A以上では行えない。1 MHzではMOSFETの高温により5 A以上ではテストできない。

ゲートソースインダクタンスの効果

より大きなソースインダクタンスは、効率を著しく低下させる。ゲートインダクタンスに対する効率の基本的依存性を示した。小さなソースインダクタンスと組み合わせると、全体像は非常に明確になる。より大きなゲートインダクタンスは必然的に大きな電力損失をもたらす。この結果の解釈にはさらなる研究が必要である。基板の合理的なインダクタンス値の範囲内で、ドレインおよびソースインダクタンスを低減し、高いコンバータ効率を確保する必要があると述べることができる。シミュレーションにより,ゲートとソースのインダクタンスはmosfetのゲート‐ソース間容量と共鳴する。HS−FETがゲートソースをオフにすると、キャパシタはこれらの誘導経路を通って放電する。MOSFETがオフになった後、インダクタンスはゲート電流を流れ続け、ゲートソースキャパシタンスを逆充電する。この電荷は、同様にして放電し、HS−FETのゲート−ソース間電圧を反転させる。ディップに応じて、HS - FETは、巨大な短絡で再びオンにすることができます。このような高いゲートインダクタンスで効果が厳しくなる。場合によっては、第2の短絡効果さえ見ることができる。この共振回路の一部として、ソースインダクタンスも第2の方法で動作することができる。短絡電流が発生すると、ソースインダクタンスは短絡電流のdi/dt(時間に対する電流変化率)を制限し、それによって損失を制限する。ソースインダクタンスもゲートソース電圧に負帰還を生じ、短絡回路を制限する。これらの効果は特に寄生ゲートインダクタンスが高い場合に生じる。高効率のためには、この効果は設計によって回避されるべきだ。すなわち、ゲートインダクタンスを最小にするために慎重に設計されなければならない。

ソースHS‐ソースLSインダクタンスの影響

寄生源インダクタンスの位置が効率に及ぼす影響を調べた。その結果、制御FETは、寄生ソースインダクタンスループの同じ量の同期FETよりもその効率に対してより大きな効果を有する。この理由は、制御FETのVDSが同期FETのVDS(同期FETの順方向電圧降下が小さい)の方がコンバージョン過程においてスイッチング損失が大きいためだ。加えて、FETゲート・ドレイン電圧への寄生インダクタンスのフィードバックは、HS-FETリーク電流全体に大きな影響を与える。比較によって、寄生FETインダクタンスの効果は、同期FETのボディダイオードによってバイパスされることができるので、部分的にのみだ。

並列MOSFETの効果

MOSFETが並列接続されている場合、個々のMOSFETループが多くの場合、同じ寄生を有することはあり得ない。MOSFETドレインループにおける付加インダクタンスが効率に及ぼす影響を調べた。DC - DCコンバータのスイッチングMOSFETの効率に及ぼす寄生インダクタンスの影響を実験的に示す。結論は以下の通りのようになる。ドレイン回路に同様のインダクタンスが続く。我々のブレッドボードで、ゲート回路インダクタンスに重大な影響はなかった。効率の低下は、コンバータのスイッチング周波数と密接に関連する。効率の低下は負荷電流と大いに関係がある。ソースおよびドレイン回路の寄生インダクタンスの存在下で、負荷電流が大きいほど, 効率が低下する。今日のDC - DCコンバータアプリケーションで、電力システムPCBのルーティング時に特別な注意を払わなければならない。特にスイッチングMOSFET周辺、多層基板を使用する利点の1つは、できるだけ多くの電流をできるだけ沈降させることによって寄生抵抗およびインダクタンスを低減することである. これは寄生インダクタンスに起因する抵抗損失と損失を低減する。高周波DC‐DCコンバータの設計、ソースおよびドレイン回路に関連する多くの寄生インダクタンス問題がある。 一つ目はパッケージインダクタンスです, そして、スイッチングMOSFETのために最近導入された低インダクタンスパッケージを使用することが可能である。第2の項目は PCBボード多層を用いて制御しなければならない PCBボード トレースインダクタンスの減少だ。これは、設計者がより速い動的応答と成功した高周波設計のためにより少ないコンデンサを使用することを可能にする。同期FETのインダクタンスは、制御FETループのインダクタンスよりも全体効率に対して効果が少ないので、設計によって回避することができない寄生インダクタンスを同期型FETループに移動させるべきだ。注:低デューティサイクルで, 同期型FETループの寄生抵抗は効率を大幅に低減できる。並列MOSFETを避ける。MOSFETを並列に置き換える方法は、余分な位相を追加したり、より良いMOSFETを使用することだ。並列化が避けられないなら、並列MOSFET用、電気的対称性は、同じ電流分布と同じスイッチング時間を得るために設計で保証されなければならない。

(株)iPCBはPCB&PCBAの設計、製造販売及びこれらの付随業務の電子相関事業を手掛けています。弊社の詳細はリンク:https://www.ipcb.jp/ 或いはhttps://www.ipcb.com/jp をご覧ください。