デジタル論理の頻度ならば PCBボード 45 MHz~50 MHzを超える, and the circuit working above this frequency has accounted for a certain amount of the entire electronic system (for example, 1/3), 通常、高周波回路と呼ばれる. 高周波回路設計は非常に複雑な設計プロセスである, そして、そのルーティングは、全体の設計に重要です.

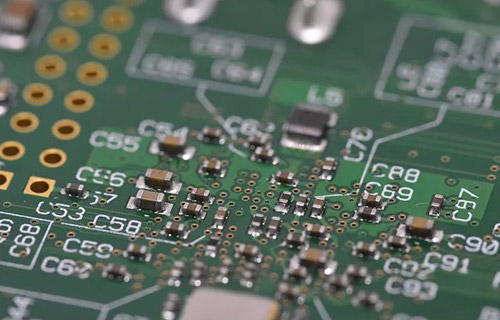

多層基板配線2

高周波回路は集積度が高く配線密度が高い傾向がある。多層基板の使用は配線のためだけでなく,干渉を低減する有効な手段である。PCBレイアウト段階において、ある層の層を有するプリント基板のサイズの妥当な選択は、中間層を完全に使用してシールドを設定し、最寄りの接地をより良く達成し、効果的に寄生インダクタンスを低減し、信号の伝送長を短くすることができる。信号交差干渉などを大幅に減少させる。これらの方法の全ては、高周波回路の信頼性に有益である。いくつかのデータは,同じ材料を使用した場合,4層板のノイズが両面板の20 dbより低いことを示した。しかし同時に、問題もある。PCBボードの半層数が高くなるほど、製造プロセスが複雑化し、単価が高くなる。これはPCBボードレイアウトを行う際に適切な層数を選択する必要があります。合理的なコンポーネントのレイアウト計画を実行し、デザインを完了するために正しいルーティングルールを使用します。

(2)高速電子装置のピン間のリードリード不良は、よりよい

高周波回路配線のリード線は全て直線であり、ターンする必要がある。彼らは45度の折れ線やアークでターンすることができます。この要件は、低周波回路における銅箔の固定強度を向上させるためだけに使用されるが、高周波回路ではこの要件が満たされる。しかし、高周波信号の外部発光と相互結合を低減することができる。

(3)高周波回路装置のピン間のリードをより短くすること

信号の放射強度は、信号線のトレース長に比例する。高周波信号リードが長いほど、それに近い成分に結合する方が容易である。したがって、クロック、水晶発振器、DDRデータ、LVDS線、USB線、HDMI線などの高周波信号線については、できるだけ短くする必要がある。

(4)高周波回路装置のピン間のリード層間の交叉は少ない

いわゆる「リードの中間層交替が悪いほど、」とは、部品接続プロセスで使用されるより少ないビアがよりよいことを意味する。データによると、1つのビアは、約0.5 pFの分布容量をもたらすことができ、VIAの数を減らすことにより、速度を大幅に改善し、データエラーの可能性を低減することができる。

信号線の近接した平行トレースに起因する「クロストーク」に注目する

高周波回路配線では、信号線の並列配線によるクロストークに注目する必要がある。クロストークは直接接続されていない信号線間の結合現象を指す。高周波信号は伝送線路に沿って電磁波の形で伝送されるので、信号線がアンテナとして作用し、電磁界のエネルギーが伝送線の周囲に放出される。クロストークと呼ばれる。PCB層のパラメータ、信号線の間隔、駆動端と受信端の電気的特性、および信号線の終端方法は、すべてクロストークに影響を与える。従って、高周波信号のクロストークを低減するためには、配線が許容される条件では、配線間に接地線やグランドプレーンを挿入する必要がある。これは分離の役割を再生し、クロストークを減らすことができます。信号線の周囲の空間内に時変電磁場が存在する場合には、平行分布を回避できない場合には、並列信号線の反対側に「グランド」の大面積を配置して干渉を大幅に低減することができる。配線空間が許容されると、隣接する信号線間の間隔が大きくなり、信号線の平行長が短くなり、並列にではなく鍵信号線に垂直になる。同じ層の平行なトレースがほとんど避けられないならば、2つの隣接した層で、痕跡は互いに垂直に向けられなければなりません。ディジタル回路では、通常のクロック信号は、高速エッジ変化を有する信号であり、外部クロストークが大きい。したがって、設計においては、クロック線を接地線で囲む必要があり、より多くの接地線孔を設けて、分布容量を低減し、クロストークを低減させる必要がある。高周波信号クロックの場合は、低電圧差動クロック信号を使用してグランドをラップしようとする。地面パンチングの整合性に注意を払う。未使用の入力端子をサスペンドするのではなく、電源を接地したり、電源に接続する(電源も接地されている)。このようにしてクロストークを除去することは、時々効果的であることがある。

集積回路ブロックの電源ピンに高周波デカップリングコンデンサを加える

高集積デカップリングコンデンサは、各々の集積回路ブロックの電源ピンに添加される。パワーピン上に高周波デカップリングコンデンサを加えることにより、パワーピン上の高周波高調波による干渉を効果的に抑制することができる。

高周波デジタル信号の接地線とアナログ信号の接地線を分離する

アナログ接地線、デジタル接地線等を共通接地線に接続する場合は、高周波チョーク磁性ビーズを適宜の場所で接続または直接分離、単点配線に用いる。高周波デジタル信号の接地線の接地電位は、一般的に矛盾しており、2つの間の電圧差がしばしばあるデジタル信号グランド線とアナログ信号グランド線とが直接接続されると、高周波信号の高調波がグランド線結合を介してアナログ信号と干渉する。したがって、通常の場合には、アナログ信号の高周波デジタル信号と接地線の接地線を孤立させておく必要があり、適切な位置に1点で接続することができ、あるいは高周波チョーク磁性ビーズの相互接続を用いることができる。

トレースによって形成されるループを避ける

すべての種類の高周波信号は、できるだけループを形成しないでください。それを避けることができないならば、ループ領域はできるだけ小さく保たれなければなりません。

良好な信号インピーダンス整合を確保しなければならない

信号伝送の過程において、インピーダンスが一致しない場合、信号は伝送路に反映され、反射は複合信号をオーバーシュートとし、論理閾値の近くで信号を変動させる。反射を除去する基本的な方法は、送信信号のインピーダンスをよく一致させることである。負荷インピーダンスと伝送線路の特性インピーダンスとの差が大きいため、反射が大きくなる。したがって、信号伝送線路の特性インピーダンスは、できるだけ負荷インピーダンスに等しくなければならない同時に、PCBに注意を払う。ボード上の伝送ラインは、突然の変更またはコーナーを持ってはいけません。伝送線路の各点のインピーダンスを連続的に保つようにし、そうでなければ伝送線路の区間間に反射を生じる。これは、高速PCBボードを配線するときに以下の配線規則を従わなければならないことを必要とする。USB信号のための差動トレースは、10ミリメートルのライン幅、6マイルのライン間隔、およびグランドと信号線の間の6ミル間隔で、必要である。HDMI配線規則HDMI信号差動トレースが必要であり、線幅は10 mil、線間隔は6 mil、各2つのHDMI差動信号対間の間隔は20 milを超える。LVDS配線規則LVDSシグナル差動トレースは、7マイルの線幅と6マイルの線間隔で、必要です。目的は、HDMIの差動信号対インピーダンスを100+−15 %オームであるように制御することである。DDRルーティングルールDDR 1配線は、信号ができるだけ正孔を通過しないことを必要とし、信号線は等しい幅であり、線は等間隔である。配線は、信号間のクロストークを低減するために2 W原理を満たす必要がある。以上のDDR 2の高速デバイスには、高周波データも必要となる。ラインの長さは、信号のインピーダンス整合を確保するために等しい。

10 .シグナル完全性の維持

信号伝送の完全性を維持し、接地線分裂に起因する「接地バウンス現象」を防止する PCBボード.