SOPパッケージは電子部品の形式であり、表面実装パッケージの一種であり、比較的によく見られるパッケージ材料は:セラミックス、ガラス、プラスチック、金属などであり、現在基本的にプラスチックパッケージを使用し、主に各種集積回路に使用されている。

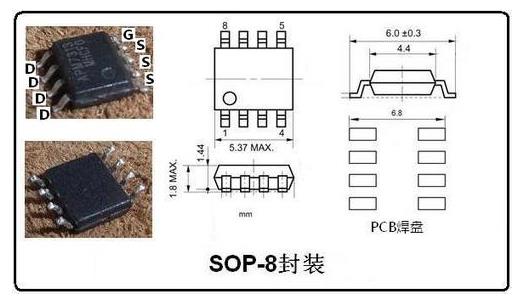

SOPデバイスはSOIC(Small Outline Integrated Circuit、小外形集積回路)とも呼ばれ、リード線の中心距離は1.27 mmで、材料はプラスチックとセラミックスの2種類があり、SOPはSOLとDFPとも呼ばれている。SOPパッケージ標準にはSOP-8、SOP-16、SOP-20、SOP-28などがある。SOPピン数を数えると、業界内では「P」が省略され、so(Small Out Line)と呼ばれることが多い。

SOP(小形パッケージ)小形パッケージとは、カモメの羽の形をしたL字型のリード線がパッケージの両側から1つの表面を引き出してパッケージを貼り付けることを指す。フィリップスは1968~1969年に小型外形パッケージ(SOP)を開発した。その後、徐々にSOJ(ピン型小外形パッケージ)、TSOP薄型小外形パッケージ、VSOP(非常に小型外形パッケージ)、SSOP(シンSOP)、TSSOP(薄型シンSOP)とSOT(小型外形トランジスタ)、SOIC(小型外形集積回路)などが派生した。

ピン数星型が40を超えない分野では、SOPは最も広範な表面貼付パッケージを応用し、典型的な書き込みピンの中心距離は127 mm(150 mi)、その他は0.65 mm、05 mmである。書き込みピン数が8~32個より大きい、組み立て高さが1.27 mm未満のSOPはTSOPとも呼ばれる。

1.SOPエイジングシートの特徴

二重接点技術、接触安定。

シートカバーは特殊なエンジニアリングプラスチックを採用し、強度が高く、耐用年数が長い。

弾性片は輸入ベリリウム銅材料を採用し、インピーダンスが小さく、弾性がよく、使用寿命が長い。

â:メッキ層を厚くし、接点を厚くしてメッキし、接触が安定し、接触インピーダンスが超低で、抗酸化度が高い。

間隔が0.5、0.635、0.65、1.27 mmの標準パッケージチップに適しています。

2.SOPエージングソケットパラメータ

ソケット本体:PEI

弾片材料:ベリリウム銅

弾片めっき層:ニッケル金

動作圧力:最小0.9 KG、PINが多いほど、圧力が大きい

絶縁インピーダンス:1000 M±500 V DC

墊¥最大電流:1 A

操作温度:-40水分~ 155

機械寿命:15000回

SOP包装技術は表面貼付(SMD)包装製造技術である。SOPパッケージプロセスは、まずICチップを薄くし、線を引き、その後、ICチップをSOPリードフレームのキャリアに貼り付け、ベーキング、ボンディング(リードボンディング)を経て、チップとチップ、チップとインナーピンを接続させ、その後、成形後、チップとリード、インナーピンなどをカプセルボンディングし、最後に後硬化、マーキング、マーキング、電気鎮、ダイシング成形、テストを経て、SOP生産プロセス全体を完成する。

SOP包装プロセス標準プロセス

(1)薄型化:金裏地(銀裏地)を有する光ディスクは薄型化しない。非金(銀)バッキングディスクは、元のディスクの粗研削及び細研削方法により薄肉化される。

(2)スクライブ:包装の必要に応じて、通常の青色フィルム、DAF(DieAttach film)フィルム、CDAF(Conductive DieAttach film)フィルムまたはUV(Ultraviolet Rays Fim)フィルムを選択することができる。現在、鋼刃片は主に機械切断またはレーザー切断技術を採用している。

(3)接着剤:接着フィルム接着剤、接着フィルムシート及びUVフィルム上芯を用いた方法。

(4)接着:すなわち、配線、溶接線用金線、銅線、銀合金線とアルミニウム線などの材料は、超音波熱接着技術を採用する。

(5)プラスチック密封:SOPは射出成形技術を採用する。

(6)後硬化:オーブンを用いて高温で成形品を焼く。

(7)マーキング:レーザーマーキングマシンを用いて製品正面に製品標識(以前は「印刷」と呼ばれていた)を生成する。

(8)電気めっき:純スズ電着技術を採用する。錫めっき後、製品は焼く必要があります。

(9)切断成形:切断成形一体機の上で、先に廃棄物を流して、中間の棒を切り落として、それから成形して、自分で人の管を強くします。

(10)試験:カニューレまたは編組一体化試験技術を採用する。

SOPパッケージは操作過程の標準化、規範化だけでなく、効率と品質の二重保障でもある。SOPパッケージにより、企業は従業員一人一人が既定の基準とプログラムに従って作業できるようにすることができ、人為的な要因によるエラーと偏差を減らすことができます。