レイアウトはPCB設計の重要な部分です、そして、それはPCB設計全体の中で最も時間がかかる部分です。エンジニアは、面取り規則、3 Wルールなどのいくつかの基本ルールに従う必要があります。

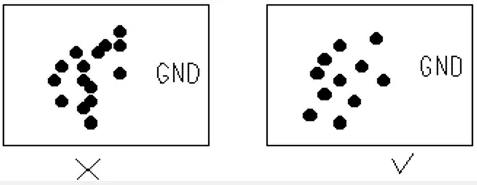

接地回路規則

対応する接地回路規則は、信号のループ領域を最小にするために実際にある, いくつかの重要な信号でしばしば見られる, such as clock signal and synchronous signal;

クロストークはPCB上の異なるネットワーク間の長い並列配線に起因する相互干渉を意味する, 主に平行線間の分布容量とインダクタンスに起因する. The main measures to overcome crosstalk are as follows:

The

概して

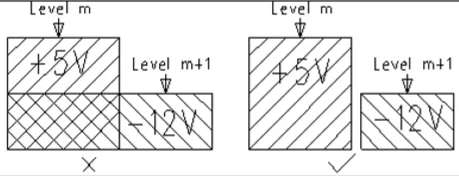

デバイス分離ルール

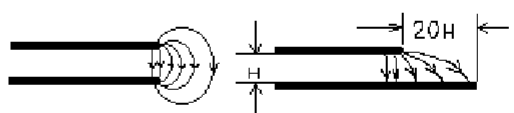

電力層と層の間の電場は可変であるので、電磁干渉はプレートの縁から放射する。それはエッジ効果と呼ばれます。

解決策は、電力層を縮小することである, 電界がグランドプレーンの範囲でのみ実行されるように. Taking an H (dielectric thickness between power supply and ground) as a unit, 電界が20 hによって凹んでいるならば, 電界の70 %は接地面のエッジに制限され得る, また、98 %以内の電界を制限することができます.

PCBレイアウトの他の注意

一般規則

1.1のデジタル、アナログとDAA信号配線域は、PCBにあらかじめ分割されます。

1.2のデジタルおよびアナログコンポーネントおよび対応する配線は、可能な限り切り離されて、それらのそれぞれの配線領域に置かれる。

1.3高速デジタル信号ルーティングは可能な限り短くする。

1.4の敏感なアナログ信号ルーティングは、できるだけ短くなければなりません。

1.5は、力と地面を合理的に分配します。

1.6 dGND、agndとフィールド分離。

1.7の広いワイヤーは、電源と重要な信号ルーティングのために使われなければなりません。

1.8デジタル回路はパラレルバス/シリアルDTEインタフェースの近くに置かれ、DAA回路は電話回線インターフェースの近くに置かれる。

PCB配線の基本ルールと技能

2 .コンポーネントの配置

システム回路図の2.1

デジタル、アナログ、DAA回路及び関連回路を分割する

各回路において、デジタル、アナログ、ハイブリッドデジタル/アナログ部品を分割する

c)各icチップの電源と信号ピンの位置合わせに注目する。

2.2は、PCB(一般的に2 / 1 / 1)で、デジタル、アナログとDAA回路の配線領域をあらかじめ分割します。デジタルおよびアナログ部品およびそれらの対応する配線は、可能な限りそれらのそれぞれの配線領域から遠く離れて、制限されなければならない。

注意:DAA回路が大きな割合を占めている場合、その配線領域を通してより多くの制御/ステータス信号ルーティングが行われ、コンポーネントの間隔、高電圧の抑制、電流制限などのローカルルールに従って調整することができる。

2.3の予備除算の後、コネクタとジャックからコンポーネントを配置します

コネクタとジャックの周りにプラグインを配置します

部品周辺の電源及びグランド配線のためのスペースを残す

ソケットに対応するプラグインを置きます。

2.4最初の場所ハイブリッドデバイス(モデムデバイス、A / D、D / A変換チップなど)

コンポーネントの配置方向を決定し、デジタル信号とアナログ信号ピンをそれぞれの配線領域に向かわせるようにしてください

デジタルとアナログ信号の配線領域の接合部にコンポーネントを配置する。

2.5すべてのシミュレータを配置します

DAA回路を含むアナログ回路部品を配置する

シミュレータは互いに近接し、TXA 1、TXA 2、RIN、VC及びVREF信号配線を含むPCBの片側に配置される

TX 1、TXA 2、RIN、VCおよびVREF信号配線の周りに高いノイズ成分を配置することを避ける

シリアルDTEモジュールについて

直列インターフェース信号の受信機/ドライバは、チョーク及びキャパシタンスのような、各ライン上のノイズ抑制デバイスの増加を低減/回避するために、可能な限り離れて高周波クロック信号ルーティングからのコネクタに近接しなければならない。

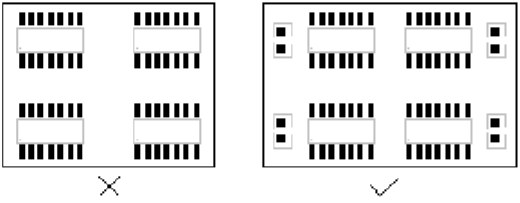

2.6デジタルコンポーネントとデカップリングコンデンサを置く

デジタル部品は、配線長を減らすために集中的に配置される

ICの電源/グラウンド間に0.1 UFのデカップリングコンデンサを配置し、接続経路はEMIを減らすためにできるだけ短くする。

パラレルバスモジュールの場合、コンポーネントは互いに近接している

ISAバス経路長が2.5インチに制限されるように、コネクタ・エッジはアプリケーションバス・インターフェース規格を満たすために置かれなければならない

シリアルDTEモジュールでは、インターフェース回路はコネクタに近接している

水晶発振回路は、できるだけそのドライバに近いものとする。

2.7各々の領域の接地線は、通常、0オーム抵抗またはクマを有する一つ以上の点で接続される。

信号ルーティング

モデム信号ルーティングの3.1で、妨害に影響を受けやすい雑音と信号線の傾向がある信号線は、できるだけ遠くに保たれなければなりません。それが避けられないならば、中立の信号線は孤立のために使われなければなりません。

モデムの干渉に弱い信号ピン、中性信号ピンおよび信号ピンは以下の表に示されている。

モデム信号ライン

RS - 232 Cシリアルポート信号は、3つのカテゴリーに分けられます:トランスミッション信号、接触信号と接地線

(1)送信信号:TXD(送信データ信号線)及びRXD(受信データ信号線)を指す。TXDを介して伝送され、RXDを介して受信された情報の形式は、送信ユニット(バイト)は、スタートビット、データビット、パリティビットおよびストップビットから構成される。

(2)接触信号:RTS、CTS、DTR、DSR、DCD、RI信号を参照し、その機能を示す。

RTS(Request Transmission)はPCからモデムに送られる連絡信号です。ハイレベルは、PCがモデムにデータを送信することを要求することを示す

モデムはPCによって送られたRTS信号に応答し、リモートモデムにデータを送る準備ができていることを示します。

DTR(Data Terminal Ready)はPCからモデムに送られる連絡信号です。高出力スクリーンはPCが準備ができていることを示します、そして、通信チャンネルはローカルモデムとリモートモデムの間で確立されることができます。それが低出力スクリーンであるならば、モデムに通信を終了させてください。

DSR ( Data Device Ready )はモデムからPCに送られてくる連絡信号です。高レベルは、モデムがテスト呼び出し状態にないことを示して、リモートモデムでチャンネルを確立することができます。

DCD(Transmission Detection)はモデムからPCに送られたステータス信号である。高レベルは、ローカルDCEがリモートモデムからキャリア信号を受信することを示す。

RI(リンギング表示)はモデムからPCに送られたステータス信号です。高レベルはローカルモデムがリモートモデムからリンギング信号を受信することを示します。

(3)接地線信号(GND)は、接続されたPC及びモデムに対して同じ電位基準点を与える。

56 k高速モデムは1997年に発売されたダイアルアップ高速モデムである。伝送速度は33.6 kと完全に異なる変復調技術を採用しており,33.6 kの高速モデムとは異なる。

dteとdceの接続規格はcctvを含んでいる。10 / x . 26 ;

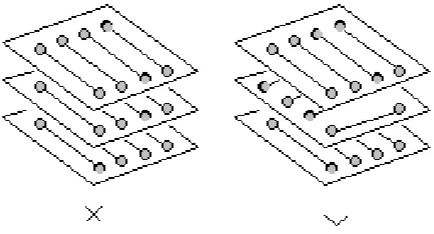

3.2デジタル信号配線は、できるだけデジタル信号配線領域に置かれなければならない

アナログ信号配線は、可能な限りアナログ信号配線領域に配置する

(分離配線は、配線を制限するために予め配置することができ、配線領域から配線が広がることを防止する)。

デジタル信号ルーティングは、相互結合を減らすためにアナログ信号ルーティングに垂直である。

3.3は、アナログ信号配線領域にアナログ信号ルーティングを制限するために孤立したルーティング(通常グラウンド)を使います。

アナログ領域の絶縁グランド配線は、PCBボードの両側に配置されたアナログ信号配線領域を囲み、ライン幅は50~100ミルである

b)デジタル領域の孤立配線は、配線幅50〜100ミルでPCBの両側に配置され、1枚のPCBの端部を200 milの幅で配置する。

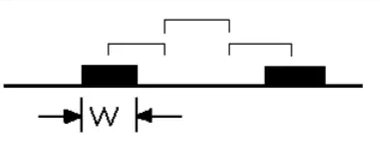

3.4のパラレルバスインターフェース信号線幅「10 mil(一般的に12~15 mil)(例えば、HCS、/ HARD、/ HWT、/ reset)。

3.5本のアナログ信号配線幅:10 mil(一般に12 - 15ミル)(例えばMIMM、MILV、SPKV、VC、VREF、TXA 1、TXA 2、RXA、テルインとテルアウト)。

3.6他のすべての信号のルーティングは可能な限り広く、ライン幅は5 mil(一般的に10ミル)であり、コンポーネント間のルーティングは可能な限り短くする(事前にコンポーネントを配置するときに考慮される)。

3.7バイパスコンデンサから対応するICへの配線幅は25ミルであり、ビアはできる限り回避しなければならない。

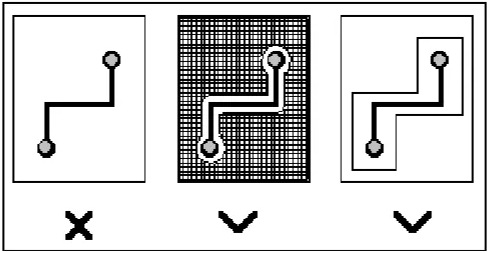

異なる領域(例えば典型的な低速の制御/ステータス信号)を通過する3.8信号線は、1ポイント(好ましい)または2ポイントで孤立した接地線を通過しなければならない。ルーティングが片側だけであるならば、孤立した接地線は信号ルーティングをスキップして、連続性を維持するためにPCBの向こう側に行くことができます。

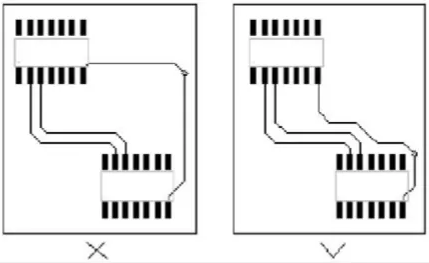

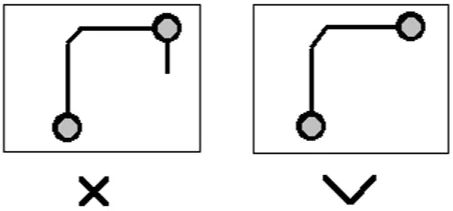

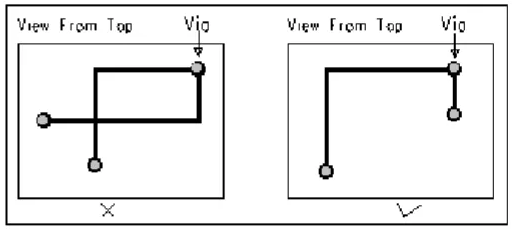

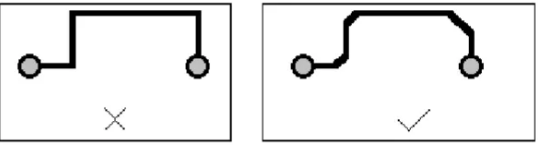

3.9高周波信号のルーティングは、90度の角度の曲げを回避し、滑らかな円弧または45度の角度を使用する必要があります。

3.10の高周波信号配線は、ビア接続の使用を減らす。

3.11すべての信号ルーティングは水晶発振器回路から離れていなければなりません。

3.12単一の連続ルーティングは、1ポイントから延びるルーティングのいくつかのセクションを避けるために高周波信号ルーティングのために採用されなければなりません。

3.13 DAA回路では、少なくとも60 milのスペースをパーフォレーション(すべての層)のまわりで去ります。

3.14は、電源に影響を及ぼすことから偶然の現在のフィードバックを防ぐために、グランド・ループをクリアします。

電源

4.1電源接続関係を決定します。

4.2のデジタル信号配線領域において、10 uFの電解コンデンサまたはタンタルコンデンサは、0.1 UFセラミック・チップ・コンデンサと並列に接続されて、それから電源/グランドの間で接続される。パワーピークパルスによって引き起こされる雑音干渉を防止するために、電力入口端とPCBボードの最遠端で1を配置する。

両面基板のための4.3は、電力回路の同じ層において、回路線を両側に200 milの線幅で電力線で囲みます。(反対側は同じ数値で扱われる)

4.4一般的に、電源配線は、最初に、そして、それから信号配線である。

5 .土地

5.1ダブルパネルでは、デジタルおよびアナログコンポーネント(DAAを除く)の前後の未使用領域は、デジタルまたはアナログ領域ドメインで満たされる。異なるレベルの同じ領域ドメインが一緒に接続され、異なるレベルの同じ領域ドメインが複数のパスを介して接続されます。モデムDGNDピンはデジタル領域に接続し、AGndピンはアナログ領域に接続しますデジタルおよびアナログ領域は、直線間隙によって分離される。

4層パネルの5.2は、デジタルとアナログのコンポーネント(DAAを除く)をカバーするためにデジタルとアナログ領域を使用しますモデムDGNDピンはデジタル領域に接続し、AGndピンはアナログ領域に接続しますデジタルおよびアナログ領域は、直線間隙によって分離される。

5.3 EMIフィルタが設計において必要であるならば、スペースはほとんどのEMIデバイス(Bead / Character)が置かれることができるインターフェースのソケット端で予約されなければなりません。未使用の地域は、ゾーンで満たされ、シールドされたハウジングに接続する必要があります。

5.4各モジュールの電源は分離されるべきです。機能モジュールは、パラレルバスインターフェース、ディスプレイ、デジタル回路(SRAM、EPROM、モデム)、DAAなどに分割することができます。各機能モジュールは、電源/グラウンドのソースポイントで電源/グランドを接続することができます。

直列結合DTEモジュールの5.5ペアは、電力結合を減らすためにキャパシタンスをデカップリングすることによって、電話回線のために同じこともできる。

5.6グラウンドラインは、可能ならばビーズを使用して、ポイントによって接続されますEMI抑制が必要ならば、グラウンド線を他の場所に接続させてください。

5.7すべての接地線は可能な限り広い、25 - 50ミルであるべきです。

5.8すべてのIC電源/グランドコンデンサは、可能な限り短くなって、スルーホールを使わない。

水晶振動回路

6.1結晶入出力に接続する全ての線(例えば、XTLi、XTLO)は、ノイズ干渉および結晶に対する分散キャパシタンスの影響を低減するために、できるだけ短い。XTLOは可能な限り短く走らせて、45度以下の回転角を持ちます。(高速立上り時間に対するXTLO接続による高電流ドライバ)

6.2ダブルパネルに接地線層がない。結晶容量性接地線は、最短の短いワイヤでデバイス上の結晶振動に最も近いDGNDピンに接続し、スルーホールを最小にする必要がある。

6.3可能であれば、クリスタルハウジングは接地される。

6.4は、XTLOピンと水晶発振器/コンデンサノードの間に100オームの抵抗を接続します。

6.5水晶振動コンデンサは、直接モデムのGNDピンに接続します。モデムのGNDピンにキャパシタンスを接続するために、接地領域または接地線を使用しないでください。

EIA / TIA - 232インタフェースを用いた独立モデム設計

7.1は、金属住宅を使います。プラスチックハウジングが必要であるならば、金属箔または導電性スプレーはEMIを減らすために内部で適用されなければなりません。

7.2は、各々の電源コードに同じモードチョークを置きます。

7.3コンポーネントを持つコネクタは、EIA / TIA - 232インタフェースの近くに置かれました。

7.4すべてのEIA / TIA - 232デバイスは、電源ポイントから別に電源/グランドに接続しています。パワー/グラウンドのソースは、基板上の電源入力または電圧レギュレータチップの出力であるべきである。

7.5 EIA / TIA - 232ケーブルは、デジタルグラウンドに信号接続されます。

アナログ信号については、以下の詳細を示します。

アナログ回路の設計は、最も困難であるが、エンジニアの最も致命的な部分でもある。ディジタル回路と大規模集積回路の開発は現在非常に急速であるが,アナログ回路の設計はまだ避けられないものであり,rf回路設計のようなディジタル回路によって置き換えることはできないここではアナログ回路の設計に注目すべき課題の概要を述べる。いくつかは、純粋に経験的です。我々はより多くを追加することができますし、もっと批判を願って!

(1)安定性の良いフィードバック回路を得るためには、通常、フィードバックリングの外側の小さな抵抗またはチョークリングが、容量性負荷のバッファを提供するために必要である。

(2)積分帰還回路は、通常、10 pFより大きい各集積コンデンサと直列に小さな抵抗(約560ユーロ)を必要とする。

(3)フィードバックループの外側に能動回路を使用して、EMCのRF帯域幅をフィルタリングまたは制御するが、受動素子(好ましくはRC回路)のみを使用しない。積分フィードバックは、開ループ利得が閉ループ利得よりも大きい周波数においてのみ有効である。より高い周波数では、積分回路は周波数応答を制御することができない。

(4)安定した線形回路を得るためには、全ての接続をパッシブフィルタや光電分離等の他の抑圧方法で保護する必要がある。

(5)EMCフィルタを使用し、IC関連フィルタをローカル0 V基準面に接続する。

(6)入出力ケーブルを外部ケーブルの接続部に配置する。シールドシステムのないどんなワイヤー接続も、アンテナ効果のために濾過される必要があります。フィルタリングは、デジタル信号処理またはスイッチングモードを有するコンバータの遮蔽システム内のワイヤ接続でも必要である。

(7)アナログic電源とグランドリファレンスピンでは,ディジタルicと同様に高品質のrfデカップリングが必要である。しかし、アナログICのパワーノイズ除去比(PSRR)が1 kHzを超えてほとんど増加しないので、アナログICは、通常、低周波数でパワーデカップリングを必要とする。RCまたはLCフィルタは、各オペアンプ、コンパレータ、およびデータコンバータのアナログ電力線に使用されるべきである。電力フィルタの角周波数は、全体の動作周波数範囲にわたって所望のPSRRを得るために、PSRRコーナー周波数及び装置の傾きを補償しなければならない。2 p % Uy 3 a 8 f

8)高速アナログ信号に対しては,接続長,通信の最高周波数に応じて伝送線路技術が必要である。低周波信号についてさえ、伝送ライン技術の使用はそれらの妨害妨害を改善することができます、しかし、適切にマッチした伝送線の不足はアンテナ効果を生じるでしょう。

(9)電界に対して非常に敏感である高インピーダンス入力または出力を使用することを避ける。

(10)放射線の大部分はコモンモード電圧と電流によって生成されるため、環境における電磁干渉の大部分はコモンモードの問題に起因しているので、アナログ回路における平衡送信および受信(差動モード)技術は良好なEMC効果を有し、クロストークを低減する。平衡回路(差動回路)ドライバは、リターン電流ループとして0 V基準システムを使用しないので、大きな電流ループを回避し、それによってRF放射を減少させる。

(11)比較器は、ノイズと干渉による誤った出力変換を防止し、ブレークポイントでの発振を防止するために、(正帰還)を有する必要がある。必要なより高速な比較器を使用しないでください(あなたの要件を満たしている間、可能な限り低dv / dtを維持)。

(12)アナログICは特に無線周波数フィールドに対して敏感であるので、PCB上に実装され、PCBのグランド表面に接続された小さな金属シールドボックスを有するこのようなアナログ素子をシールドすることがしばしば必要である。その放熱条件を確実にするために注意してください。

複雑なPLDのためのCPLDは短いです。その名前が意味するように、それはPLDより複雑な論理要素です。cpldは高集積の論理素子である。高い集積化のため,性能の向上,信頼性の向上,pcb面積の低減,低価格化の利点がある。CPLD要素は、基本的に多くの論理ブロックの組合せです。各論理ブロックは単純なPLD要素(例えば22 V 10)に似ています。論理ブロック間の関係は、論理回路全体を合成する可変接続構成で構成される。

共通のCPDコンポーネントは、AlteraのMAX 5000とMAX 7000シリーズです。サイプレスのMAX 340とFLASH 370シリーズ、一般的に、CPLD要素のゲートカウントは、1000と7000のゲートの間にあります。