エー, PCBシミュレーション とDDR 3メモリ設計

1今日のコンピュータシステムddr 3メモリ技術は広く使用されており,データ伝送速度は繰り返し進められており,現在では1866 mbpsと非常に高い。

この種の高速バスの条件下では,データ伝送品質の信頼性を確保し,パラレルバスのタイミング要求を満たすため,設計と実装に大きな課題を提起した。

本論文では,主としてddr 3の設計を定量的に解析するために,cadenceの時間領域解析ツールを用いて,ddr 3タイミング解析の信号完全性に影響を与える主要因子を導入し,信号品質を改善するための結果の解析を通して設計を改善し最適化する。その信頼性と安全性を大幅に改善されます。

2 DDR 3 DDR 3メモリへの導入は、2つのコントローラとメモリ部分を含むDDR 2メモリに類似しています。そして、そのすべてはソース同期タイミングを使用します。

それは1866 Mbpsまで、DR 2より高いデータ転送速度を持ちます;DDR 3も8ビットプリフェッチ技術を使用します。そして、それはかなり記憶域帯域幅を増やします、そして、その動作電圧は1.5 Vです。そして、同じ頻度で消費電力を減らしました。DDR 3インタフェースデザインは達成するのが難しいです。それは、トポロジーによってユニークなハエを使用して、デバイスの他の効果的な処置の内部のオフセットタイミングを制御するために、「書込み等化」技術を使用します。

これは、設計の実装と信号の整合性を確保する役割を果たしているが、高周波数と帯域幅を達成するストレージシステムは包括的ではありません。したがって,設計実装と信号品質の完全性を保証するためにシミュレーション解析が必要である。

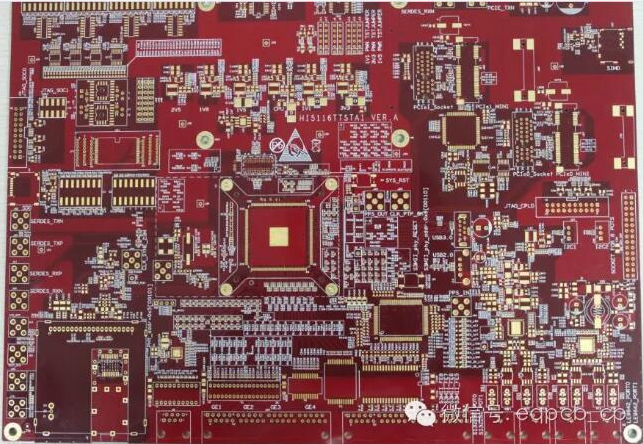

3シミュレーション解析DDR 3シミュレーション解析を説明するプロジェクトと組み合わせる:PowerPC 64ビットデュアルコアCPUモジュールを選択し、このモジュールは、メモリのためのミクロンのMT 41 J 256 M 16 HI - 125 EITを使用しています。

p 5020のプロセッサを解析すると,モジュールは1333 mt/sのメモリバスデータ伝送速度と666 mhzのアナログ周波数で構成される。

3.1分析前の事前シミュレーション準備, DDR 3のインピーダンスに基づいてPCBメーカーと通信し、積層構造を確認する必要がある. 高速伝送における伝送線路の性能を確保するためのキーは連続特性インピーダンスである. のインピーダンス制御を決定する 高速PCB信号 ある範囲内の線, プリント基板が「制御可能なインピーダンス板」になるように, アナログ解析の基礎.

DDR 3バスの単線インピーダンスは50アンペア、差動リニアインピーダンスは100アンペアである。解析されたデバイスのパッシブデバイスアロケーションモデルを含む解析ネットワーク端末の電圧値を設定し、デバイスの種類の属性を決定し、デバイスのピン属性(入力および出力、電源接地など)を確認します。

第二に、迅速にPCBの高速システムの信号の整合性を解決する

すぐに、PCB高速システムの信号完全性問題を解決してください。データ速度の増加に伴い,信号完全性問題は設計技術者が考慮した最も重要な要因となった。データレートのこの指数関数的増加は、ハンドヘルドモバイルデバイス及び消費者ディスプレイ製品のような高帯域幅ルータ/スイッチなどのアプリケーションにおいて見ることができる。ジッタ(雑音)は設計における信号完全性のレベルを減少させる主な理由である。信号の整合性向上技術を達成するために、レイアウト、インピーダンス整合およびより高価な材料を使用することに加えて、設計者は、ジッタ問題を解決するためにイコライザのようなジッタ受信機を単に設計に加えることもできる。

このように、設計者は、信号完全性問題に焦点を合わせる必要はなく、システムのコア設計に関して。従来、信号配線は単純な概念と考えられており、配線の観点から映像信号、音声信号、データ信号の区別はない。したがって、過去の信号配線についてはほとんど人が関心を持っていなかった。しかし、状況は完全に変わりました。ビデオ信号伝送速度は現在チャネルあたり3.3 Gbpsに達し、データ信号はチャネルあたり5 Gbpsをはるかに超える。

PCI Express、XAUI、SATA、TMDS、および表示ポートなどの高速シリアル規格は、設計の整合性の問題を考慮するだけでなく、設計のチームとエンジニアが必要ですが、また、それがシステムの性能と信頼性にどのように影響を与えるかの詳細な理解を持っている。この知識を習得するために、技術者は最初にシステムの信号完全性に影響する要因を理解しなければならない。信号ジッタを増加させることにより,システムの信号完全性の損失を観測できる。システムの全ジッタは主に2種類のジッタ,すなわちランダムジッタと決定性ジッタから構成される。ランダムジッタは無限大であり、基本的にはガウス分布に従う。一方、決定論的ジッタは有限で予測可能である。

システムの90 %において、決定論的ジッタは、設計技術者が解決しなければならない主な信号完全性問題である。決定論的ジッタは、帯域幅制限問題、クロックサイクル非対称性、および交差結合またはEMI問題によって引き起こされる符号干渉(ISI)、デューティサイクル歪み、および周期ジッタを含む。

コネクタ、PCB配線、長いケーブル、および配線に沿って配置される他の受動部品のような受動部品は、決定的ジッタの最も重要な原因である。信号周波数が高いほど、減衰が大きくなるので、指定されたデータストリームの電力レベルは一致しない。そして、この電力レベルの不整合は信号中のISIをもたらす。

ISIは信号完全性を減少させます。そして、それは受信機が受信端で信号からどんな実際のデータも正しく抽出するのを防ぐのに十分です。電力レベル不整合の理由は、設計エンジニアが設計におけるデータ伝送を保証することができないことである。データは常に(0 - 1 - 0 - 1 - 0 - 1など)または定数(1 - 1 - 1 - 1 - 1 - 1など)を変更することができます。明らかに、上記の6つの変化ビットの免税比は、6“1”定データストリームのデューティ比の6倍である。免税率が6倍小さいので、信号周波数は6倍高くなる。

データストリームがこれらの2つのタイプを含む場合、受信機信号は非常に異なる電力レベルを有する。

電力不一致の問題を解決する最も高速な信号規格は、変化のない連続ビットの数が8 B/10 B符号化のように最小化されるべきであることを規定する。この符号化方式は、データストリームが連続した4ビットを超えないことを保証する。

しかし、受信機信号の高電力部分を4倍にすることは依然として可能である。ISIを減らすために電力レベル不整合を補償するために、PCB設計者は、等化またはデエンファシス技術を使用することができる。

PCB等化技術 すべての高速ビットのパワーを増加させる, したがって、高速および低速ビットの受信信号は、同じ電力レベルを有する, これにより、電力レベルの不整合を低減する. 悪化するバランスの反対, しかし、目標は同じです:パワーレベルの不一致を最小化. これは、低速ビットの電力を減らすことによって行われます, これは高速ビットのパワーを増加させる.