高速で導入された効果を考える PCB伝送線路 問題, 我々は、以下の側面からこれらの効果を制御する方法について話します.

1厳密にネットワークケーブルの長さを制御する

設計に高速遷移エッジがあれば,pcbへの伝送線路効果の問題を考慮しなければならない。今日一般に使用される非常に高いクロック周波数を有する高速集積回路チップはそのような問題を有する。この問題を解決するためのいくつかの基本的な原理がある。CMOSまたはTTL回路を設計する場合、動作周波数は10 MHz未満であり、配線長は7インチより大きくならない。配線長は50 MHzで1.5インチより大きくすべきではない。動作周波数が75 MHzに達しているか、または超えるならば、配線長は1インチでなければなりません。GaAsチップの最大配線長は0.3インチである。この規格が超えているなら、送電線問題があります。

2配線のトポロジーを合理的に計画する

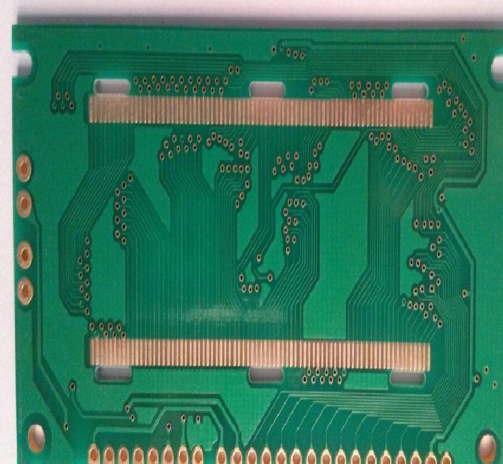

別の解決策高速PCB伝送路は正しい配線経路と端末トポロジーを選択することです. 配線のトポロジ構造は、ネットワーク・ケーブルの配線シーケンス及び配線構造を指す. 高速論理デバイスの使用, トレース分岐の長さが短い場合を除き, シグナルトランクトレース上の分岐トレースによって、急速に変化するエッジを有する信号は歪んでしまう. 平常に, PCBルーティングは2つの基本トポロジーを使用する, すなわちデイジーチェーンルーティングとスター分布.

デイジーチェーン配線は、駆動端から配線が始まり、各受信端に順番に到達する。信号特性を変化させるために直列抵抗を使用すると、直列抵抗の位置はドライブ端に近いはずである。配線の高次高調波干渉を抑制する観点から、デイジーチェーン配線は最良の効果を有する。しかし、この配線方法は分布率が最も低く、100 %の分配が容易ではない。実際の設計では,デイジーチェーン配線の分岐長をできるだけ短くした。安全な長さの値は以下のはずです。

例えば、高速TTL回路の分岐端の長さは1.5インチ未満でなければならない。このトポロジは、より少ない配線スペースを占有し、単一の抵抗で終端することができる。しかし、この配線構造では、異なる信号受信時の信号の受信を非同期にすることができる。

スター・トポロジー構造は、クロック信号の非同期問題を効果的に回避することができるが、高密度PCB基板上の手動で配線を完了することは非常に困難である。自動ルータを使用して、星の配線を完了する最良の方法です。各分岐には終端抵抗が必要です。終端抵抗器の抵抗は、接続の特性インピーダンスに一致しなければならない。これは、手動で、またはCADツールによって、特性インピーダンス値および端子整合抵抗値を計算することができる。

上記2つの例では、簡単な終端抵抗を用いる。実際には、より複雑な整合端子を選択することができる。最初のオプションはRCマッチング端末です。RCマッチング端末は電力消費を減らすことができるが、信号が比較的安定しているときにのみ使用することができる。この方法はクロックライン信号のマッチングに最も適している。欠点は、RC整合端子のキャパシタンスが信号の形状及び伝搬速度に影響を及ぼすことである。

直列抵抗整合端子は、追加の電力消費を生じないが、信号伝送を遅くする。この方法は時間遅れがほとんどないバス駆動回路に用いられる。直列抵抗整合端子の利点は、車載デバイス数と配線密度を低減できる点である。

最後の方法はマッチング端末を分離する方法です。このように、マッチング・コンポーネントは、受信端の近くに置かれる必要がある。利点は、信号をプルダウンしないことであり、ノイズは非常によく回避できる。典型的には、TTL入力信号(ACT、HCT、高速)に使用されます。

また、端子整合抵抗のパッケージタイプと設置タイプも考慮しなければならない。一般に、SMD表面実装抵抗器はスルーホール構成要素より低いインダクタンスを有する。あなたが普通のインライン抵抗器を選ぶならば、インストールのために2つのオプションもあります:垂直と水平。

垂直設置モードにおいて、抵抗器の1つの取付ピンは非常に短い。そして、それは抵抗器および回路基板間の熱抵抗を減らすことができる。しかし、より長い垂直のインストールは、抵抗器のインダクタンスを増やします。水平設置は低い設置によりインダクタンスが低い。しかし、過熱した抵抗はドリフトする。最悪の場合には、抵抗はオープン回路となり、PCBトレース終端整合故障となり、潜在的な故障要因となる。

3電磁干渉を抑える方法

信号完全性問題への良い解決は、PCBボードの電磁両立性(EMC)を改善するであろう。非常に重要なのは、PCBボードが良好な接地を有することを保証することである。複雑な設計のために接地層を持つ信号層を用いることは非常に有効である。加えて、回路基板の最外層の信号密度を最小にすることは、電磁放射を減らす良い方法でもある。この方法は,「表面積領域」技術「ビルドアップ」設計とpcbを製造することで実現できる。表面領域層は、共通のプロセスPCB上にこれらの層を貫通するために用いられる薄い絶縁層と微小孔との組み合わせを追加することによって実現される。抵抗および容量は、表層の下で埋設されることができて、単位面積当たりのトレース密度はほぼ2倍になる。PCBのサイズを小さくします。PCB面積の減少は、トレースの位相構造に大きな影響を与え、電流ループが減少し、分岐トレースの長さが減少し、電磁放射線が電流ループの面積にほぼ比例することを意味する同時に、小型の特徴は、高密度リードフットパッケージデバイスを使用することができ、これにより、ワイヤの長さを短くすることができ、それによって電流ループを低減し、電磁両立性の特性を改善することができる。

4他の利用できるテクノロジー

集積回路チップの電源上の電圧の瞬間的オーバーシュートを減らすために、デカップリングコンデンサを集積回路チップに追加すべきである。これにより、電源に対するバリの効果を効果的に除去し、プリント基板上の電力ループの放射線を低減することができる。

デカップリングコンデンサがパワー層の代わりに集積回路のパワーチューブ脚部に直接接続されるとき、バリを平滑化する効果は最もよい。これは、いくつかのデバイスソケットがコンデンサを切り離している理由であり、いくつかのデバイスは、デカップリングコンデンサとデバイス間の距離を十分小さくする必要がある。

いかなる高速で高出力デバイスも、電源電圧の過渡的オーバーシュートを減らすために、できるだけ一緒に置かれなければならない。

パワー・レイヤーがない場合、長い電源接続はシグナルおよびループ間のループを形成する。そして、放射源および敏感な回路になる。

状況 PCBトレース 同じネットワークケーブルまたは他のトレースを通過しないループをオープンループと呼ぶ. ループが同じネットワークケーブルの他のワイヤーを通過するならば, 閉ループを構成する. 両方とも,アンテナ効果(有線アンテナとループアンテナ)の形成. アンテナは外部からEMI放射を発生し、また、敏感な回路そのものでもある. 閉ループは、発生する放射線が閉ループの面積にほぼ比例するので考慮されなければならない問題である.