導入

シグナル完全性 回路系の信号の品質を示す. 信号が必要な時間の範囲内で歪みなしでソースから受信端まで伝送されることができる場合, 信号は完全であると言われている. 半導体技術の急速な発展とICスイッチの出力速度の向上, signal integrity issues (including signal overshoot and undershoot, リンギング, 反射, クロストーク, グラウンドバウンス, etc.) have become one of the issues that must be paid attention to in high-speed PCB設計. . 通常, デジタル論理回路の周波数は50 MHz, そして、この周波数で動作する回路は1を超える/システム全体の3, 高速回路と言えます. 事実上, 信号自体の周波数に比べて, 信号エッジの高調波周波数は、より高い, and the rapid changes (rising and falling edges) of the signal cause unexpected effects of signal transmission. これは、信号完全性問題の源でもあります. したがって, 高速における信号完全性因子を完全に考慮する方法 PCB設計 回路設計の品質を向上させるための効果的な制御策をとるためのプロセスは、考慮すべき問題である.

高速信号に対する信号完全性シミュレーション解析を実行するためのiBISモデルを使用して、強力なCadence Speectraquestシミュレーションソフトウェアの助けを借りて、信号完全性問題を見つけることができて、シミュレーション結果に基づくシグナル完全性問題を実行することは、設計を最適化する効果的で実行可能な分析方法である。設計品質の向上と設計サイクルの短縮を目的とした。

1アプリケーション設計例

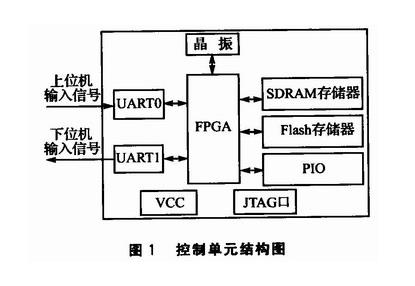

本システムにおいて設計された制御装置の機能は、地上受信装置が受信した符号化信号を主局データ処理センタに戻すことである。具体的な作業プロセスは、最初にホストコンピュータ・データを記憶して、それからビットエラー・レート試験および計算によって、データ伝送経路として最も低いビット誤り率を有するパスを選ぶ。そして、最終的にプロセスにこのパスを経て主駅データ処理センターに格納されたホストコンピュータ・データを伝送する。包括的な考慮の後、AlteraのサイクロンII - 2 C 8は、外部チップと同様に外部の拡張SDRAM、フラッシュ、いろいろな入出力回路とMax 232インターフェース・チップなどとして選ばれて、NIOS IIソフト・コア・プロセッサー開発キットと結合しました。制御部の構成を図1に示す。

cycloneii - 2 c 8のクロック周波数は最大150 MHz以上である。FPGA内部のデータ記憶領域は比較的小さいので、SDRAMは外部データ記憶空間を拡大するために使用される。SDRAMはHY - NIX社のHY 57 V 651610を採用しており、クロック周波数は75 MHzを超える。従って、信号周波数が過大になることに起因する信号の健全性の問題を考慮する必要がある。設計図,pcbレイアウト,高速シミュレーション解析を統合した強力なcad ence design softwareを選んだ。それはデザインのすべての面で電気性能に関する問題を解決することができて、デザインを大いに改善します。成功率。

2キー信号トポロジーとシミュレーション

このシステムの高周波部分はFPGAとSDRAMである. FPGAのクロック周波数は150 MHz以上に達することができる, そして、SDRAMのクロック周波数は、75 MHz. FPGAの内部高周波が他のデバイスに影響しないので, FPGAとSDRAMの接続はシームレスです, 信号の整合性は、FPGAが正しくSDRAMを読み書きできるかどうか直接的に影響する. イン PCB設計, Cadenceソフトウェアの高速シミュレーションツールspecctraquestを使用する, そして、デバイスのIBISモデルは、信号完全性を分析するために用いる, そして、システムの正常な動作を確実にするためにインピーダンス整合およびトポロジ構造が最適化される. この記事は、信号反射とクロストークの詳細な説明をするだけです, 他のシミュレーションも同様です.

2.1反射

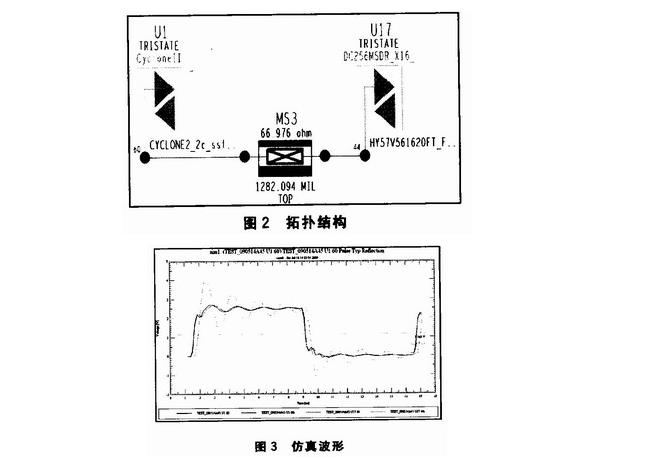

送信端はHi 57 V 561620の44ピンであり、受信端はサイクロトロンIIの60ピンであり、励起は66 MHz方形波である。図2はトポロジー構造を示し、図3はシミュレートされた波形を示す。

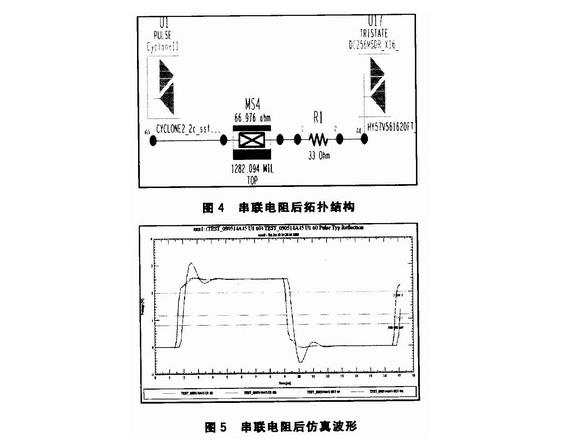

シミュレーション波形から信号歪みによる波形歪みが見られ,明らかなリンギング現象が生じることがわかった。リンギング現象の存在により、信号はレベル論理しきい値を何度も交差させ、論理関数の乱れにつながる。リンギングノイズを減少させる効果的な方法は、回路のために減衰を提供する回路と直列の小さな抵抗器を接続することであり、回路の速度にほとんど影響を与えずに、リンギング振幅を大幅に減少させ、リンギング発振時間を短縮することができる。工学的な使用において、抵抗は通常33アンペアである。図4および図5は、直列抵抗の後のトポロジカル構造およびシミュレートされた波形を示す。

直列抵抗後のリンギング現象はよく解決された。実際には、この解をインピーダンス整合と呼ぶ。インピーダンスは信号完全性問題において極めて重要な位置を占める。

2.2クロストーク

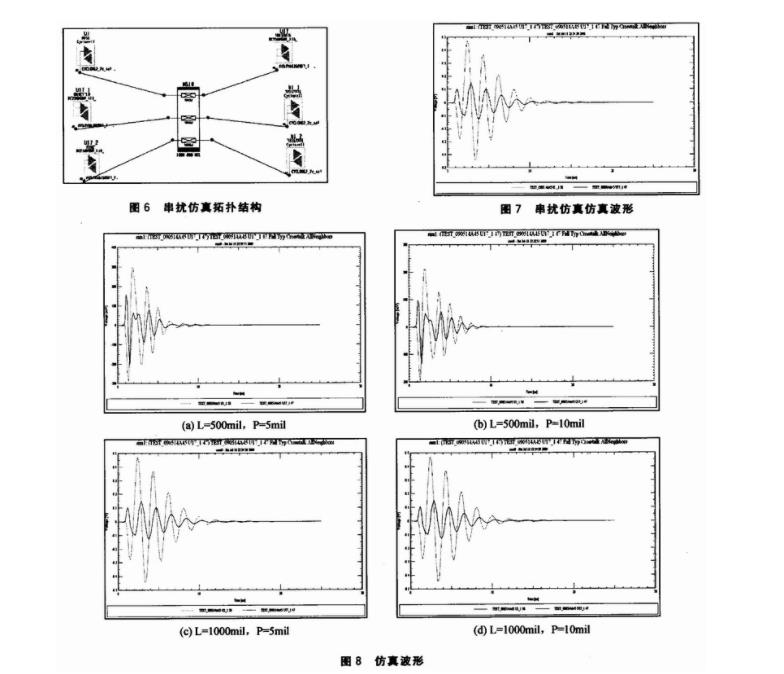

抽出SDNADDQLO(サイクロンIIの59ピンを接続し、Hi 57 V 561620の45ピンを接続)、SDUNDQDLL(サイクロンIIの58ピンを接続し、HY 57 V 561620の47ピン)、SDUNDER DQ - L 2(サイクロンIIの57ピンを接続し、HY 57 V 561620の48ピン)これらの3つのネットワークの間のクロストークシミュレーションを行う。それらの中で、攻撃ネットワークとしてのSDRACK DQLL、攻撃ネットワークとしてSDHUNDQLOとSDUNE D - QL 2。それらのトポロジ及びシミュレーション波形は、図6及び図7(伝送線路の並列結合長はL=1000ミル、ピッチP=5ミル)で示されている。

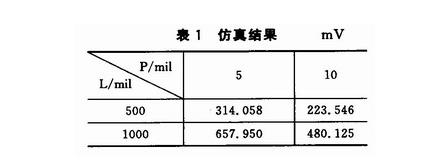

シミュレーション波形を図8に示す。図7から、クロストークが攻撃されたネットワークに大きな影響を及ぼすことが分かる。クロストーク値クロストーク=657.95 mVは、伝送線路の並列結合長Lと間隔Pに関係する。結合長が短いほど、間隔が大きくなる。クロストークは小さい。シミュレーション結果を表1に示す。

したがって, 作るとき PCB, 異なる特性の信号線間の平行長は、許容されるとき、できるだけ少なくされなければならない, それらの間隔は広くなければならない, そして、いくつかの線の線幅と高さを変えなければなりません. もちろん, 漏話に影響する多くの要因がある, 干渉源信号の電流フロー方向と周波数上昇時間のような, どれを包括的に考慮すべきか.

まとめ

この高速で PCB設計 制御装置の, 強力なCadenceソフトウェアは、回路図の製造から良い結果を達成するのに用いられました, PCB 高速シミュレーション解析へのレイアウト. SpeecTraquestシミュレーション解析によって得られた合理的トポロジーとレイアウトに従って, 回路基板は正常に動作できる. この設計方法はハードウェアデバッグ時間を大幅に短縮する, 作業効率の向上, と設計コストを節約.