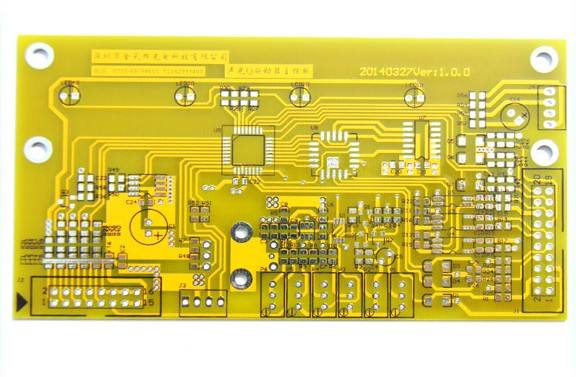

現在のPCB基板プルーフの電子設計はほとんど統合システムレベル設計であり、プロジェクト全体はハードウェア設計とソフトウェア開発の両方を含んでいる。この技術的特徴は,pcb技術者に新たな課題を提起する。

まず最初に、システムのソフトウェアとハードウェア機能を初期設計段階で合理的に分割し、冗長な周期的プロセスを回避するための効果的な機能構造フレームワークを形成する方法

第二に、短時間で高性能で信頼性の高い基板を設計する方法。ソフトウェアの開発は、ハードウェアの実現に大きく依存しているため、マシン全体の設計を一度だけ通過させることによって、設計サイクルをより効果的に短縮することができる。新技術背景の下でのシステムボードレベル設計の新しい特徴と新しい戦略について論じた。

我々が知っているように、電子技術の発展は、それぞれの通過日で変化しています、そして、この変化の根本原因はチップ技術の進歩です。半導体プロセスはますます物理的になり,今ではディープサブミクロンレベルに達し,超大規模回路はチップ開発の主流となっている。そして、このプロセスとスケールの変化は、エレクトロニクス産業全体に多くの新しい電子設計のボトルネックをもたらした。ボードレベルのデザインも大幅に影響されている。最も明白な変化は、BGA、TQFP、PLCCおよび他のパッケージングタイプの出現のような、多種多様なチップパッケージングである第二に、高密度のピンパッケージングと小型化パッケージングが1つになった。このようなやり方は,mcm技術の幅広い応用など,製品全体の小型化を実現するためである。また、チップの動作周波数の増加により、システムの動作周波数を高くすることができる。これらの変更は必然的に多くの問題とレベルのデザインをボードに挑戦をもたらすでしょう。最初に、高密度ピンおよびピン・サイズの物理的限界の増加のために、低い展開率に結果としてなる第2に、システムクロック周波数の増加に起因するタイミングおよび信号完全性問題;第三に、エンジニアは、PCプラットフォームを使用してより複雑な、高性能なデザインを完了するために使用できるように願っています。したがって、PCBボード設計には以下の3つの傾向があることが分かりにくい。

高速ディジタル回路(すなわち高クロック周波数と高速エッジ)のpcb設計は主流となった。

製品の小型化と高性能は,同一ボード上の混合信号設計技術(すなわち,ディジタル,アナログ,rf混合設計)による配電効果の問題に直面しなければならない。

設計の難易度の増加は従来の設計プロセスと設計方法を引き起こし,pcb上のcadツールは現在の技術的課題を満たすことが困難であった。したがって,unixプラットフォームからntプラットフォームへのedaソフトウェアツールプラットフォームの転送は業界で認識された傾向となっている。

PCB校正用高速ディジタルシステム用PCBボードソリューション

一般に、信号相互接続遅延がエッジ信号反転しきい値時間の20 %より大きい場合、基板上の信号配線は伝送線効果、すなわち、接続はもはや集中定数パラメータ性能を示す単純なワイヤではなく、分布定数の影響を示すが、この設計は高速設計である。高速デジタルシステムの設計において、設計者は、タイミングと信号の整合性の問題である寄生パラメータによって引き起こされる偽の反転と信号歪みの問題を解決しなければならない。現在,これは高速回路設計者が解決しなければならないボトルネック問題でもある。

PCB校正は伝統的な物理規則によって駆動される

従来の高速PCB回路設計では,電気的ルール設定と物理的ルール設定は別々であることが分かった。これにより、以下の欠点が生じます。

PCB設計の初期に、エンジニアは、電気的要件を満たす物理的配線戦略を計画するために、詳細なフロントエンドとバックエンド(すなわち、論理確立物理的実現)分析に多くのエネルギーを費やさなければならなかった。

高速効果は複雑な課題であり,配線長と平行線を制御するだけでは期待できない効果が得られない。

デザイナーは必然的にそのようなジレンマに直面するでしょう。実際の配線では、偽成分の物理ルールは適用できない。彼は繰り返し規則を変更して、彼らに実用的な価値を持たせる必要があります。

配線が完了すると、後検証ツールを解析に使用することができる。しかし、問題が発見されるならば、エンジニアはデザインに戻って、構造または規則を調整しなければなりません。これは周期的冗長プロセスである。それは必然的に市場への時間に影響します。

設計において重要なワイヤネットが数個または数個しかない場合、物理ルール駆動は、設計タスクをよく完了することができるしかし、デザインにおいて何百または何千ものワイヤーネットがあるとき、物理的な支配された方法は、設計タスクを実行する基本的な無能です。電子技術の発展は,デザインに直面するボトルネック問題を解決するための新しい方法とツールの出現を要求している。物理法則駆動高速設計の欠点を解決するために,高速ディジタル回路設計edaツールの開発に携わった業界での洞察の人々は,3年前のリアルタイム電気ルール駆動型物理レイアウトの概念を提案し,高速ディジタルpcb設計アイデアを設計した。その過程は改革された。