ギガビットタンデムI/O技術は極めて優れた効能を持っているが、これらの優れた効能は条件を必要として保証する、すなわち優れた信号完全性である。例えば、あるビットベンダーは、特定のアプリケーションのギガビット直列設計に対して高速を使用しようとしたとき、故障率は90%であったと報告している.成功率を高めるためには、類比を行い、より複雑な新しいバイパス回路を採用する必要があるかもしれない。

Spartan-6 FPGAのGTP機能はプリント基板に依存する。テストでは、PCB基板の設計過程、プレートの積層構造、コンポーネントのレイアウト、信号経路を考慮する必要がある。

電源装置とスタック

Spartan-6 FPGA用GTPトランシーバスタックは2.つのグループ、配電層、信号ルート層に分けることができる。パワー層はMGTACC、MGTAVCCPLL、GTPの管理タワーvtttxとデータの管理電源ピンを接続するために使用される。

スタックにおいて、地平層伝送信号線は信号リターン経路を提供する.一方、つの信号層の間にはマスク面があるため、信号経路の場合、隣接層の配線を考慮する必要があり、より多くの信号経路を提供する必要がない.

GTP社の電力平面は接地層と密接に隣接し、結合効果を増加させるべきである。接地板はGTP社の電源面に遮蔽を提供することができ、上層または次の層の信号によるノイズから電力面を遮蔽することができる。

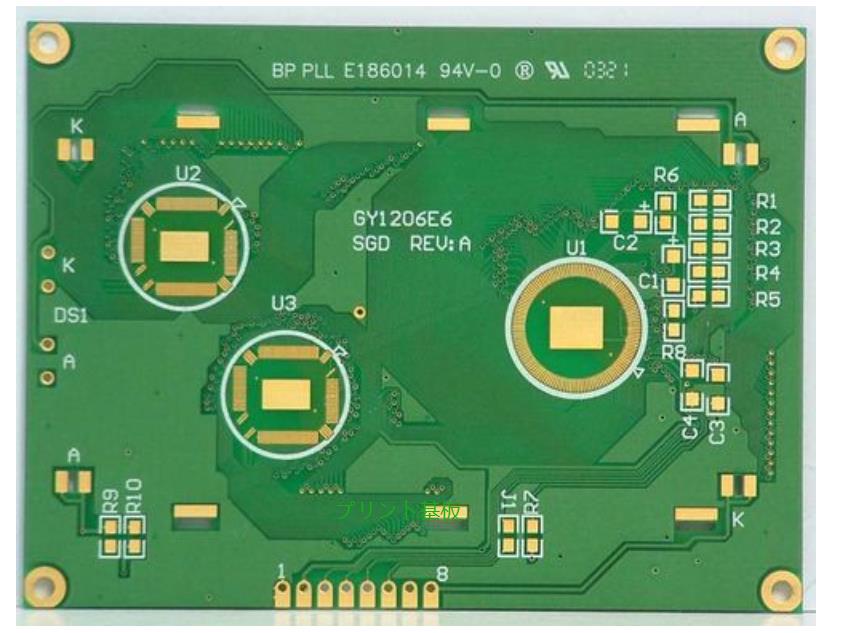

プリント配線板設計コンデンサ配置

バイパスコンデンサの値を考慮する以外はは、考慮すべきもう一つの重要な点はコンデンサの配置である.

一般的な法則は容量が大きいほど、配置要求が厳しくないことである.キャパシタ値が小さい場合は、キャパシタはできるだけ電源と接地ピンに近づけるべきである.使用できる1つの方法は、未使用の汎用IOのトレースとビアを除去し、バイパスコンデンサのスペースを空けることです

GTPパワーセグメント領域の位置とGTPフィルタコンデンサの位置。

シグナルルーティング

隣接層上のGTP信号トレースとSelectIO信号トレースは避けるべきであるは、それぞれの戻り経路も分離すべきであり、ビアを含む.差分線対間及び差分線と他の線との間に一定の距離を保つことが重要である.一般的な規則は、隣接線対間の距離は少なくとも線対中の2.本の線間の距離の0.5倍でなければならない。

ギガビット信号差動線路は配線層の変更をできるだけ避けるべきである.レイヤー間の転送が必要な場合は、特に注意する必要があります。第一に、完全なリターンパスを提供しなければならない。したがって、A.層の参照層とB層の参照層を結合しなければならない。2.つの参照層が地層であることが望ましい.この場合、戻り経路は、2.つの基準層を伝送層の近傍に接続する別の貫通孔を配置することにより実現することができる.基準平面が異なる場合(1つは地表平面、もう1つは電源平面)は、回路インピーダンスを低減するために、0.01華氏度キャパシタをできるだけ貫通孔に近づけるように2.つの基準面を接続する必要があります。プロセス中に多くの問題が

実際には、別の観点から、電源ノイズが高周波範囲に現れると、周波数の増加に伴う、その周波数範囲をカバーしてフィルタ効果を実現できるキャパシタを見つけることが困難になり、そのようなキャパシタを見つけることが不可能になるまでは、電源ノイズが高周波範囲に現れる.容量値の減少に伴い、パッケージの相関浮遊インダクタンスと抵抗値は変化せず、この周波数応答はほとんど変化しなかった。高速でより良い電力分配を実現するためには、電力層と接地層を使用して独自のキャパシタを構築する必要があります。私たちの目標をより効果的に実現するためには、通常、隣接する電源平面と接地層を使用する必要があります。

GTP社電源ピンと配電ネットワークとの接続はGTP社の効能に重要な役割を果たす。へんこうびぶんもう社、プログラマブルゲートアレイは低インピーダンスと低雑音接続を必要とする.プログラマブルゲートアレイのGTP社電源は10百万ボルトの最大雑音に耐えることができる。電源は10 kHzから80メガヘルツの範囲で小型機を用いることができる.この小さな電源ボードはIOを選択の中間面の領域をカバーすべきではない.