В дополнение к передовым процессам, передовые инкапсуляции стали ключевой технологией для продолжения закона Мура. В последние годы такие технологии, как 2.5D, 3D и чипы, стали горячей темой в полупроводниковой промышленности. Как именно высокоуровневая упаковка играет ключевую роль в продолжении закона Мура? В чем особенности таких технологий упаковки, как 2.5D, 3D и Chiplets?

Появились такие приложения, как искусственный интеллект, автомобильные сети и 5G, все из которых требуют передовых функциональных чипов с высокоскоростными вычислениями, высокоскоростной передачей, низкой задержкой и низким потреблением энергии. Однако, поскольку спрос на вычисления многократно растет, продолжение закона Мура является проблемой для полупроводниковой промышленности.

По мере того, как микросхемы становятся все более сложными, возникает изомерная интеграция.

Другими словами, передовые полупроводниковые технологии развиваются в направлении 7 нм, 5 нм, а затем 3 нм и 2 нм. Таким образом, размер транзистора приближается к физическому пределу объема атома. Электронные и физические ограничения также затрудняют дальнейшее сокращение и модернизацию передовых процессов.

Поэтому, помимо продолжения разработки передовых процессов, полупроводниковая промышленность также ищет другие способы поддержания миниатюризации и эффективности чипов. Дизайн компоновки чипа стал новым решением, которое продолжает закон Мура, и возникла концепция изомерной интегрированной архитектурной системы дизайна (HIDAS), которая стала инновационной движущей силой чипов интегральных схем.

Так называемая гетерогенная интеграция, в широком смысле, через упаковку, 3D - укладку и другие технологии, память + логический чип, фотоэлектрические + электронные компоненты и другие два разных чипа, интегрированных вместе. Другими словами, интеграцию двух чипов с различными процессами и производительностью можно назвать гетерогенной интеграцией.

Поскольку рынок приложений более разнообразен, стоимость, производительность и целевая группа каждого продукта различны, поэтому требуемые технологии гетерогенной интеграции также различны, и тенденция фокусировки рынка постепенно проявляется. Таким образом, IC суррогаты, производство и полупроводниковая промышленность оборудования инвестировали в разработку гетерогенной интеграции, 2.5D, 3D - инкапсуляции, Chiplets и другие популярные технологии инкапсуляции, основанные на концепции гетерогенной интеграции, такие как весенние ростки.

2.5D Эффективное снижение затрат на производство чипов

В прошлом, чтобы интегрировать чипы вместе, большинство из них используют технологию системы в упаковке (SiP), такую как PiP (инкапсуляция в упаковке), PoP (инкапсуляция в упаковке) инкапсуляция. Тем не менее, как смартфоны, AIoT и другие приложения, которые требуют не только более высокой производительности, но и поддержания небольшого объема и низкого энергопотребления, в этом случае мы должны найти способ сложить больше чипов, чтобы уменьшить объем, поэтому нынешняя технология упаковки в дополнение к оригинальному SiP также развивается в направлении технологии трехмерного инкапсуляции.

Короче говоря, трехмерное инкапсуляция означает использование кремниевого промежуточного слоя (кремниевого промежуточного слоя), изготовленного непосредственно из кремниевых пластин, вместо использования предыдущего пластикового « носителя провода» и инкапсулирование нескольких чипов с различными функциями непосредственно в более эффективный чип. Другими словами, кремниевые пластины добавляются к кремнию, чтобы увеличить стоимость процесса и физические ограничения, чтобы закон Мура оставался эффективным.

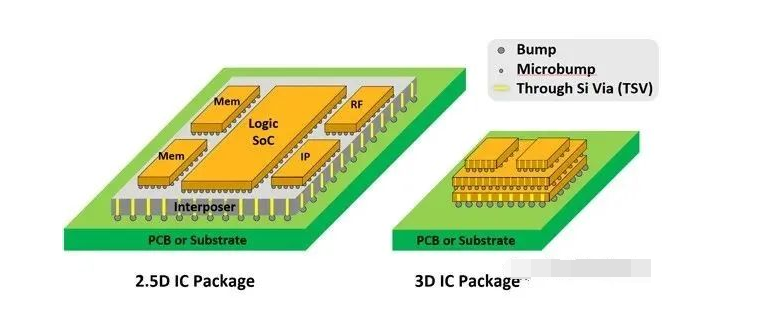

Стереоскопические инкапсуляции более знакомы с 2.5D и 3D - инкапсуляцией, здесь мы начинаем с 2.5D - инкапсуляции. Так называемая 2.5D - инкапсуляция, основная концепция заключается в размещении процессора, памяти или другого чипа на силиконовой вставке (Silicon Interposer), которая соединяется микровыпуклыми блоками, так что металлические провода внутри кремниевой вставки могут соединять электронные сигналы различных чипов. Затем TSV используется для соединения нижних металлических выпуклостей, а несущая пластина провода используется для соединения внешних металлических шаров для достижения более тесного взаимодействия между чипом, чипом и упакованной базой.

2.5D и 3D - инкапсуляция являются популярными технологиями стереоинкапсуляции. (Источник: ANSYS)

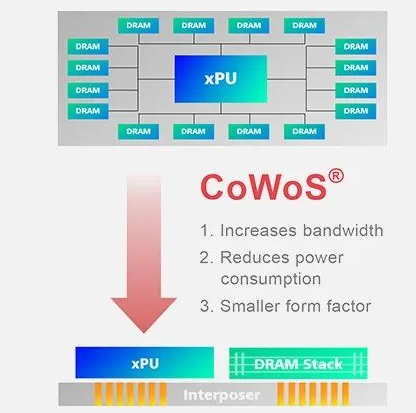

В настоящее время известная технология упаковки 2.5D - это не что иное, как CoWOS для аккумуляции электроэнергии. Концепция технологии CoWOS заключается в том, чтобы поместить полупроводниковые чипы (такие как процессоры, память и т. Д.) в кремниевый средний слой, а затем соединить их с конечной базой с помощью процесса инкапсуляции чипов на чипе (CoW). Другими словами, сначала чип подключается к кремниевому чипу с помощью процесса упаковки чипа на чипе (CoW), а затем чип CoW подключается к подложке и интегрируется в CoWOS. Используя этот режим упаковки, несколько чипов могут быть упакованы вместе и соединены между собой через кремниевый интерполятор, чтобы достичь эффекта небольшого объема упаковки, низкого энергопотребления и меньшего количества выводов.

Концепция технологии упаковки аккумуляторов. (Источник: тайваньский аккумулятор)

В дополнение к CoWos, вентиляция упаковки на уровне кристаллического круга также может быть классифицирована как метод упаковки 2.5D. Принцип упаковки на уровне вентиляционного кристалла заключается в том, чтобы вытянуть требуемую цепь из конца голого полупроводника в слой перераспределения для формирования упаковки. Поэтому нет необходимости герметизировать загрузочные пластины, провода, выпуклые блоки, что может снизить себестоимость производства на 30% или сделать чип тоньше. При этом площадь чипа может быть значительно уменьшена. Он также может заменить более дорогостоящую перфорацию из кремния для интеграции различных компонентов с помощью технологии упаковки.

Конечно, технология стереоинкапсуляции - это не только 2.5D, но и 3D инкапсуляция. Итак, в чем разница между ними, полупроводниковая промышленность принимает 3D - упаковку?

Принцип работы 3D - инкапсуляции по сравнению с 2.5D - инкапсуляцией заключается в создании транзисторной (CMOS) структуры на чипе и использовании кремниевой перфорации для подключения электронных сигналов от разных чипов вверх и вниз, что позволяет памяти или другим чипам складываться непосредственно вертикально

3D - инкапсуляция - это прямое сложение чипов. (Источник: Intel)

Tesla и Intel активно разрабатывают технологию 3D - инкапсуляции

Intel (INTC) и Taiwan Semiconductor (TSMC) имеют свои собственные технологии 3D - инкапсуляции. Intel использует технологию 3D - инкапсуляции « Foveros», которая использует логику изомерного стека для обработки операций и может складывать каждый логический чип вместе. Это означает, что впервые пакеты чипов были расширены от традиционных пассивных кремниевых сред и стеков памяти до высокоэффективных логических продуктов, таких как процессоры CPU, графики и AI. Раньше укладка использовалась только для запоминающего устройства, но теперь используется изомерная укладка для достижения укладки различных комбинаций памяти и вычислительных чипов.

Кроме того, Intel разрабатывает три новые технологии: co - EMIB, ODI и MDIO. Co - emib может подключать более высокие вычислительные мощности и позволяет соединять два или более компонентов Foveros друг с другом. Дизайнеры также могут подключать симуляторы, память и другие модули с очень высокой пропускной способностью и очень низким энергопотреблением. Технология ODI обеспечивает большую гибкость для всесторонней взаимосвязанной связи между микросхемами малого и среднего размера. Верхние чипы могут общаться с другими небольшими чипами, такими как технология EMIB, или вертикально с нижними голыми чипами через кремниевые отверстия (TSV), такие как технология Foveros.

Концепция технологии Intel Foveros. (Источник: Intel)

Технология также использует большие вертикальные проходные отверстия, которые питают энергию непосредственно от упакованной базовой пластины к верхней голой пластине. Эти большие отверстия пропускания намного больше, чем традиционные отверстия пропускания кремния, и обеспечивают более стабильную передачу мощности с более низким сопротивлением. Более высокая пропускная способность и более низкая задержка через стек. Этот метод уменьшает количество отверстий для пропускания кремния, необходимых в базовых чипах, освобождает больше площадей для активных компонентов и оптимизирует размер обнаженной пластины.

С другой стороны, TSMC предлагает интегрированные решения для « 3D мультичипов и системных интегральных чипов» (SoIC). Системно интегрированное решение на пластине накладывает хорошо известные обнаженные кристаллы разных размеров, технологий и материалов непосредственно друг на друга.

TSMC отмечает, что по сравнению с традиционными решениями для 3D - интегральных схем, использующими микровыпуклые блоки, интегральные чипы системы имеют в несколько раз более высокую плотность и скорость выпуклых блоков, при этом значительно снижая энергопотребление. Кроме того, системный интегральный чип представляет собой предварительно обработанное интегрированное решение для подключения двух или более голых кристаллов перед упаковкой; Таким образом, чипсеты системной интеграции могут использовать передовые технологии инкапсуляции InFO или CoWOS компании для дальнейшей интеграции других чипов, создавая мощные решения системного уровня « 3D * 3D».

Кроме того, TSMC представила 3DFabric, который объединяет быстрорастущие интегрированные решения для 3DIC - систем, чтобы обеспечить большую гибкость и создать мощные системы с мощными блокбастерами, соединенными друг с другом. 3DFabric имеет различные варианты сборки передних и задних чипов, которые помогают клиентам соединять несколько логических чипов вместе или даже гетерогенные микрочипы, такие как последовательное высокочастотное широкополосное запоминающее устройство (HBM) или аналоговые, входные / выходные и радиочастотные модули. 3DFabric сочетает в себе заднее и фронтальное 3D - решение и дополняет микромодель транзистора, чтобы постоянно улучшать производительность и функциональность системы, уменьшать размер и внешний вид и ускорять время выхода продукта на рынок.

После запуска 2.5D и 3D, Chiplets является одной из новейших передовых технологий упаковки, которые поражают полупроводниковую промышленность. Наконец, кратко опишите характеристики и преимущества Chiplets.

Использование Chiplets имеет три преимущества. Поскольку стоимость передовых процессов очень высока, особенно аналоговые схемы и I / O все труднее сжиматься по мере развития технологии. Чипы делят схемы на отдельные микрочипы, усиливая их функциональность, технологию и размеры, в конечном итоге интегрируя их вместе, чтобы преодолеть проблемы миниатюризации процесса. Кроме того, Chiplets может использовать существующие зрелые чипы для снижения затрат на разработку и проверку.

В настоящее время многие производители полупроводников представили высокопроизводительные продукты в виде чипов. Например, Intel Stratix 10 GX 10 - метровая FPGA имеет чиповую конструкцию, которая обеспечивает более высокую плотность компонентов и емкость. Продукт основан на существующей архитектуре Intel Stratix 10 FPGA и передовой технологии Intel Embedded Multip Internet Bridge (Emib), которая объединяет два основных логических чипа Intel Stratix 10 GX FPGA высокой плотности с соответствующими блоками ввода / вывода с использованием технологии emib. То же самое можно сказать и о процессорах AMD второго поколения EPYC. В отличие от первого поколения чипов, которые объединяют память и I / O для формирования 14 - нм CPU, второе поколение состоит в том, чтобы разделить I / O и память на один чип и разрезать 7 - нм CPU на 8 чипов для объединения.

Короче говоря, в прошлом эффективность чипа повышалась за счет улучшения полупроводникового процесса, но по мере того, как размер элемента приближался к физическому пределу, миниатюризация чипа становилась все более сложной. Чтобы поддерживать небольшие размеры и высокую эффективность конструкции чипов, полупроводниковая промышленность не только продолжает разрабатывать передовые процессы, но и улучшает архитектуру чипов, позволяя чипам переходить от оригинальных однослойных к многослойным укладкам. Таким образом, усовершенствованная упаковка также стала одним из ключевых факторов улучшения закона Мура, что привело к тенденции в полупроводниковой промышленности.

Основные задачи будущей интеллектуальной лаборатории включают: создание системы оценки IQ системы искусственного интеллекта, проведение оценки IQ мирового искусственного интеллекта; Провести программу исследований облачного мозга в Интернете (город), построить интернет (город "облачных технологий мозга и корпоративных карт, услуги для повышения уровня интеллекта в бизнесе, промышленности и городе.