本文的重點是 PCB設計師 誰使用IP, 並進一步使用拓撲規劃和路由工具來支持IP,以快速完成整個PCB設計. 從圖1可以看出, 設計工程師有責任通過安排少量必要的組件並規劃這些組件之間的關鍵互連路徑來獲得IP.

一旦獲得IP,可以將IP資訊提供給PCB設計師,PCB設計師將完成剩餘的設計。 PCB設計者進一步使用拓撲規劃和路由工具來支持IP,以快速完成整個PCB設計。 現在,不需要通過設計工程師和PCB設計師之間的互動和反覆運算過程來獲得正確的設計意圖。 設計工程師獲得了這些資訊,結果相當準確,這對PCB設計師有很大幫助。 在許多設計中,設計工程師和PCB設計師必須執行互動式佈局和佈線,這可能會為雙方消耗大量寶貴的時間。 根據過去的經驗,互動操作是必要的,但耗時且效率低下。

設計工程師提供的初步計畫只能是手動繪製,沒有適當的組件比例、匯流排寬度或引脚輸出提示。

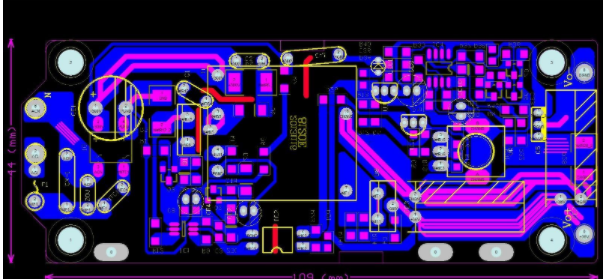

當PCB設計師參與設計時,使用拓撲規劃科技的工程師可以獲得某些組件的佈局和互連。 該設計還可能需要其他組件的佈局、其他IO和匯流排結構的收集以及所有互連的完成。

PCB設計師 需要採用拓撲規劃並與 PCB佈局 在佈局下實現組件的最佳佈局和互動規劃, 從而提高PCB設計的效率. 隨著重點區域和高密度區域佈局的完成以及拓撲規劃的獲取, 佈局可能先於最終拓撲規劃. 因此, 某些拓撲路徑可能必須使用現有佈局. 雖然他們的優先順序較低, 他們仍然需要聯系. 因此, 部分規劃圍繞生產組件的佈局展開.

此外,這一級別的規劃可能需要更詳細的資訊,以便為其他訊號提供必要的優先順序。 特定匯流排自動路由之前的一些障礙可以為算灋提供其他路由層的選項。 由於匯流排在第一層上被組織成緊密的線,設計者開始將轉換部分規劃為第3層,細節為“3”,並考慮匯流排通過PCB的距離。 注意,第3層上的拓撲路徑比頂層寬,因為它需要額外的空間來容納阻抗。 此外,該設計還指定了層過渡的確切位置(17個孔)。 當拓撲路徑從圖3的右側向下移動到詳圖“4”時,需要從拓撲路徑連接和每個組件引脚中繪製許多組織T形連接點。 PCB設計者選擇將大部分連接保持在第3層,並穿透其他層以連接元件引脚。

囙此,他們繪製了一個拓撲區域來表示從主線束到第四層(粉紅色)的連接,並將單元T形觸點連接到第二層,然後使用其他過孔連接到設備引脚。 拓撲路徑在第3層繼續到詳細資訊“5”,以連接有源設備。 然後將這些連接從有源引脚連接到有源器件下的下拉電阻器。

設計者使用另一種拓撲區域規範從第3層連接到第1層,其中元件引脚是有源器件和下拉電阻器。 這一級別的詳細規劃可以在大約30秒內完成。 在獲得該計畫後,PCB設計師可能希望立即佈線或創建進一步的拓撲規劃,然後通過自動佈線完成所有拓撲規劃。 從完成計畫到自動佈線的結果不到10秒。 事實上,這個速度並不重要。 事實上,如果忽視設計者的意圖,自動佈線的質量很差,這完全是浪費時間。 執行高品質的自動佈線大約需要10秒。 通過將抽象級別提高到拓撲規劃,整個互連時間大大縮短。 在互連開始之前,設計師真正清楚地瞭解了密度和完成設計的潜力。 例如,為什麼在設計中保持這一點? 為什麼不繼續規劃並在後面添加行? 何時規劃完整的拓撲?

如果考慮上述示例,則可以將計畫抽象用於另一個計畫,而不是17個獨立的網絡,每個網絡上有許多段和許多孔。 在考慮工程變更單(生態學、項目)時,這一概念非常重要。

工程變更單(ECO)在以下示例中,FPGA引脚輸出尚未完成。 設計工程師已將這一事實告知PCB設計師,但出於進度原因,他們需要在FPGA引脚輸出完成之前盡可能地推進設計。 在已知引脚輸出的情况下,PCB設計人員開始規劃FPGA空間,同時完成規劃,同時還考慮從其他設備引入FPGA。 IO最初計畫位於FPGA的右側,但現在位於FPGA的左側,導致引脚輸出與原始計畫完全不同。

PCB設計師 可以在設計開始時使用拓撲規劃工具, 也可以在設計工程師獲得IP後使用, 取決於誰使用這種靈活的工具來最好地適應他們的設計環境. 拓撲佈線僅遵循設計師的計畫或意圖提供 高品質PCB 接線結果. 面對ECO時, 拓撲規劃比單獨的連接操作快得多, 囙此拓撲佈線設備可以更快地採用ECO, 從而提供快速準確的結果.