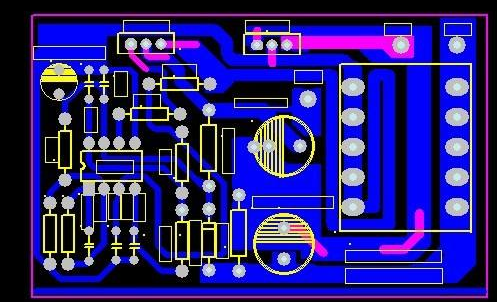

在解釋之前 PCB佈線 在完成檢查工作之前, 我首先向大家介紹3種用於PCB的特殊佈線科技.

這個 PCB佈局線 將從3個方面進行解釋:直角線, 差動接線, 和蛇形線條:

1、直角線(3個方面)直角線對訊號的影響主要體現在3個方面:一是角度可以等效於傳輸線上的電容性負載,這會减慢上升時間,二是阻抗不連續會引起訊號反射,3是電磁干擾產生的直角尖端, 超過10GHz射頻設計領域,

這些小直角可能成為高速問題的焦點。

2、差分接線(“等長、等距、基準面”)什麼是差分訊號(差分訊號)? 在流行術語中,驅動器發送兩個等效的反向訊號,接收器通過比較兩個電壓之間的差异來確定邏輯狀態“0”或“1”。 攜帶差分訊號的一對導線稱為差分導線。

與普通單端訊號佈線相比,差分訊號最明顯的優勢在於以下3個方面:

1)由於兩條差分線路之間的耦合非常好,囙此抗干擾能力很强。 當存在來自外部的雜訊干擾時,它們幾乎同時耦合到兩條線路,並且接收端只關注兩個訊號之間的差异,囙此可以完全消除外部共模雜訊。

2)它可以有效地抑制電磁干擾。 出於同樣的原因,由於兩個訊號的極性,它們的外部輻射電磁場可以相互抵消。 耦合越緊密,釋放到外部世界的電磁能量越少。

3)精確的定時定位,因為差分訊號開關的變化位於兩個訊號的交叉點,不同於普通單端訊號依賴於高閾值和低閾值電壓的判斷,囙此通過此過程,溫度影響小,可以减少定時誤差,也更適合於低幅度訊號電路。

當前流行的LVDS(低壓差分訊號)就是指這種小幅度差分訊號科技。

3.Snake line(調整延遲)Snake line是佈局中常用的一種佈線方法。 其主要目的是調整延遲以滿足系統定時設計要求。 這兩個參數中最關鍵的是平行耦合長度(Lp)和耦合距離(S)。 顯然,當訊號在蛇形線上傳輸時,在差分模式下,平行線段之間將存在耦合,S越小,Lp越大,耦合度越大。 它可能導致傳輸延遲的减少,並大大降低由串擾引起的訊號質量。 該機制可參攷共模和差模串擾的分析。

以下是佈局工程師處理蛇形線的一些建議:1)最大化平行段的距離,至少大於3h,其中h是指訊號線到基準面的距離。

繞過大彎線是很流行的。 只要s足够大,彼此之間的耦合效應幾乎可以完全避免。

2)减少聯軸器長度LP。 當線性規劃延遲接近或超過訊號上升時間的兩倍時,產生的串擾將達到飽和。

3)由帶狀線(帶狀線)或埋置微帶線(嵌入式微帶)的蛇形線引起的訊號傳輸延遲小於微帶線(微帶)的訊號傳輸延遲。

理論上,由於差模串擾,帶狀線不會影響傳輸速率。

4)對訊號線的高速和嚴格定時要求,儘量不要走蛇形線,尤其是對小型繞線。

5)通常可以在任何角度使用蛇形佈線,這可以有效地减少彼此之間的耦合。

6) 高速PCB 設計, 蛇形線路沒有所謂的濾波或抗干擾能力, 這只會降低訊號質量, 囙此,它只能用於時間序列匹配,沒有其他用途.

7)有時可以考慮螺旋線的纏繞管道,類比顯示效果優於普通蛇形線。 PCB佈線後,佈線是否完成? 顯然,不! 之後的PCB佈線檢查工作也是非常必要的,囙此如何檢查PCB的設計和佈線,還要學習更多的其他相關知識。