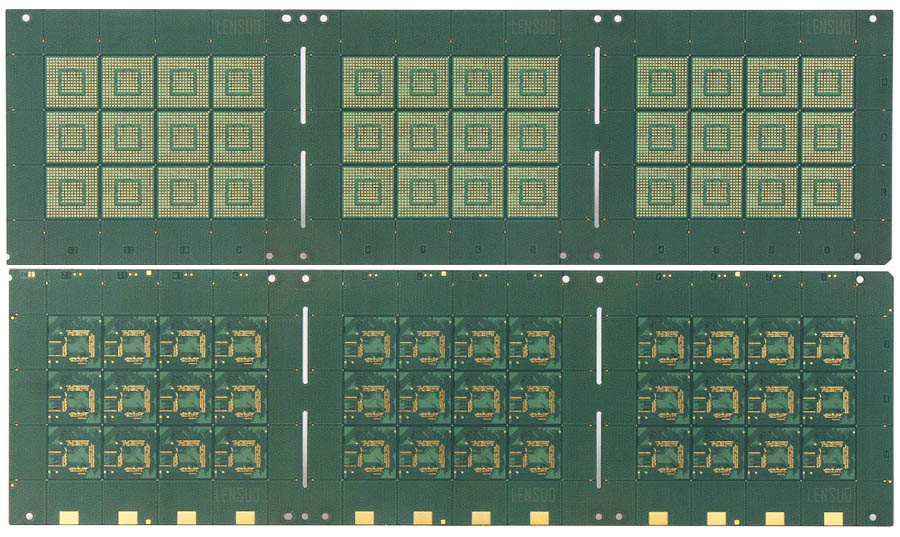

HDI IC封裝基板

lga PCB(lga IC封裝基板)

產品名稱: HDI IC封裝基板

板材:3菱無鹵燃氣BT HL832NX-A-HS

最小線寬/線距:30/30um

表面技術:鎳鈀金(ENEPIG)

板厚:0.3mm

層數:4層

孔徑:雷射孔0.075mm,機械孔0.1mm

使用: BGA IC封裝基板

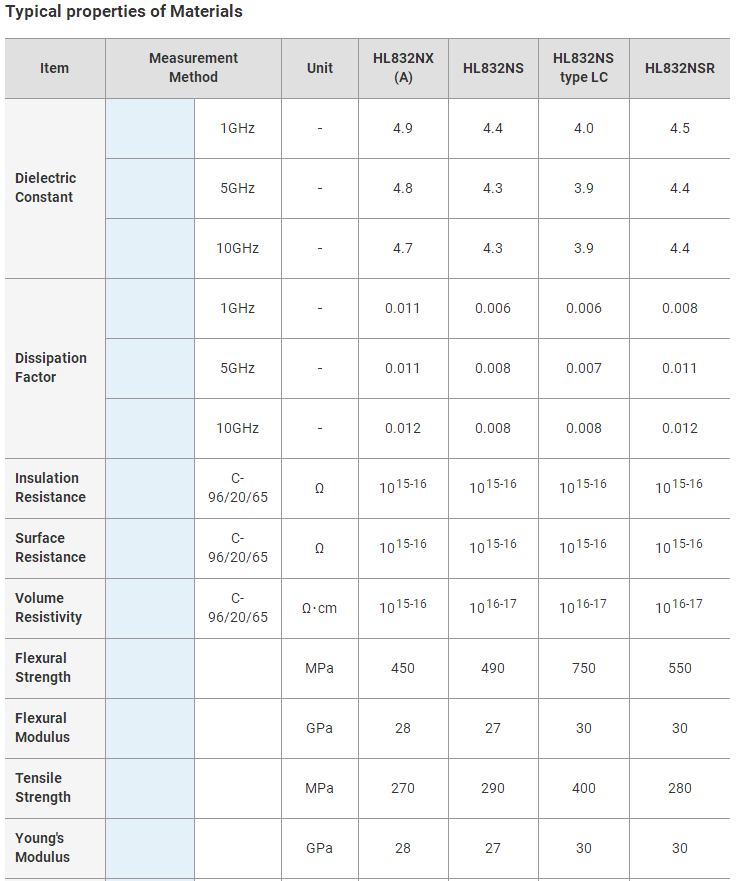

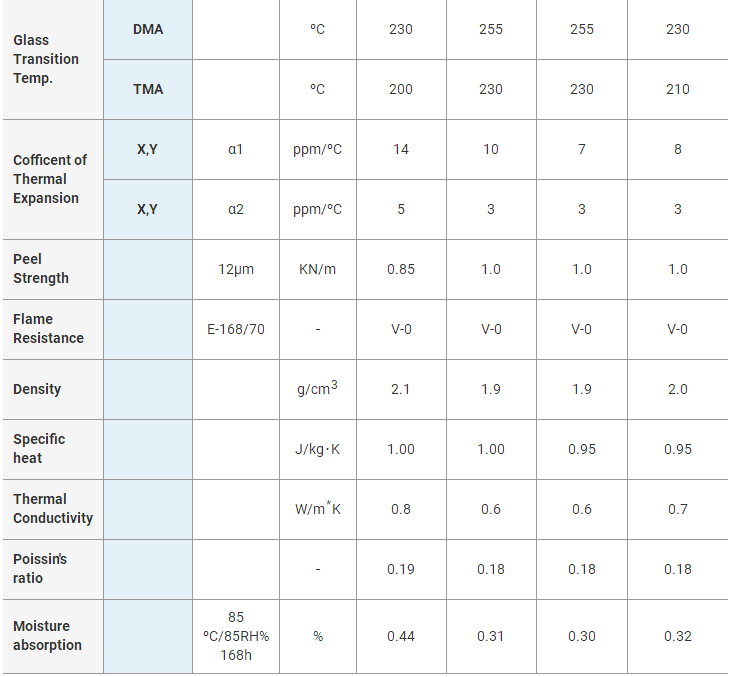

特徵 3菱燃氣英國公司 布料

3菱燃氣BT資料的特點

WLP、WLCSP體積小、重量輕

但問題來了。 雖然WLP和WLCSP的尺寸很小,但隨著常規IC引脚數量的新增,WLP和WLCSP封裝的球距要求趨於嚴格,但電路設計所需的電力效能基本上與一般IC所需的電力支撐沒有什麼不同,但WLP和WLCSP的尺寸已减小到模具尺寸。 此外,可以使用WLP和WLCSP連接到PCB的觸點和電路非常小。 在PCB的設計中,解決方案並不像一般的IC應用解決方案那麼簡單。

至於使用晶圓級封裝,目的是降低解決方案的成本和整體尺寸,但當引入晶圓級封裝時,PCB的成本必然是由於使用晶圓級封裝,必須進行相應的佈線。 隨著衝壓工藝的改進,PCB特性可以與WLP和WLCSP元件完全匹配,而不會出現連接問題。 特別是在設計方案中使用WLP和WLCSP後,PCB將變得更加複雜,其作用將變得更加重要。 在設計過程中需要仔細規劃,以避免PCB質量導致終端產品的穩定性。

當我們在設計載波板時,基本上在現有的設計產品中,可用的載波板面積已經越來越小,工程師不得不面對不斷縮小的設計要求,例如可穿戴電子產品,對於手錶和手機等電子電路來說,可用的載波板空間是極其寶貴的。 為了减少終端設計中使用的PCB面積,引入WLP和WLCSP等小型IC封裝是不可避免的設計趨勢。

晶圓階段的組件封裝大大節省了載體板的占地面積

由於WLP和WLCSP封裝是直接構建在“矽”襯底封裝工藝上的,IC基本上不需要使用鍵合線,對於高頻元件,它可以直接獲得更好的高頻電效能,並達到縮短週期時間的好處。 而且,由於包裝可以在工廠內完成,同時可以節省包裝成本,但對於工程師來說,設計計畫也必須朝著降低成本的方向考慮。 為了匹配WLP和WLCSP組件,PCB成本也必須在一定程度上受到限制。 注意折衷設計,或採用相應的電路佈局。

一般來說,要導入WLP和WLCSP組件,工程師在實施PCB電路佈局規劃之前,必須首先獲得WLP和WLCSP的封裝外形(即封裝尺寸),同時確認WLP和WLCSP組件的尺寸/接觸誤差和接觸,以及組件的關鍵資訊,如間距、啟動電路佈局、工藝組件放置、, 您可以使用獲得的元件參數進行設計和規劃,並且由於WLP和WLCSP的尺寸和接觸變得更小,囙此有必要考慮適用IC引脚的焊接。 墊子設計。

PCB需要針對SMD和NSMD形式進行微調

它可以與WLP和WLCSP焊盤類型匹配,並且可以使用定義的焊接掩模(SMD)和定義的非焊接掩模(NSMD)。 阻焊板定義型SMD焊盤設計用於使用阻焊板定義焊球和要焊接的焊盤區域。 此設計解決方案可减少在焊接或脫焊過程中拉起焊盤的可能性。 但SMD形式的缺點是,SMD减少了與錫球連接的銅表面的表面積,同時减少了相鄰焊盤之間的空間,這將限制焊盤之間的跡線寬度,也可能導致PCB打開。 該孔使用彈性。 在大多數設計方案中,更常用的仍然是SMD設計方案,因為SMD的焊盤可以具有更好的焊料連接特性,並且焊料和焊盤可以在製造過程中集成在一起。

對於非焊接掩模定義焊盤(NSMD),設計方法是使用銅進行焊接凸焊來定義焊盤區域。 這種設計方案可以提供更大的表面積來連接PCB和焊球。 同時,與SMD設計形式相比,NSMD還提供了焊盤和焊盤之間更大的絕緣距離,從而允許焊盤之間更寬的佈線間距,並且對於PCB通孔的使用具有更高的靈活性。 但是,如果NSMD正在焊接,則脫焊和其他操作很容易導致焊盤拉起。

需要特別考慮間距

間距大小的考慮也很重要,特別是當PCB是SMD或NSMD形式時,不同解決方案的預留間距大小也會略有不同,間距大小是指焊球之間的距離,是焊球中心之間距離的兩倍,間距大小越大, 焊盤和可用於佈線的焊盤之間的佈線空間越大。

對於0.5 mm的設計方案,由於間距較大,提供了更多的佈線空間,或者設計可以使用更寬的線路和更多的銅資料,這意味著可以在跡線中驅動更高的傳輸電流,並且絕緣距離也可以輕鬆完成設計。 對於絕緣距離,一般需要檢查所需的設計規範,一般絕緣距離為3~3.5密耳(mil)。 與0.4 mm節距寬度設計相比,設計難度更大,因為可用佈線空間更靈活,並且由於節距收縮,可用絕緣節距將同時减小。 這表示可以在電路中使用的銅變化。 如果較小,則傳輸的驅動電流將相應减小。

就PCB佈線而言,由於WLP和WLCSP組件的特性,可用的錫球間距非常小。 基本上,不可能使用機械開孔設備來製作PCB孔。 由於機械孔的孔徑過大,開孔過程中也可能會由於開孔過程中的錯誤而使PCB上較細的線路受損。 然而,在使用WLP和WLCSP元件的PCB中,由於電路更緊密,將使用成本更高的雷射鑽孔過孔。

一般來說,只有中高單價的終端產品才會使用高成本的雷射穿孔PCB生產解決方案,雷射穿孔也會與多層板一起使用進行生產,成本會超過四層。 這塊木板要高得多。 對於一些低成本應用,使用多層板和雷射開口設計基本上不符合成本效益。 另一個相對不常見的設計解決方案是使用WLP組件的交錯凸塊陣列,該陣列可用於交錯WLP晶片上的焊球,從而允許產品開發人員爭取更多可用空間。 執行PCB電路佈局。 但實際上,採用交錯凹凸陣列的WLP的成本相當高。 同時,在開發WLP和WLCSP組件時,必須同時考慮此解決方案。 零部件生產難度大,會新增零部件成本。

結束語

WLP和WLCSP組件的晶圓級晶片尺寸封裝對於减小最終產品的尺寸具有極好的改進效益,但作為交換,PCB設計計畫也必須同時陞級,在開發過程中使用高密度多層板和雷射開口的精密制造技術, 最初由IC組件節省的載體空間和組件成本將部分轉移到PCB設計和隨後的大規模生產中。 相反,較小的組件將用於產品的生產線。 處理或維護也會導致一些更難實施的操作問題,必須在相關設計之前逐一考慮。

WLP和WLCSP組件是晶圓級晶片尺寸封裝。 最終的IC外觀和封裝尺寸幾乎與晶片相同。 晶圓級晶片尺寸封裝具有許多優點,例如顯著减小了組件尺寸,從而减少了傳統IC。 由於面積和厚度的原因,組件重量較輕,並且組件可以通過自動送料和分模製造,更適合大規模生產線生產,這可以降低總體生產成本,甚至WLP和WLCSP組件本身的電力特性對於高頻應用來說,性能也會更好。 它用於需要重量輕、體積小的移動設備,如手機、筆記型電腦和可穿戴智慧產品。 它們都可以用來大大减少載體的面積和產品的重量。 如果WLP和WLCSP組件在引入之前可以更多地集成用於晶圓級封裝技術,例如使用重佈線層科技、凸點等。為了改進WLP和WLCSP組件的設計,WLP、WLCSP組件和PCB的組合可以更容易地集成在設計中。