串擾是指當訊號在傳輸線上傳播時,相鄰訊號之間的電磁場相互耦合產生的不良雜訊電壓訊號, 那就是, 能量從一條線耦合到另一條線. 隨著電子產品的複雜性和效能的提高, 密度 印刷電路董事會 相關設備的頻率也在不斷增加. 維護和提高系統的速度和效能已成為設計人員的一個重要問題. 訊號頻率越高, 邊緣越陡, 較小的PCB尺寸, 而佈線密度的新增都會造成高速時串擾的影響 PCB設計 顯著增加. 串擾問題是客觀存在的, 但超過一定限制可能會導致電路錯誤觸發,並導致系統無法正常工作. 設計者必須理解串擾的原理,並在設計中應用適當的方法,以儘量減少串擾的負面影響.

高速交叉繞組 PCB設計 可能由互感產生的磁場耦合引起, 或由互電容產生的電場耦合. 兩條耦合傳輸線的串擾模型. 近端串擾是指靠近干擾線驅動器的受干擾線上的串擾, 遠端串擾是指靠近干擾線接收端的受干擾線上的串擾.

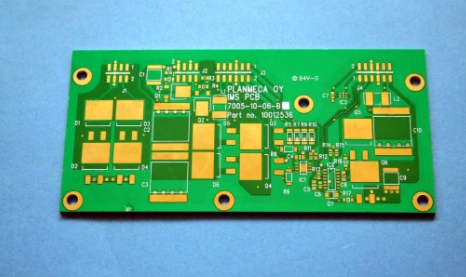

Magnetic field (inductive) and electric field (capacitive) crosstalk model diagram

Inductive coupling is the interference caused by the induced voltage on the interfered object due to the magnetic field generated by the current change on the interference source. 在線路ab-in上傳輸的訊號的磁場在線路cd上感應電壓. 干擾線可視為變壓器的一次側, 受干擾線路可被視為變壓器的二次側, 受干擾線路產生的電流在近端. 負載電阻和遠程負載電阻中的流量. Tp是輸電線路的延遲時間, Tr是驅動訊號的上升時間. 可以看出,遠端耦合產生脈寬為Tr的負脈衝, 近端耦合存儲2TP時間擴展, 其振幅保持不變, 但它們耦合串擾的總面積是相同的. The total area 屬於 crosstalk coupling is proportional to LM (dIs/dt) and coupling length.

電容耦合是由干擾源上的電壓變化引起的受干擾物體上的感應電流引起的干擾. 由電容耦合引起的每個點的波形如所示 .與互感耦合的區別在於,遠程耦合是正脈衝. The coupling crosstalk area is proportional to CM[(dv/dt) and coupling length.

電感和電容耦合串擾本質上是兩個耦合串擾疊加的結果. It can be seen from that both inductive coupling and capacitive coupling crosstalk try to enhance their effect at the near end d (they have the same polarity at point d), while at the far end c try to cancel each other's effect (their polarities at point c on the contrary). 近端串擾脈衝的幅度是恒定的, 脈衝寬度是由耦合區表示的傳播時間Tp的兩倍. 遠端脈衝的寬度約為干擾線上脈衝的上升時間Tr, 振幅隨著耦合長度的新增而新增. 在正常條件下, 在一個完整的平面上, 電感和電容串擾電壓基本相同. 中的帶狀線電路 PCB電路 具有良好的電感和電容耦合平衡, 其遠端串擾小; 用於線路的微帶, 大多數與串擾有關的電場通過空氣而不是其他絕緣材料, 所以電容串擾比電感串小, 這導致其遠端耦合為負數. 如果串擾是主要問題, 然後將所有敏感記錄道排列為帶狀線.

Mutual inductance and mutual capacitive coupling crosstalk waveform diagram

The effect of crosstalk on the system is generally negative. 在高密度和複雜環境中,不可能完全避免串擾 PCB設計. 為了减少串擾, 基本問題是使干擾源網絡和受干擾網絡之間的耦合盡可能小. 在系統設計中, 我們應該選擇適當的方法來最小化串擾,而不影響系統的其他效能. 結合以上分析, the solution to the crosstalk problem is mainly considered from the following aspects:

When the wiring conditions allow, increase the distance between the transmission lines as much as possible; or reduce the parallel length between adjacent transmission lines as much as possible (cumulative parallel length), preferably wiring between different layers;

In the case of ensuring the signal timing, 盡可能選擇轉換速度較低的設備,以減緩電場和磁場的變化速度, thereby reducing crosstalk;

The signal layer of two adjacent layers (without planar layer isolation) should be perpendicular to the routing direction, try to avoid parallel routing to reduce crosstalk between layers;

When designing the stack, 在滿足特性阻抗的條件下, the dielectric layer between the wiring layer and the reference plane (power or ground plane) should be made as thin as possible, thus increasing the coupling between the transmission line and the reference plane and reducing adjacent Coupling of transmission lines;

Because the surface layer has only one reference plane, 表面佈線的電場耦合比中間層强, so signal lines that are more sensitive to crosstalk are placed in the inner layer as much as possible;

Through termination, 傳輸線遠端和近端的阻抗與傳輸線匹配, 這可以大大降低串擾的幅度.

串擾是高速通信中一個不容忽視的問題 PCB電路 design, 它越來越受到關注. 基於數位的系統設計進入了一個新階段. 過去次要的許多高速設計問題現在對系統性能產生了關鍵影響. 包括串擾在內的信號完整性問題帶來了設計概念的變化, 設計過程, 和設計方法. 面對新的挑戰, 串擾雜訊的關鍵是找出對系統正常運行有實際影響的網絡, 而不是盲目地抑制所有網絡上的串擾雜訊, 這也與有限的佈線資源相衝突. of.