現今, 中考慮的因素 PCB設計 變得越來越複雜, 例如時鐘, 串擾, 阻抗, 偵查, 制造技術, 等., 這通常會讓設計師重複很多工作,比如佈局, 驗證, 和維護. 參數約束編輯器可以將這些參數編譯成公式, 幫助設計師更好地處理這些參數,這些參數有時甚至在設計和生產過程中相互對立.

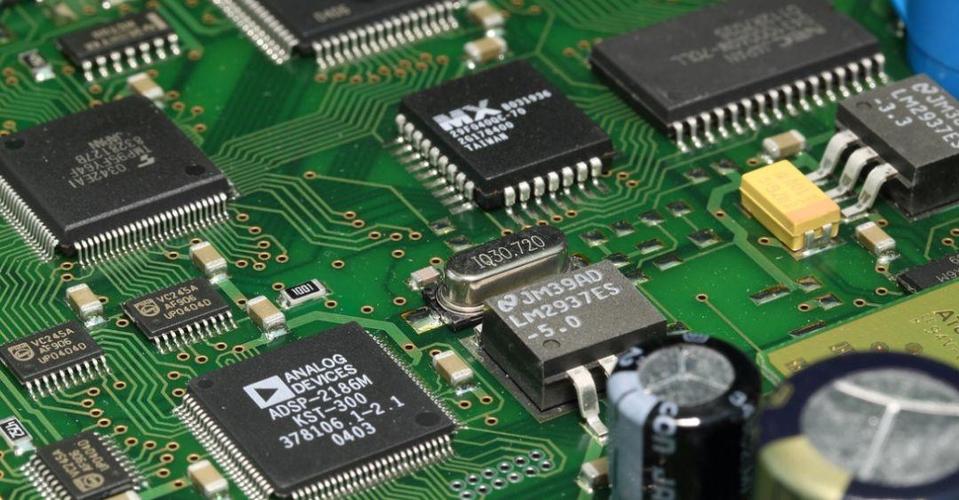

近年來, 的要求 PCB佈局 佈線變得越來越複雜. 集成電路中的電晶體數量仍在以摩爾定律預測的速度增長, 這使得器件速度更快,每個脈衝邊緣的上升時間縮短, 引脚數量也在新增. 越來越多的情况是500到2,000個針腳. 所有這些都將帶來密度, 時鐘, 以及設計時的串擾問題 PCB板.

幾年前, there were only a few "critical" nodes (net) on most PCBs, 這通常意味著它們在阻抗方面受到一些限制, 長, 和gap. PCB設計ers通常首先手動路由這些軌跡, 然後使用軟件對整個電路進行大規模自動佈線. 今天的PCB通常有5個,000個或更多節點, 其中超過50%是關鍵節點. 由於上市時間壓力, 此時無法再進行手動接線. 此外, 不僅關鍵節點的數量新增了, 但每個節點的約束也新增了.

這些約束主要是由參數的相關性和設計要求日益複雜引起的. 例如, 兩條記錄道之間的距離可能取決於與節點電壓和電路板資料相關的功能. 數位積體電路的上升時間縮短. 高時鐘速度和低時鐘速度設計都會產生影響. 因為脈衝產生得更快, 設定和保持時間較短. 此外, 互連延遲是高速電路設計總延遲的重要組成部分,對於低速設計也非常重要, 等. 等待.

如果電路板可以設計得更大,上述一些問題將更容易解决,但現時的發展趨勢恰恰相反。 由於對互連延遲和高密度封裝的要求,電路板變得越來越小,導致了高密度電路設計,同時,必須遵循小型化設計規則。 上升時間的縮短和這些小型化設計規則使得串擾雜訊問題越來越突出,球栅陣列和其他高密度封裝也會加劇串擾、開關雜訊和地面反彈。