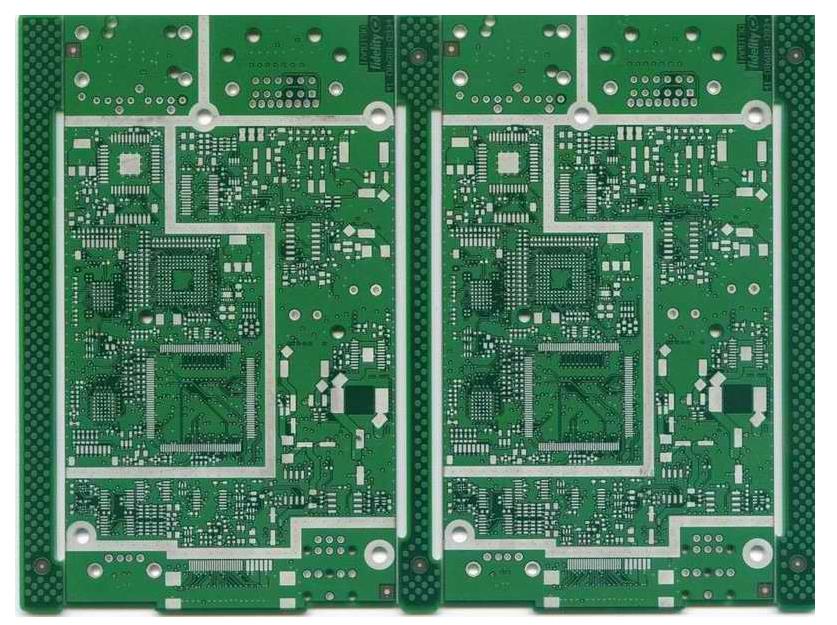

現時大多數電子產品 PCB電路板 設計是集成系統級設計, 整個項目包括硬體設計和軟體發展. 這一科技特徵給電子工程師帶來了新的挑戰. 第一, 如何在早期設計階段合理劃分系統軟硬體功能,形成有效的功能結構框架,避免冗餘的迴圈過程; 第二, 如何設計高性能和高可靠性 PCB板很快. 因為軟件的開發在很大程度上依賴於硬體的實現, 只有通過整機設計,才能更有效地縮短設計週期. 本文討論了新技術背景下系統板級設計的新特點和新策略. 眾所周知, 電子技術的發展日新月异, 這種變化的根源主要是晶片科技的進步. 電晶體工藝越來越接近物理極限,現已達到深亞微米級, 超大規模電路已經成為晶片開發的主流. 這種工藝和規模的變化給整個電子行業帶來了許多新的電子設計瓶頸. 董事會級設計也受到了很大影響. 一個明顯的變化是晶片封裝的類型非常豐富; 其次, 高密度鉛封裝和小型化封裝已成為一種時尚, 以實現整個產品的小型化, 如MCM科技的廣泛應用. 此外, 晶片工作頻率的提高使得新增系統工作頻率成為可能. 這些變化不可避免地給板級設計帶來了許多問題和挑戰. 第一, 由於高密度引脚和引脚尺寸的物理限制不斷增加, 導致低路由速率; 第二, 由於系統時鐘頻率的新增, 時機, 以及信號完整性問題; 完全複合體, 具有更好工具的高性能設計.

高速數位電路(即,高時鐘頻率和快速邊緣)的設計已成為主流。 產品小型化和高性能必須面對由同一板上的混合訊號設計科技(即數位、類比和射頻混合設計)引起的分佈效應問題。 設計難度的新增使得傳統的設計過程和設計方法以及PC上的CAD工具難以滿足當前的科技挑戰。 囙此,將EDA軟體工具平臺從UNIX轉移到NT平臺已成為業界公認的趨勢。 通常,當訊號的互連延遲大於邊緣訊號翻轉閾值時間的20%時,板上的訊號線將顯示傳輸線效應,即,連接不再是顯示集總參數的純線效能。 相反,它表現出分佈參數效應,這種設計是一種高速設計。 在高速數位系統設計中,設計者必須解决寄生效應引起的錯誤反轉和訊號失真,即時序和信號完整性問題。 現時,這也是高速電路設計者必須解决的瓶頸問題。 我們可以發現,在傳統的高速電路設計中,電力規則設定和物理規則設定是分開的。 這帶來了以下缺點:工程師必須在早期設計階段花費大量精力進行詳盡的前端(即,邏輯設定物理實現)分析,以規劃滿足電力要求的物理路由策略。 高速效果是一個複雜的主題,並且不能簡單地通過控制佈線長度和平行線來實現期望的效果。 設計師必然會面臨這樣的困境。 帶有虛假組件的物理規則不適用於實際佈線,他必須反復修改規則,使其具有實用價值。 路由完成後,可以使用驗證後工具進行分析。 但如果發現問題,工程師必須回到設計,並進行結構或規則調整。 這是一個迴圈冗餘過程。 這將不可避免地影響產品的上市時間。 當設計中只有幾個或幾十個關鍵線網時,物理規則驅動方法可以很好地完成設計任務; 但當設計中有數百甚至數千個線網時,物理規則驅動方法是基本的。 無法完成設計任務。 電子技術的發展要求出現新方法和新工具來解决設計面臨的瓶頸問題。 為了解决物理規則驅動的高速設計缺陷,一比特從事高速數位電路設計EDA工具研發的業內有識之士三年前提出了實时電力規則驅動物理佈局的概念。 進行了改革。

互連綜合是實时電力規則驅動方法的典型術語,即在物理佈局和佈線過程中,互連綜合器根據電力規則約束實时進行分析,選取滿足設計者要求的佈線策略,並使設計通過。 這種方法通過互連綜合集成電力需求和物理實現,從根本上消除了物理規則驅動方法的缺陷。 工具中的輸入雜訊約束和定時約束規則; 時序控制佈局以滿足時序約束; 執行信號完整性預優化; 板級綜合,以確保關鍵網絡滿足電力要求; 完成公共網絡的佈線; 優化。 通過由電力規則驅動的方法,可以在設計佈局之前有效地評估質量,檢測訊號失真,並確定匹配網路拓撲以及適當的端子匹配結構和電阻值。 在完成佈局和佈線後,可以執行後驗證,並且可以使用軟件示波器視覺檢測波形。 對於此時發現的定時和失真問題,可以使用路由綜合優化函數來解决。

混合訊號設計解決方案

隨著設計小型化成為一種時尚,消費者需要高性能、低價格的產品。 為了適應市場競爭,製造商要求研發人員在盡可能短的時間內開發不同類型和功能配寘的高性能、低成本產品。 產品,佔領市場。 這給設計師帶來了許多新的設計挑戰。 例如,在同一基板上使用數模混合科技甚至射頻技術,以達到小型化設計和提高產品功能的目的。 風靡全球的手機就是一個典型的例子。 該行業也有相應的解決方案-設計團隊、並行設計、派生和設計重用是典型的策略。

傳統系列設計

也就是說,在電子工程師完成所有前端電路設計之後,將其移交給物理板級設計者以完成後端實現。 設計週期是電路設計和板級設計時間的總和。 在小型化的新型並行設計成為主流設計思想和混合科技被廣泛採用後,串列設計方法有些過時。 我們必須創新設計方法,並使用强大的EDA工具協助設計師進行設計,以滿足及時市場的要求。 眾所周知,我們每個人都不可能在所有領域,也不可能在短時間內迅速完成所有工作。 設計組的概念是在這一背景下提出的,並得到廣泛應用。 現時,許多公司都採用設計團隊的方法進行協同產品開發。 即根據設計的複雜性和功能模組的差异,將整個設計劃分為不同的功能塊,不同的設計開發人員並行進行邏輯電路和PCB板設計; 然後在設計的頂層,每個模塊的最終設計結果以“設備”的管道傳遞,以合成整個板設計。 這種方法稱為PCB板設計重用。 通過這種方法不難看出,它可以大大縮短設計週期,而設計時間只是佔用大量時間的塊塊的設計時間和後端介面連接處理時間的總和。

衍生科技

以滿足不同層次用戶的需求, 專注於民用產品的製造商往往需要開發不同功能和等級的產品來佔領市場. 過去, 用於不同功能的產品開發, 我們經常使用不同的設計過程來分別實現它們, 那就是, 使用不同的設計數據生產具有不同功能的電路板以實現產品. 缺點是成本新增,設計週期延長, 同時, 產品的人為不可靠因素新增. 許多製造商現在使用衍生科技來解决上述問題, 那就是, 使用相同的設計過程數據匯出不同功能系列的產品, 從而降低成本,提高品質 PCB板.