本文解釋了限制PCB切割和粘貼能力的限制因素

給予的限制 PCB切割 and pasting capabilities

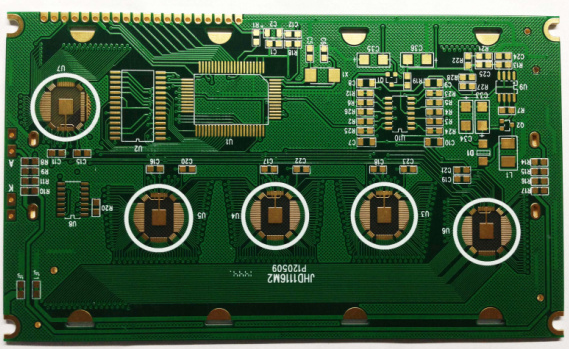

The latest form of intellectual property (IP) entering the market is simple PCB設計. 為了能够將已知的好設計轉移到新項目中, 設計自動化供應商已經安裝了軟件,允許工程師剪切和粘貼 PCB佈局.

本文解釋了限制PCB切割和粘貼能力的限制因素

由於擔心高集成度矽設計成本的快速增長,佈局工程師的短缺促使PCB領域的主要供應商對其高端工具進行改造,以彌補一些不足。

Zuken行銷總監馬克·阿什頓(Mark Ashton)說:“缺乏人才。在美國,他們現在為版面設計人員支付的費用比EEs高。”

本文解釋了限制PCB切割和粘貼能力的限制因素

設計自動化供應商認為,員工短缺正驅使客戶尋求更高水准的自動化。 囙此,20世紀90年代中期的約束管理概念(在每個PCB軌跡上設定規則以確保正確的佈線)又回來了。

本文解釋了限制PCB切割和粘貼能力的限制因素

Cadence Design Systems為約束管理提供了新的支持,從原理圖捕捉到佈局,再到Allegro軟件的14.0版本。 祖肯集團計畫在今年晚些時候將約束管理系統推廣到HotStage 4。

本文解釋了限制PCB切割和粘貼能力的限制因素

他們希望解决的問題來自PCB上仍然存在的大量關鍵記錄道。 阿什頓說:“[晶片上系統]的發展速度沒有人們預期的那麼快。人們正在使用多個現成的晶片,因為開發SoC的成本非常低。

“你必須對市場預測充滿信心,才能選擇SoC設計,而不是收集更便宜的現成零件。

本文解釋了限制PCB切割和粘貼能力的限制因素

“但仍有縮小和加快的趨勢。在某些情况下,電路板比預期的所有組件都小,囙此它們進入PCB本身。”

本文解釋了限制PCB切割和粘貼能力的限制因素

加裏·欣德, Cadence PCB Group歐洲行銷經理, 說:“PCB佈局 可以是IP. 這成為區別供應商的一個因素."

本文解釋了限制PCB切割和粘貼能力的限制因素

通過將約束與已知良好佈局相結合,Hinde表示,可以將設計轉移到新產品上,並且仍然希望在信號完整性分析的幫助下對其進行路由,從而通過自動化工具有效地實現這一目標。

本文解釋了限制PCB切割和粘貼能力的限制因素

推動信號完整性分析已擴展到低端產品。 對於最新發佈的Cadstar,Zuken已經將其通過iCases獲得的部分EMC科技推廣到路由引擎。 Cadstar 4.5中的EMC檢查軟件首先識別關鍵網絡,然後分析這些網絡在路由後是否會導致問題。