主要限制因素 PCB線上功能 測試系統是指駕駛員的倒車吸收能力/放電電流過大, 從而覆蓋了被測晶片輸入引脚的故障現象. 例如, the input pin impedance of most chips is very high (greater than 1 megaohm). 如果輸入引脚的內部功能損壞, 引脚阻抗可降低至約20歐姆, 這將導致驅動輸入引脚的晶片出現扇出問題, 電路故障是因為大多數晶片只能驅動約10 mA的輸出電流. 然而, 通用反向驅動測試儀器可以驅動阻抗為20歐姆的輸入引脚, 這使得具有故障輸入引脚的晶片能够通過功能測試. QT200 can drive nodes above 8 ohms (less than 8 ohms are regarded as short circuits), 這是這個系統的主要問題.

PCB測試失敗的原因:

晶片功能損壞

速度/計時問題

晶片引脚狀態(浮動、高阻抗、,

時鐘,非法連接)

OC門行或狀態

扇出問題

ICFT測試結果的分類

測試通過

測試失敗

設備未經過全面測試

設備相同

設備比較不同

(2) How to deal with different PCB測試結果

出現“測試失敗”結果時

檢查測試夾具是否連接到錯誤的晶片,以及是否與測試晶片連接良好。 檢查引脚狀態視窗中是否有打開的引脚(顯示HIZ),以及是否檢測到電源引脚。 糾正這些問題後重新測試。

如果結果仍然是“測試失敗”,請將滑鼠移動到引脚狀態視窗,然後按一下左鍵以顯示引脚阻抗。 將具有誤差的管脚阻抗與具有相同功能的另一管脚阻抗進行比較。 如果晶片的某個輸出引脚出現測試錯誤,請檢查該引脚的阻抗是否與其他輸出引脚一致(注意,此時的阻抗是晶片通電時量測的接地阻抗)。

如果比較的阻抗大致相等,則降低測試時基或閾值,然後再次測試。 如果這次測試通過,則意味著晶片的測試錯誤是一個計時問題。 這可能是輸出引脚連接到電容設備。 由於電容器的放電過程,輸出引脚的狀態變慢。 如果調整時基或閾值後的測試可以通過,您可以90%確定設備沒有損壞,此時您可以去測試下一個晶片。

如果在調整時基或閾值後測試仍然失敗,請檢查是否需要隔離。 如果不需要隔離,請直接轉至步驟5。

如果從夾具狀態可以看出測試失敗的原因是輸出引脚無法達到正常邏輯電平,則降低測試閾值並再次測試。 如果此時可以通過具有鬆散閾值的測試,則意味著連接到晶片的負載太重,或者晶片本身的輸出驅動能力已經退化,並且無法吸收或放電正常負載所需的電流。 發生這種情況時,用戶必須特別注意。 解決方案是在測試板通電或未通電時重新測試輸出引脚對地的阻抗。 您也可以在測試板上使用QSM/VI方法。 測試晶片每個輸出引脚在通電和斷電兩種狀態下的VI曲線。

比較每個輸出引脚對地的量測阻抗。 如果在沒有電源的情况下測得的阻抗大致相同,並且當電源接通時,具有測試誤差的輸出引脚的阻抗高於其他輸出引脚的阻抗,則表示晶片功能受損(高阻抗狀態無法吸收或放電所需電流),應更換晶片。

比較每個輸出引脚的VI曲線,如果某個輸出引脚的阻抗明顯低於其他輸出引脚的阻抗,則意味著問題在於連接到該引脚的扇出負載。 檢測連接到此引脚的所有晶片輸入引脚的阻抗,並找出真正的短路點。

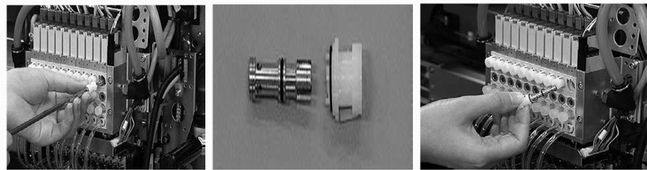

為了進一步找出問題的根本原因,可以使用扁嘴鉗夾住有測試錯誤的測試晶片上的輸出引脚,然後重新測試。 如果此時測試通過,則表明連接到晶片的負載確實存在問題。

2當“設備未完全測試”的結果出現時

當測試過程中被測晶片的輸出引脚未翻轉(即在測試視窗中保持固定的高電位或低電位)時,系統將提示“設備未完全測試”(提示出現時荧幕上的波形視窗不會出現)標記任何測試錯誤。 例如,7400反及閘的輸入引脚對地短路,相應的輸出引脚始終為高電平,測試晶片時會出現上述提示。

如果用戶有被測板的PCB原理圖,他可以輕鬆確定晶片的引脚連接狀態是否正常。

如果用戶已經學習了一個良好的電路板,也將記錄學習晶片的正常連接狀態。 當測試壞板時,系統會自動將學習結果與好板進行比較。 如果比較結果不同,則表示壞板存在非法連接; 如果比較結果相同,您可以忽略“device not fully tested”(設備未完全測試)提示,然後繼續測試下一個晶片。

如果被測晶片是一個OC設備,並且被設計為 PCB電路, 晶片的輸出可能會受到與之有導線或關係的其他晶片的影響. 例如, 如果某個晶片的輸入邏輯使其輸出固定在低電平, 測試晶片的輸出也將固定在低電平. 此時, 測試晶片系統也會提示“設備未完全測試”. 此類設備的用戶應特別注意. 建議使用QSM/通過比較測試晶片上所有相同功能引脚的VI曲線來判斷PCB故障點的VI方法.