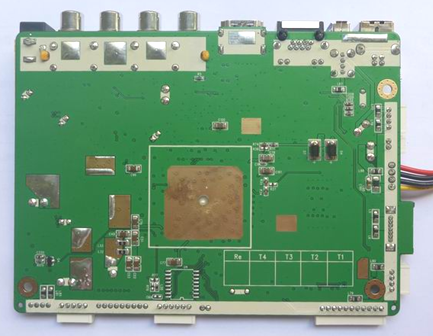

1 PCB維護 實例

重要提示:

晶片引脚對地或電源短路時,短路電阻值在10-25毫歐姆之間。

一英寸長的連接銅線的電阻約為40-50毫歐姆。

例如:當74640執行線上功能測試時,其針腳6顯示接地電阻為1歐姆,使用QT50量測的第6個針腳上的接地電阻約為160毫歐姆。 懷疑是由連接到它的其他設備引起的短路故障。 QT50檢查後,發現晶片與電阻組和設定開關相連。 開關觸點處測得的對地電阻約為40毫歐姆,低於針腳6上測得的電阻,囙此這意味著晶片顯示的針腳6對地短路故障是因為設定開關接地。 這不是晶片本身的故障。

在正常情况下,匯流排設備的引脚在設計中沒有(或很少)接地和電源。 如果有引脚接地或電源,請再次測試設備。

在沒有好的電路板供參考和比較的情况下,也可以通過分析引脚狀態和實際測量的波形來修復壞的電路板。 例如,許多晶片在電路設計中僅使用部分邏輯單元,其餘未使用部分的輸入引脚通常接地,以防止該部分處於隨機操作狀態並對電路造成干擾。 根據晶片的邏輯功能分析實際輸出波形將有助於判斷被測晶片是否真的損壞。

示例1:74123(單穩態諧振器)引脚出現浮動(FLT)

在線上功能測試中,設備的輸入引脚通常顯示為高阻抗狀態(電阻值大於1兆歐)。 當設備離線測試時,如果未連接TTL或CMOS負載,則會出現此結果。 在線上測試中,晶片的輸入引脚通常連接到另一個晶片的輸出引脚。 為了確保晶片的輸出引脚驅動扇出負載,通常為低阻抗。

線上測試中, 如果輸入引脚在引脚狀態視窗中顯示“FLT”, 這意味著引脚處於浮動狀態, 引脚可以連接到電路板或3態器件的邊界連接端, 或者連接到 PCB電路板. 開路.

通過與其他輸入引脚的狀態進行比較,可以判斷該引脚的狀態是否正常。

在本例中,第6個引脚連接到RC電路的輸入端子。 電路中的電容器通過電阻器充電,然後通過晶片的第6個引脚放電。 然後,輸入引脚不能處於高阻抗狀態,因為如果是高阻抗,則無法對電容器放電。 在晶片上執行ICFT時發生測試錯誤。 第7個引脚顯示“FLT”,另一個相同的輸入引脚(引脚15)顯示正常邏輯電平(對地阻抗約為550歐姆)。 雖然QT200在晶片上的測試結果為“測試失敗”,但晶片的輸出引脚翻轉,囙此似乎是一個時序問題。 如果用戶沒有注意,測試結果將被忽略,並被視為時間問題。

以上分析表明,用戶仔細觀察和分析引脚狀態資訊,這對於判斷真正的故障點至關重要。 如果輸入引脚的輸入阻抗為550歐姆,則不會處於浮動狀態(FLT)。 本例中故障的實際原因是單穩態諧振器由於其功能損壞而無法正常放電。

類似地,設備的輸出引脚不能處於浮動狀態(FLT),因為如果處於浮動狀態,引脚不能吸收或放電電流,也不能驅動任何扇出負載。 此外,用戶還應注意:任何節點對地的阻抗不得小於5-10歐姆(除非節點確實對地短路,否則此時阻抗約為2歐姆)。 在邏輯低狀態下,常用的緩衝驅動器的阻抗約為15-17歐姆。

例2:由於接觸不良,測試儀的電源夾具無法提供測試電源

當通過測試儀的電源夾具和被測板上的晶片向被測板供電時,有時會發現被測晶片電源引脚的量測電壓僅為4.5V,此時的測試結果往往不穩定。 出現這種情況的原因可能是晶片引脚氧化,導致測試儀的電源夾具無法與晶片引脚良好接觸。 當這種問題發生時,用戶可以採取不同的方法來解决。 最有效的方法是通過被測板的邊界將測試儀的電源端子連接到測試儀的電源電纜。

例3:當被測板通電時,晶片的某個引脚對地短路

這種現象很難解决。 測試結果表明,被測晶片輸出引脚的阻抗為10歐姆(低阻抗狀態),並且沒有翻轉動作。 當其邏輯低時,阻抗小於正常緩衝驅動器輸出引脚的阻抗。 斷開測試板的電源時,使用3米量測引脚是否對地短路(電阻大於1千歐姆)。

這種短路現象僅在被測板通電時發生,這可能是被測設備的輸出端或連接到輸出端的設備的輸入端的原因。 當邏輯低時,被測設備的輸出端應能够吸收電流,當邏輯高時,其向扇出設備的輸入引脚輸出電流。

例4:當被測板未通電時,3個晶片的一個引脚均對地短路

如果被測設備通電時內部對地短路,則在未通電的情况下,量測中將不會對地短路。 在這種情況下,可以使用毫歐錶量測被測設備的輸出引脚對地電阻,以及連接的扇出設備的輸入引脚對地電阻。 電阻最小的量測點是實際損壞的設備。

具體現象是,在ICFT期間,測試板上有3個晶片出現“測試失敗”,匯流排設備74374的第二個引脚、74244的第18個引脚和其他74244引脚顯示在引脚狀態視窗中。 針腳3分別對地短路。

首先找出距離PCB短路點最近的晶片。 使用QT50短路跟踪器進行測試時,將測量範圍設定為200毫歐姆,量測3個晶片的短路引脚對地電阻,並找到電阻最低的引脚。 方法是:將一個探針連接到被測板的電源接地,將另一個探針連接到74374的第二個引脚,量測電阻為160毫歐姆,然後連接到74244的第18個引脚,量測電阻為90毫歐姆,然後連接到另一個74244的第3個引脚,量測電阻為10毫歐姆。 那麼這個引脚就是導致匯流排錯誤的短路點。

下麵的問題是確定真正的短路點是在74244內還是在連接到斷路器外部的銅線上 PCB短路引脚. 方法是:使用QT50的一個探頭接地, 將另一個探針連接到74244的第3個引脚的焊點上方, read the resistance of this pin to ground (about 10 milliohms), 然後將探針筆連接到第3個引脚焊點外3-4 mm的連接銅線上, and then read the resistance value of the 3rd pin to the ground at this time (about 6 milliohms). 該結果表明,真正的短路點是連接到引脚3的外部銅線.