IC đóng gói Substrate Nhà sản xuất: Danh sách các công nghệ đóng gói chip

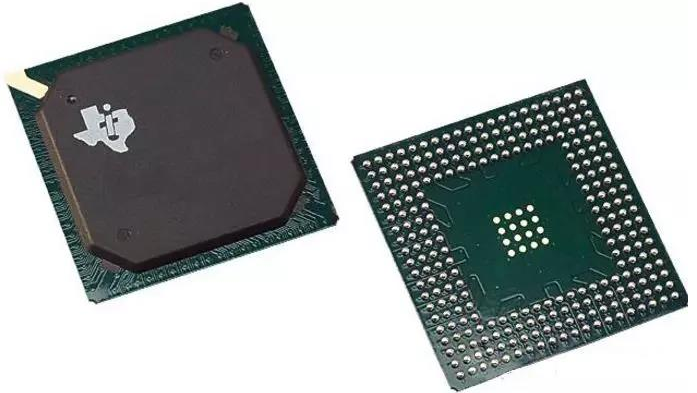

1. Mảng lưới bóng BGA

CPAC (Global Top Pad Array Carrier) là viết tắt của cụm từ CPAC (Global Top Pad Array Carrier). Màn hình tiếp xúc hình cầu, một trong những gói gắn trên bề mặt. Mặt sau của IC PCB tạo ra các vết lồi hình cầu dưới dạng màn hình thay vì pin. Các chip LSI được lắp ráp ở mặt trước của PCB, sau đó mô hình được ép vào nhựa tự nhiên hoặc được niêm phong bằng cách đổ. Còn được gọi là Convex Start Display Carrier (PAC). Nó có hơn 200 chân và là một gói cho LSI đa chân. Các gói cũng có thể được thực hiện nhỏ hơn so với QFP (gói phẳng bốn chân). Ví dụ: BGA cho 360 chân với khoảng cách lõi 1,5mm chỉ có hình vuông 31mm; QFP cho chân 304 với khoảng cách lõi 0,5mm là hình vuông 40mm. Và BGA không phải lo lắng về các biến thể pin giống như QFP.

Được phát triển bởi công ty Motorola của Mỹ, gói phần mềm này ban đầu được phát hiện hoạt động trên các thiết bị như điện thoại di động và nhanh chóng trở nên phổ biến trong máy tính cá nhân. Ban đầu, chiều dài lõi pin (lồi) của BGA là 1,5mm và số pin là 225. Ngoài ra còn có một số nhà sản xuất LSI đang phát triển BGA 500 chân. Vấn đề với BGA là kiểm tra sự xuất hiện sau khi hàn trở lại. American Motorcycle Ola Enterprises ép mô hình này vào một gói nhựa tự nhiên được gọi là MPAC và gọi phương pháp niêm phong của nó là GPAC.

2. C - (gốm sứ)

Một dấu hiệu được sử dụng để biểu thị một gói sứ. CDIP là viết tắt của Ceramic DIP. Đây là một biểu tượng thường được sử dụng trong thực tế.

3. COB (chip trên bảng)

Chip trên bảng

Đóng gói chip trên bảng là một trong những công nghệ gắn chip trần. Gắn chip bán dẫn vào bảng mạch in, kết nối điện của chip với chất nền được thực hiện thành công một cách hợp pháp thông qua đường may chì và độ tin cậy được phủ bằng nhựa tự nhiên. Mặc dù COB là công nghệ lắp đặt tấm trần đơn giản nhất, mật độ đóng gói của nó thấp hơn nhiều so với TAB và công nghệ hàn ngược

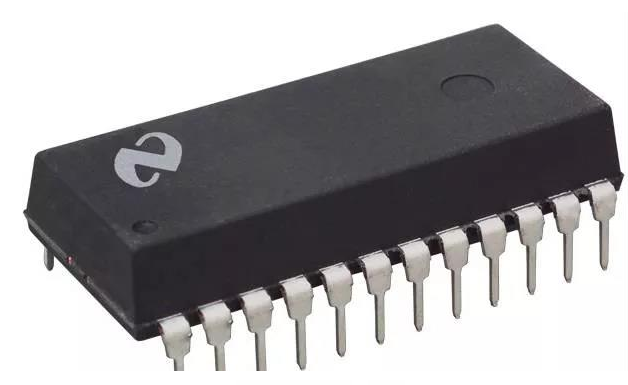

4. DIP (đóng gói trực tiếp hai cột)

Bao bì hai cột thẳng. Pin được rút ra từ cả hai bên của gói. Vật liệu đóng gói là nhựa tổng hợp phân tử và gốm sứ. Các nhà sản xuất bán dẫn Europa sử dụng DIL. DIP là gói plugin phổ biến nhất cho các ứng dụng như IC suy nghĩ tiêu chuẩn, LSI lưu trữ, mạch đánh dấu, v.v. Khoảng cách lõi pin 2,54mm và số lượng pin từ 6 đến 64. Chiều rộng gói thường là 15,2mm. Một số gói có chiều rộng 7,52mm và 10,16mm được gọi là SK-DIP (Skinny Dual In Line Package) và SL-DIP (Slim Dual In Line Package). Nhưng hầu hết mọi thứ được gọi chung là DIP. Ngoài ra, một DIP gốm được niêm phong chặt chẽ với kính điểm nóng chảy thấp còn được gọi là Cerdip.

4.1 DIC (Bao bì gốm hai cột thẳng)

Một tên khác cho DIP (đóng gói bằng kính) trong vỏ gốm.

4.2 Cerdip:

Gói thủy tinh Gốm sứ hai hàng thẳng gói cho ECLRAM, DSP (Bộ xử lý tín hiệu kỹ thuật số) mạch. Cerdip với cửa sổ kính được sử dụng cho EPROM loại tẩy UV và mạch đánh dấu với EPROM bên trong, v.v. Khoảng cách lõi pin 2,54mm, số pin từ 8 đến 42. Trong Toyo, gói này được biểu thị là DIP-G (G cho kính kín).

B5-03=giá trị thông số Ki, (cài 3)

Thu nhỏ DIP. Một trong những đóng gói hộp, giống như DIP, nhưng khoảng cách lõi pin (1,778mm) nhỏ hơn DIP (2,54mm)

Đó là tên của nó. Số pin từ 14 đến 90. Có hai loại gốm sứ và nhựa tổng hợp phân tử. Còn được gọi là Sh-dip (co lại hai cột thẳng đóng gói)

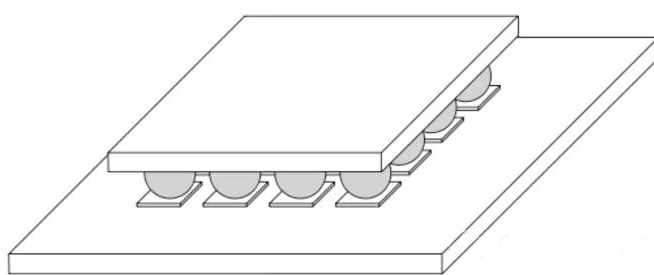

5. Flap tấm

hàn ngược của chip. Một trong những kỹ thuật đóng gói chip trần, trong đó các vết lồi kim loại được tạo ra trong vùng điện cực của chip LSI, sau đó được gắn vào vùng điện cực của chất nền in bằng hàn áp lực. Kích thước của mặt phẳng chiếm đóng hoặc bề mặt của vật thể được đóng gói về cơ bản giống như kích thước của chip. Đây là công nghệ nhỏ nhất và mỏng nhất trong tất cả các công nghệ đóng gói. Tuy nhiên, nếu hệ số giãn nở nhiệt của chất nền không giống như của chip LSI, phản ứng sẽ xảy ra tại khớp và do đó độ tin cậy của khớp sẽ bị ảnh hưởng. Điều này là do chip LSI phải được tăng cường bằng nhựa tự nhiên và sử dụng hệ số giãn nở nhiệt của vật liệu cơ bản.

6, FP (đóng gói phẳng)

Gói phẳng. Một trong những gói được cài đặt bên ngoài. QFP hoặc SOP (xem QFP và SOP). Các nhà sản xuất chất bán dẫn địa phương sử dụng tên này vì họ thấy phù hợp.

7, H- (với tản nhiệt)

Biểu thị dấu hiệu với bộ tản nhiệt. HSOP là viết tắt của SOP with Radiator.

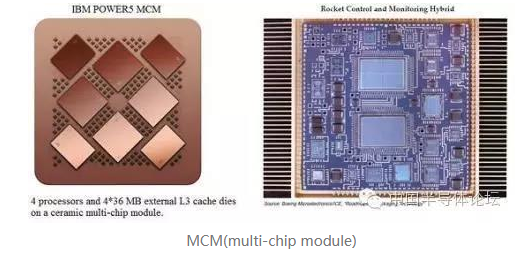

8, MCM (mô-đun đa chip) linh kiện đa chip

9, P- (nhựa)

Dấu hiệu trong bao bì nhựa đại diện cho các hợp chất phân tử. Chẳng hạn như DIP nhựa tổng hợp phân tử thể hiện bởi PDIP.

10, Lưng lợn

Gói đã nạp. Gốm sứ gói với ổ cắm, hình dạng tương tự như DIP, QFP, QFN. Được sử dụng để phát triển các cơ sở có logo để xác nhận rõ ràng hoạt động của các thủ tục uy tín. Ví dụ, cắm EPROM vào ổ cắm để điều chỉnh. Loại bao bì này về cơ bản đều là sản phẩm cố định, thị trường không lưu thông nhiều.

QFP (Quad Flat Package) 4 chân phẳng

Gói phẳng hình tứ giác

Là một gói gắn bên ngoài, các chân được kéo ra từ bốn bên và có hình dạng cánh mòng biển (L). Chất nền có ba loại gốm sứ, kim loại và nhựa tổng hợp phân tử. Từ số lượng bao bì nhựa, các hợp chất phân tử chiếm phần lớn. Khi vật liệu không có biểu hiện đặc biệt, nó thường là nhựa tổng hợp phân tử QFP. Nhựa tổng hợp phân tử QFP là gói LSI đa chân phổ biến nhất. Nó không chỉ được sử dụng trong các mạch LSI có quy luật suy nghĩ kỹ thuật số như bộ vi xử lý, màn hình cửa, mà còn cho các mạch LSI tương tự như xử lý tín hiệu VTR, xử lý tín hiệu âm thanh, v.v. Pin Core Pitch 1.0mm, 0.8mm, 0.65mm, 0.5mm, 0.4mm, 0.3mm và các thông số kỹ thuật khác. Số pin tối đa trong thông số kỹ thuật Core Pitch 0,65mm là 304.

Một số nhà sản xuất LSI gọi QFP với khoảng cách lõi pin 0,5mm cụ thể là QFP co lại hoặc SQFP, VQFP. Nhưng một số nhà sản xuất đặt khoảng cách lõi 0,65mm và 0,4mm từ QFP (còn được gọi là SQFP) với nhau, làm cho tên của họ hơi không phù hợp với thông số kỹ thuật.

QFP bổ sung với khoảng cách lõi 0,65mm và độ dày cơ thể từ 3,8mm đến 2,0mm được gọi là MQFP (gói bốn mặt phẳng theo hệ mét) theo tiêu chuẩn JEDEC (Ủy ban thiết bị điện tử). 55mm, 0.4mm, 0.3mm, v.v. QFP nhỏ hơn 0.65mm được gọi là QFP (FP) (QFP Fine Pitch), với khoảng cách lõi nhỏ từ QFP. Còn được gọi là FQFP (Thin Pitch Four Flat Packing). Nhưng bây giờ việc thực hiện các thông số kỹ thuật hình thức QFP của Hiệp hội Công nghiệp Máy móc Điện tử Toyo đã có một danh tiếng mới. Không có sự khác biệt về khoảng cách lõi pin, nhưng theo độ dày của gói, nó được chia thành ba loại: QFP (dày 2.0mm~3.6mm), LQFP (dày 1.4mm) và TQFP (dày 1.0mm).

11.1 BQFP (gói bốn mặt phẳng với bội thu)

BQFP

Bao bì phẳng pin bên của chúng tôi với đệm giảm thiểu xung đột. Một trong những gói QFP có phần nhô ra (đệm giảm xung đột) ở bốn góc của thân gói để tránh uốn cong pin trong quá trình vận chuyển. Các nhà sản xuất chất bán dẫn của Mỹ sử dụng gói này chủ yếu trong các mạch như vi xử lý và ASIC. Khoảng cách lõi pin là 0,635mm và số lượng pin thay đổi từ 84 đến khoảng 196.

11.2 QIC (Gói gốm bốn dây)

Một cái tên khác cho gốm QFP. Một cái tên mà các nhà sản xuất chất bán dẫn địa phương cho là phù hợp.

11.3 QIP (Bao bì nhựa bốn dây)

Bí danh của nhựa tổng hợp phân tử QFP. Một cái tên mà các nhà sản xuất chất bán dẫn địa phương cho là phù hợp.

11.4 PFPF (Bao bì nhựa phẳng)

Bao bì nhựa tổng hợp phân tử phẳng. Bí danh của nhựa tổng hợp phân tử QFP. Một cái tên mà nhà sản xuất LSI địa phương cho là phù hợp.

11.5 QFH (gói cao bốn mặt phẳng)

Bốn bên pin dày cơ thể phẳng đóng gói. Một hợp chất phân tử của nhựa QFP, để tránh phá vỡ cơ thể đóng gói, cơ thể QFP được làm dày hơn. Một cái tên mà các nhà sản xuất chất bán dẫn địa phương cho là phù hợp.

11.6 CQFP (gói bốn Fiat với vòng bảo vệ)

Bốn bên pin phẳng đóng gói với vòng chăm sóc tốt nhất. Nhựa tổng hợp phân tử QFP, một trong những pin với nhựa tự nhiên càng nhiều càng tốt để chăm sóc nơi trú ẩn của vòng, tránh biến dạng uốn. Trước khi LSI được lắp ráp trên bề mặt in, chân được cắt từ vòng chăm sóc tối ưu và được tạo thành hình dạng cánh mòng biển (loại L). Loại bao bì này đã được sản xuất hàng loạt tại công ty xe máy Ola của Mỹ. Khoảng cách lõi pin là 0,5mm và số lượng pin tối đa là khoảng 208.

11.7 MQUAD (tứ giác kim loại)

Olin Corporation của Mỹ đã phát triển gói QFP. Các cơ sở và nắp được coi là phù hợp và nhôm được sử dụng, được niêm phong chặt chẽ bằng chất kết dính. Trong điều kiện làm mát bằng không khí tự nhiên, công suất 2,5W~2,8W có thể được cho phép. Doanh nghiệp công nghiệp điện nhẹ mới Toyo được nhượng quyền sản xuất vào năm 1993

11,8 lít - 4 xi lanh

Gốm sứ là một trong những QFP. Nhôm nitride là chất nền đóng gói, độ dẫn nhiệt cơ bản gấp 7~8 lần so với nhôm oxy, có hiệu suất tản nhiệt tốt hơn. Khung của gói là oxit nhôm và chip được niêm phong chặt chẽ bằng cách làm đầy, do đó hạn chế chi phí. Nó là một gói phần mềm được phát triển cho Law of Thinking LSI, cho phép sử dụng năng lượng W3 trong điều kiện làm mát không khí tự nhiên. Gói LSI Mindrule 208 pin (khoảng cách lõi 0,5mm) và 160 pin (khoảng cách lõi 0,65mm) đã được phát triển và sản xuất hàng loạt bắt đầu vào tháng 10 năm 1993.

11.9 Cerquad

Một trong những gói bên ngoài, dưới QFP gốm đóng kín, được sử dụng để đóng gói mạch LSI của các quy luật tư duy như DSP. Cerquad với Windows được sử dụng để đóng gói mạch EPROM. Hiệu suất tản nhiệt của nó tốt hơn so với chất dẻo tổng hợp phân tử QFP, có thể cho phép công suất 1,5~2W trong điều kiện làm mát bằng không khí tự nhiên. Nhưng chi phí đóng gói gấp 3-5 lần so với QFP nhựa tổng hợp phân tử. Khoảng cách lõi pin là 1.27mm, 0.8mm, 0.65mm, 0.5mm 0.4mm và các thông số kỹ thuật khác. Số pin là từ 32 đến 368.

QFG (Quad Flat J-Leaded Package) Bao bì phẳng 4 chân J

Một trong những gói được cài đặt bên ngoài. Các chân được rút ra từ bốn mặt của bao bì trong một hình chữ J xuống. Là tên do Hiệp hội Công nghiệp Cơ khí Điện tử Đông Dương quy định. Khoảng cách lõi pin 1,27mm. Vật liệu có sẵn trong nhựa tổng hợp phân tử và gốm sứ.

Nhựa tổng hợp phân tử QFJ chủ yếu được gọi là PLCC (Plastic Lead Chip Carrier), được sử dụng trong các mạch như dấu hiệu, hiển thị cửa, DRAM, ASSP, OTP, v.v. Số pin từ 18 đến 84.

Ceramic QFJ còn được gọi là CLCC (Ceramic Lead Chip Carrier) và JLCC (J Leaded Chip Carrier). Đóng gói cửa sổ được sử dụng cho EPROM loại xóa UV và mạch chip đánh dấu với EPROM. Số pin là từ 32 đến 84.

13. QFN (gói không dây bốn mặt phẳng)

Gói phẳng không có chân bốn cạnh là gói gắn bên ngoài được sử dụng cho gói IC tốc độ cao và tần số cao. Nó thường được gọi là LCC. QFN là tên do Hiệp hội Công nghiệp Máy móc Điện tử Toyo quy định. Cả bốn mặt của gói đều có tiếp xúc điện cực, vì không có chân, kích thước của giá đỡ chiếm bề mặt của mặt phẳng hoặc vật thể, nhỏ hơn kích thước của QFP và thấp hơn so với QFP. Tuy nhiên, khi ứng suất ban đầu giữa chất nền in và bao bì không thể được giải phóng tại tiếp xúc điện cực. Bởi vì tiếp xúc điện cực này không dễ dàng như nhiều chân QFP, thường từ 14 đến 100.

Vật liệu có hai loại gốm sứ và nhựa tổng hợp phân tử. Khi được dán nhãn LCC, nó chủ yếu là gốm QFN. Khoảng cách lõi của tiếp điểm điện cực là 1,27mm. Nhựa tổng hợp phân tử QFN là một gói chất nền in thủy tinh - khí epoxy - nhựa tự nhiên chi phí thấp. Ngoài khoảng cách lõi của tiếp xúc điện cực 1,27mm, có hai loại 0,65mm và 0,5mm. Gói này còn được gọi là nhựa composite phân tử LCC, PCLC, P-LCC, v.v.

13.1 PCLP (không có gói chì cho bảng mạch in)

Bảng mạch in không có gói chì. Toyo Fujitsu Co., Ltd. coi nhựa tổng hợp phân tử QFN (Molecular Composite Plastic LCC) là tên phù hợp để sử dụng. Khoảng cách lõi pin có hai thông số kỹ thuật 0,55mm và 0,4mm. Cho đến nay, nó vẫn đang trong giai đoạn phát triển.

13.2 P-LCC (tàu sân bay chip không rách bằng nhựa) (thư viện chip chì nhựa)

Đôi khi là nhựa tổng hợp phân tử QFJ và đôi khi là QFN (Molecular Composite Plastic LCC) (xem QFJ và QFN). Các nhà sản xuất LSI địa phương sử dụng PLCC để biểu thị các gói có dây dẫn và P-LCC để biểu thị các gói không có dây dẫn để hiển thị sự khác biệt.

QFI (Quad Flat I-Leaded Packgage) 4 chân phẳng

Một trong những gói được cài đặt bên ngoài. Ghim được vẽ từ bốn mặt của gói, xuống đến chữ I. Còn được gọi là MSP (Mini Square Pack). Đặt và in cơ sở cho hàn kết hợp. Bởi vì chân không có một phần của đầu, kích thước của chân đế chiếm bề mặt phẳng hoặc vật thể nhỏ hơn QFP. Hitachi Productions đã phát triển và sử dụng gói này cho IC mô phỏng tệp video. Ngoài ra, PLL IC của Toyota Motorola cũng được coi là phù hợp để sử dụng gói này. Khoảng cách lõi pin là 1,27mm và số pin từ 18 đến 68.

15. Công nghệ TCP đóng gói màng TCP (đóng gói với tải)

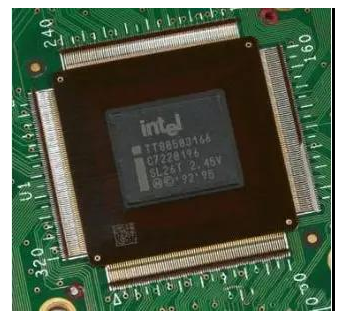

Giao thức điều khiển truyền tải

Chủ yếu được sử dụng trong "Intel Mobile Pentium MMX". CPU sử dụng gói TCP phù hợp có nhiệt ít hơn nhiều so với CPU PGA Pins Array thông thường, có thể được sử dụng trong máy tính xách tay để giảm kích thước của bộ tản nhiệt bổ sung và tăng sử dụng không gian của máy chủ, phổ biến hơn trong một số máy tính xách tay siêu nhỏ. Nhưng vì gói TCP được hàn trực tiếp CPU vào bo mạch chủ, vì người dùng trung bình không dễ dàng thay thế.

15.1 DTCP (Gói băng tải đôi)

Double Pins với Load Pack TCP (với Load Packing) Các chân được sản xuất trên băng cách nhiệt và được rút ra từ cả hai bên của gói. Gói rất mỏng do công nghệ TAB (Semi-Automatic Load Welding). Nó thường được sử dụng để điều khiển LSI thông qua phơi sáng tinh thể lỏng, nhưng hầu hết là các sản phẩm tùy chỉnh.

Ngoài ra, gói sách LSI dày 0,5mm để lưu trữ đang được phát triển. Tại Toyo, DTCP được đặt tên là DTP theo tiêu chuẩn EIAJ (Toyo Electronic Machinery Industry).

15.2 QTCP (gói bốn băng tải)

Pin bốn bên với gói tải. Một trong những gói TCP tạo chân trên băng cách nhiệt và thoát khỏi bốn mặt của gói. Là bao bì mỏng áp dụng công nghệ TAB. Ở Đông Dương, nó được gọi là QTP (Quad Tape Carrier Package).

15.3 Băng keo tự động (TAB) Công nghệ keo bán tự động

Tape Automatic Bonding (TAB) Semi-Automatic Bonding (TAB) là một chip mạch tích hợp quy mô lớn (IC) với nhiều chân kết nối, thay vì sử dụng gói truyền thống để trở thành một cá nhân hoàn chỉnh, sử dụng tàu sân bay TAB và liên kết các chip không niêm phong trực tiếp trên bề mặt bảng. Sử dụng băng "polyimide" mềm và các chân bên trong và bên ngoài được khắc bằng lá đồng làm chất mang, cho phép các chip lớn gắn vào các chân bên trong đầu tiên. Sau khi thử nghiệm bán tự động, việc lắp ráp được thực hiện bằng cách tham gia bảng với "chân bên ngoài". Một phương pháp xây dựng mới cho việc đóng gói và lắp ráp này được gọi là phương pháp TAB.

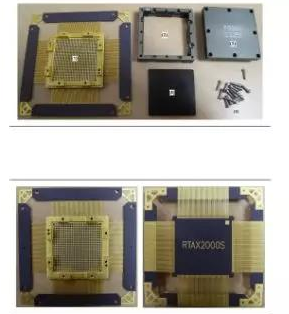

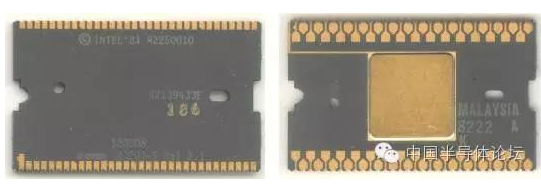

16, PGA (mảng lưới kim)

PGA

Hiển thị gói pin. Một chốt trực tiếp trên mặt dưới của nó để hiển thị một loại đóng gói hộp được sắp xếp theo mẫu. Chất nền đóng gói thường được coi là phù hợp và nhiều lớp gốm được sử dụng. Trong trường hợp tên vật liệu không được đại diện cụ thể, hầu hết là PGA gốm, được sử dụng trong các mạch LSI quy luật tư duy quy mô lớn tốc độ cao. Rất tốn kém. Khoảng cách lõi pin thường là 2,54mm, chiều dài pin khoảng 3,4mm và số lượng pin dao động từ 64 đến khoảng 447. Để giảm chi phí, chất nền in nhựa tự nhiên bằng khí epoxy thủy tinh có thể được thay thế bằng chất nền đóng gói.

PGA nhựa cũng có các hợp chất phân tử từ 64 đến 256 chân. Ngoài ra, có khoảng cách lõi pin 1,27mm, chiều dài pin ngắn từ 1,5mm đến 2,0mm Loại gắn trên bề mặt PGA (Touch-Welded PGA), nhỏ hơn một nửa so với loại chèn PGA, vì vậy các gói có thể không làm được nhiều, nhiều chân hơn loại chèn (250 đến 528).

LGA (mảng lưới đất)

LGA

Contact hiển thị các gói Đó là, làm một gói với một mảng tiếp xúc điện cực khe cắm trên mặt dưới. Chỉ cần cắm nó vào ổ cắm để lắp ráp. LGA gốm với 227 điểm tiếp xúc (khoảng cách lõi 1,27mm) và 447 điểm tiếp xúc (khoảng cách lõi 2,54mm) đã được áp dụng cho các mạch LSI quy tắc suy nghĩ tốc độ cao. LGA có thể chứa nhiều chân đầu vào và đầu ra hơn trong các gói nhỏ hơn so với QFP. Ngoài ra, dây dẫn này phù hợp với LSI tốc độ cao do trở kháng thấp của nó.

18. Gói chì trên chip

Công nghệ đóng gói LSI, một cấu trúc đặt phần trước của khung chì phía trên chip, tạo ra các mối hàn lồi gần lõi chip và khâu các dây dẫn để đồng lập trình điện. So với cấu trúc ban đầu, nơi khung dẫn được đặt gần mặt bên của chip, chiều rộng của chip có thể là khoảng 1mm trong cùng một gói.

19. Kiểm tra.

Quad In Line là một gói nội tuyến bốn chân được gọi là Quill. Các chân được rút ra từ cả hai bên của gói và uốn cong xuống thành bốn hàng trong khoảng thời gian chéo. Khoảng cách lõi pin là 1,27mm, khoảng cách lõi thay đổi thành 2,5mm khi chèn chất nền in. Bởi vì điều này áp dụng cho bảng mạch in tiêu chuẩn. Nó là một gói nhỏ hơn so với DIP tiêu chuẩn. Công ty Toyo Electric đã sử dụng một số gói thích hợp trong chip logo cho các sản phẩm máy tính để bàn và thiết bị gia dụng của mình. Vật liệu có hai loại gốm sứ và nhựa tổng hợp phân tử. Số pin 64

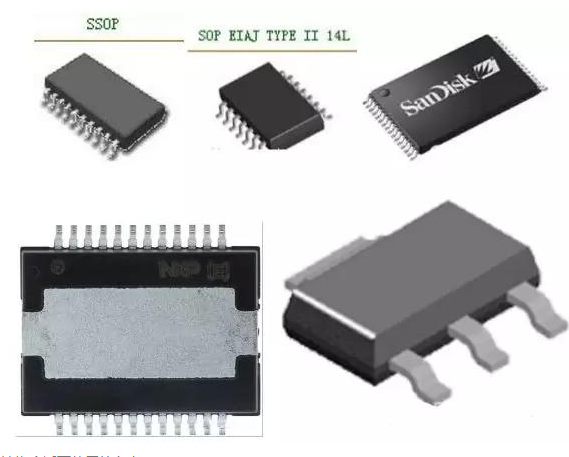

20. SOP (Gói bên ngoài nhỏ)

Gói nhỏ. Là một gói gắn bên ngoài, các chân được kéo ra từ cả hai bên của gói và có hình dạng cánh mòng biển (hình chữ L). Vật liệu có hai loại nhựa tổng hợp phân tử và gốm sứ. Còn được gọi là SOL (Small Out L Leader Pack), DFP (Dual Plane Pack), SOIC (Small Out Integrated Circuit), DSO (Dual Small) Leader, nhiều nhà sản xuất chất bán dẫn nước ngoài sử dụng tên này khi thấy phù hợp.

SOP không chỉ được sử dụng trong bộ nhớ LSI mà còn được sử dụng rộng rãi trong các mạch ASSP nhỏ. SOP là gói gắn trên bề mặt phổ biến nhất trong các lĩnh vực có thiết bị đầu cuối đầu vào và đầu ra không vượt quá 10 đến 40. Khoảng cách lõi pin là 1,27mm và số pin từ 8 đến 44.

Khi SOP tiến triển, nó được phân phối dần dần:

SSOP với khoảng cách lõi nhỏ hơn 1,27mm (SOP từ lớn đến nhỏ);

Chiều cao lắp ráp nhỏ hơn 1,27mm TSOP (gói nhỏ mỏng);

VSOP (Gói siêu nhỏ); TSSOP(Thin from Large to Small SOP);

SOT (Small Knot Transistor – bóng bán dẫn kết nối nhỏ); SOP với bộ tản nhiệt được gọi là HSOP;

Các nhà sản xuất chất bán dẫn địa phương gọi SOP là SONF (Small Non-tản nhiệt tản nhiệt);

Các nhà sản xuất địa phương gọi SOP thân rộng (loại J rộng) SOW

21. Gói phẳng nhỏ MFP (Mini Flat Pack)

SOP nhựa tổng hợp phân tử hoặc bí danh SSOP. Một cái tên mà các nhà sản xuất chất bán dẫn địa phương cho là phù hợp.

22, SIMM (Mô-đun bộ nhớ đơn hàng)

Một thành phần lưu trữ một dòng. Các thành phần lưu trữ được trang bị với các điện cực chỉ gần một bên của bề mặt in. Nó thường đề cập đến các thành phần được cắm vào ổ cắm. SIMM tiêu chuẩn có một điện cực 30 với khoảng cách lõi 2,54mm, 72 điện cực và khoảng cách lõi 1,27mm. Với DRAM 1 và 4 megabyte, SIMM được đóng gói bằng SOJ ở một hoặc cả hai bên của chất nền in, nó đã được sử dụng rộng rãi trong máy tính cá nhân, trạm văn phòng và các cơ sở khác. Ít nhất 30 đến 40% DRAM được lắp ráp trong SIMM.

23, DIMM (Mô-đun bộ nhớ trực tiếp hai hàng)

Nó rất giống với SIMM, ngoại trừ hai đầu ngón tay vàng của DIMM không giao tiếp với nhau như SIMM. Thay vào đó, các đầu ngón tay vàng của DIMM giao tiếp độc lập với nhau vì điều này có thể đáp ứng nhu cầu truyền tải của một số lượng lớn tín hiệu dữ liệu. Cũng được coi là phù hợp và sử dụng DIMM, giao diện SDRAM và giao diện bộ nhớ DDR hơi khác nhau, SDRAM DIMM là cấu trúc DIMM 168PIN, ngón tay vàng mỗi bên là 84PIN, ngón tay vàng có hai thẻ để ngăn chặn chèn khe cắm, bộ nhớ không được chèn đúng hướng ngược lại và gây ra sự phá hủy ghi; DDR DIMM cho rằng việc sử dụng cấu trúc DIMM 184PIN là thích hợp, ngón tay vàng có 92PIN ở mỗi bên và đầu ngón tay vàng chỉ có một khe cắm. Số lượng lưỡi lê không giống nhau, là sự khác biệt hời hợt nhất giữa hai người.

DIMM DDR2 có cấu trúc DIMM 240PIN và ngón tay vàng có 120PIN ở mỗi bên. Giống như DDR DIMM, Goldfinger chỉ có một thẻ trên đầu, nhưng vị trí của thẻ hơi khác so với DDR DIMM vì bộ nhớ DDR không thể cắm vào DDR2 DIMM. Bộ nhớ DDR2 không thể được chèn vào DDR DIMM vì bo mạch chủ có cả DIMM DDR và DIMM DDR2 sẽ không hiển thị vấn đề với việc chèn sai khe cắm bộ nhớ.

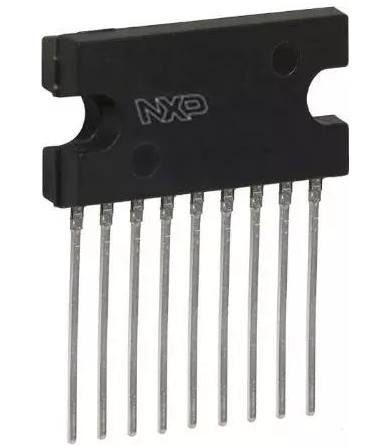

24, SIP (gói dây đơn)

Một gói nội tuyến duy nhất. Hầu hết các nhà sản xuất chất bán dẫn châu Âu sử dụng tên SIL (dây đơn) khi họ thấy phù hợp. Các chân được vẽ và sắp xếp theo một đường thẳng từ một bên của gói. Khi lắp ráp trên một chất nền in, gói ở vị trí bên. Khoảng cách lõi pin thường là 2,54mm, số lượng pin khác nhau từ 2 đến 23, hầu hết là sản phẩm tùy chỉnh. Phong cách đóng gói khác nhau. Một số cũng gọi kiểu tương tự như gói ZIP là SIP.

25. SMD (Thiết bị gắn trên bề mặt)

Chip SMD

Xuất hiện lắp đặt các bộ phận. Thỉnh thoảng, một số nhà sản xuất chất bán dẫn phân loại SOP là SMD.

26. SOI (gói dây dẫn loại I nhỏ)

Tôi đóng gói nhỏ. Một trong những gói được cài đặt bên ngoài. Các chân được rút ra từ cả hai bên của gói và có hình chữ I hướng xuống với khoảng cách lõi 1,27mm. Giá đỡ chiếm bề mặt phẳng hoặc bề mặt của một đối tượng nhỏ hơn SOP. Hitachi đã sử dụng gói này trong IC nhái (IC ăn cắp động cơ). Số pin 26

27. SOJ (gói dây dẫn J nhỏ)

J-Needle gói nhỏ. Một trong những gói được cài đặt bên ngoài. Các chân có hình chữ J từ hai bên của gói, do đó có tên. Nó thường được làm bằng nhựa phân tử và chủ yếu được sử dụng trong các mạch LSI bộ nhớ như DRAM và SRAM, nhưng chủ yếu là DRAM. Nhiều thành phần DRAM được đóng gói trong SOJ được lắp ráp trên SIMM. Khoảng cách giữa các lõi pin là 1,27mm và số lượng pin từ 20 đến 40 (xem SIMM).

28, Đóng gói

To PackageTo

Khung gầm của nó là một tấm kim loại tròn, sau đó đặt một miếng thủy tinh nhỏ để sưởi ấm, sau khi thủy tinh tan chảy sẽ cố định dây dẫn trong lỗ, lỗ và dây dẫn được gọi là sự kết hợp của ghế đầu, vì vậy đầu tiên trên ghế đầu được mạ vàng, bởi vì đáy của bảng mạch tích hợp được mạ vàng, vì vậy nó có thể được hàn bằng vàng, germanium hàn sáp; Khi hàn, ghế đầu được làm nóng trước để sáp hàn được đặt ở đó tan chảy hoàn toàn, sau đó các tấm được đặt trên sáp hàn, và cả hai tạo thành một sự kết hợp tốt sau khi làm mát.