Các thiết kế của tín hiệu chứng chìm trên tàu Bảng PCB không chỉ là một tín hiệu khác nhau, nhưng cũng là tín hiệu điện tử cao tốc. Do đó, cho dù trường hợp truyền tín hiệu đó có dùng trung gian Bảng PCB dây hay dây cáp, Cần phải có biện pháp để ngăn không cho tín hiệu phản chiếu tại nhà ga truyền thông., và nhiễu điện từ nên bị giảm để đảm bảo tín hiệu to àn vẹn. Miễn là chúng ta xem xét các yếu tố này khi lắp dây điện., thiết kế mạch khác tốc độ cao không khó lắm đâu.. The following thiết thiết the thiết kế point the LVD's signs on the Bảng PCB:.L Việc bố trí vào một bảng mạch trải nhiều lớp với tín hiệu của thẻ lớn được đặt ra như một tấm nền đa lớp. Vì biệt máy nghe hiện ở trung tâm pháp, Lớp bên cạnh phải là lớp đất để bảo vệ tín hiệu của chứng chìm để tránh nhiễu. Cho ván với mật độ thấp, nếu điều kiện không gian vật lý cho phép, đặt tín hiệu của chứng chìm ở nhiều lớp khác nhau. Ví dụ như, trong một tấm ván bốn lớp, Các lớp có thể được mô tả như sau:, Lớp đất, Lớp năng lượng, và các lớp phát tín hiệu. Name.Kiểm toán và điều khiển trực thăng. Bộ treo điện thế của tín hiệu LVD chỉ là Comment50mV, dùng để chạy tín hiệu cấp khác chạy hiện thời.. Để đảm bảo tín hiệu không bị ảnh hưởng bởi tín hiệu phản chiếu khi nó lây lan trên đường truyền, phải điều khiển trở ngại của đường truyền., và trở ngại khác biệt thường L00++/-L0 Name069;. Tính chất của việc kiểm soát trở ngại ảnh hưởng trực tiếp đến tín hiệu.

L. Cách kiểm soát nó Bảng PCB trở?

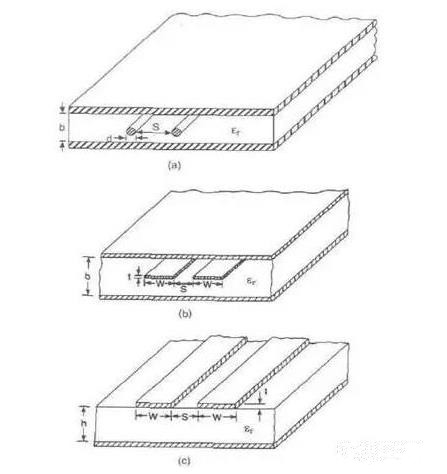

L.1 Chọn chế độ dây dẫn, tham số và tính cản trở. Phòng phát triển chứng khoán ở chế độ phân biệt đường ống vi dải cấp phía ngoài và chế độ phân biệt đường ống trong lớp. Làm giả có thể tính toán bằng cách đặt các tham số một cách hợp lý và dùng phần mềm tương ứng. Qua tính toán, Cấp cản trực tiếp tỷ lệ với độ dày của lớp cách ly, và đảo ngược tỉ lệ với hằng số điện tử, độ dày và độ rộng của sợi dây.

1.Name Làm theo nguyên tắc đường vòng và móc nối chặt. Sau khi xác định độ rộng và khoảng cách đường, tuân theo chiều ngang và khoảng cách được tính toán khi lộ trình, và khoảng cách giữa hai đường luôn phải được giữ không đổi, đó là, they must be parallel (you can place the picture). Cùng một lúc, Nguyên tắc móc nối chặt được quan sát khi tính bề ngang và khoảng cách đường., đó là, Khoảng cách đường của hai bộ phân biệt thấp hơn hoặc bằng chiều ngang của đường.. Khi hai đường dây báo hiệu chẩn rất gần nhau., Hướng truyền hiện thời ngược lại., Từ trường liền hủy bỏ lẫn nhau., các trường điện kết hợp với nhau, và bức xạ điện từ rất nhỏ. Cũng, hai sợi dây phải ở cùng một lớp để tránh dây dẫn rải nhựa. Bởi vì trong quá trình thực sự của Bảng PCB, Độ mỏng manh giữa các cọc thấp hơn độ chính xác khắc của cùng lớp, và sự mất mát cấp độ trong quá trình sản mỏng không thể đảm bảo khoảng cách giữa các đường khác ngang với độ dày của máy thở cấp ngoài, sẽ gây nên khó khăn khác nhau thay đổi hai lớp khác nhau.

1.♪ Đi ngắn và thẳng ♪. Để đảm bảo chất lượng tín hiệu, thẻ hàm phân biệt của hai cặp phải ngắn và ngắn nhất có thể., giảm số cầu dao trong đường dây., và tránh dây tế bào khác nhau quá dài và quá nhiều lần quay. Hãy thử sử dụng 45194; 176; hay arcs ở các góc. Tránh đường 954Name;176; Quay. Không có hạn chế nào cho việc chọn các phương pháp dẫn đường cặp cặp hai thẻ chứng run rẩy giữa các cặp khác nhau.. Có thể dùng đường dây vi dải, nhưng phải lưu ý là có một cái máy bay tham chiếu tốt.. Khoảng cách giữa các đường khác nhau không nên quá nhỏ., và phải có ít nhất 3-5 hơn khoảng cách giữa các đường phân biệt. Nếu cần thiết, làm thêm lỗ đất cách biệt giữa các cặp khác nhau để tránh giao nhau. Giữ cho thẻ mất tín hiệu tránh xa các tín hiệu khác nhiều nhất có thể.. Không thể phân chia tín hiệu cấp độ cho máy bay. Mặc dù hai tín hiệu khác nhau là đường quay lại., Các phân đoạn chéo sẽ không ngắt tín hiệu trở về., but the transmission line across the segmentation will cause discontinuity in impedance due to the lack of a reference plane (as shown in the figure, where GND1 and GNDName are adjacent to LVDS Ground plane). Khoảng cách giữa độ kháng cự khớp của đầu nhận và cái chốt nhận phải càng gần càng tốt.. Cùng một lúc, Độ chính xác của độ kháng cự khớp phải được kiểm soát. Cho địa hình điểm đến điểm, Độ cản trở của dấu vết thường được điều khiển ở 100\ Name0699;, nhưng độ kháng cự khớp có thể điều chỉnh theo tình trạng hiện tại. Độ kháng cự là 1-Name%. Bởi vì theo kinh nghiệm, Không phù hợp gây cản trở sẽ tạo ra lợi nhuận cao hơn.

Name. Simulation analysis of serial LVDS signal

The above analyzes the matters that must be paid attention to when designing LVDS signals. Mặc dù các quy tắc trên vẫn thường được tuân theo trong suốt kế hoạch PCB, để nâng cao độ chính xác và độ chính xác của thiết kế, Việc mô phỏng toàn bộ tín hiệu PCB phải được thực hiện qua mô phỏng.. Bắt được liên lạc, chậm, Phản xạ và hình thái rung mắt, để đạt được mục đích thiết kế đúng đắn. Mô phỏng vấn đề độ chính của tín hiệu là trước tiên thiết lập mô hình mô phỏng các thành phần, và sau đó thực hiện mô phỏng trước để xác định các tham số và giới hạn của quá trình truyền dẫn.. Các bước phát triển vật lý được thiết kế theo những hạn chế, và sau khi mô phỏng được thực hiện để xác minh thiết kế có đáp ứng yêu cầu thiết kế không.. Tính chất của mô hình trong toàn bộ quá trình ảnh hưởng trực tiếp đến kết quả của mô phỏng., và các phương pháp phân tích mô phỏng sử dụng trong giai đoạn trước và sau mô phỏng cũng rất quan trọng với kết quả mô phỏng., và một độ cao của mô hình gia vị được dùng trong thiết kế này. Những dự án này được tổ hợp để minh họa tiến trình mô phỏng trong thiết kế này..

2.1 Bảng PCB stack setting

From the above analysis, It is known that the Stacking settle of the Bảng PCB có mối liên hệ chặt chẽ với việc kết nối tín hiệu và tính cản trở. Do đó, chất liệu xếp phải được thực hiện trước khi Bảng PCB design, và sau đó tính cản trở của tín hiệu.

2.2 Set DC voltage value

This step is mainly to specify the DC voltage value for certain specific networks (usually power ground, Comment.), xác định điện tử DC cần áp dụng cho mạng lưới, và thực hiện mô phỏng EME đòi hỏi phải xác định một hoặc nhiều ghim nguồn điện.. Những giá trị điện thế này bao gồm thông tin điện ảnh tham chiếu của mô hình trong quá trình mô phỏng được mô phỏng..

2.3 Device settings

During allegro simulation, Allegro phân chia các thiết bị thành ba hạng:, connectors and discrete devices (resistance capacitors, Comment.), Allegro sẽ phân phối các thuộc tính mô phỏng của thiết bị theo kiểu thiết bị, những thiết bị riêng và chốt đoạn dẫn, và thuộc tính pin của IC có thể ở IN, Comment, Comment, Comment.

2.4 Model allocation

The main models used in the board-level high-speed Bảng PCB Quá trình mô phỏng là mô hình thiết bị và mô hình đường truyền. Thiết bị mẫu thường được cung cấp bởi người sản xuất thiết bị. Trong tín hiệu hàng loạt tốc độ cao, Những gì chúng tôi chọn là mô hình SPICE với độ chính xác cao hơn để tiến hành phân tích mô phỏng.. Mô hình đường truyền được hình thành qua mô hình phần mềm mô phỏng. Khi tín hiệu được truyền đi, Đường truyền sẽ gây chú ý vấn đề về tín hiệu., Do đó khả năng mô phỏng phần mềm mô hình đường truyền ảnh hưởng trực tiếp đến kết quả mô phỏng..

2.5 SI inspection

The SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. Thường, Đó là thiết lập mạng lưới tốc độ cao chúng ta cần phải chú ý. Thiết kế này chủ yếu tập trung vào tín hiệu liên tiếp..

2.6 Extract network topology

Extract the topological structure of the signal of interest from the Bảng PCB, Thường bao gồm cả cuối cùng và cuối cùng nhận., cũng như đường truyền và các đối tượng khớp với nhau và tụ điện. Có thể nhìn thấy từ địa hình rằng mạng lưới đi qua các đường mòn đó., sẽ gây ra sự truyền tín hiệu. This article only takes the network topology diagram of one of the signals as an example: as shown in Figure 4:

2.7 View waveform

After the above related steps are set up, Mô phỏng có thể được thực hiện. Allegro có thể thực hiện mô phỏng phản xạ tín hiệu và giả lập chat, và tuyến khác nhau cũng cần phải thực hiện phân tích sơ đồ mắt. Tất nhiên rồi, The simulation is also computed into pre-simulation and postsimulation. Khi dùng Allegro để thiết kế... Bảng PCB, cần phải thay đổi thiết kế theo thời gian thực với kết quả mô phỏng để đáp ứng yêu cầu. Bởi vì quá trình mô phỏng phức tạp và các bước chân cồng kềnh., Tôi sẽ không miêu tả từng người một.. Có hai điểm cần chú ý trong việc lắp ráp các cặp khác nhau.. Một là độ dài của hai dòng dài càng lâu càng tốt., và độ dài ngang nhau là đảm bảo hai tín hiệu khác nhau được giữ đối diện mọi lúc.. Địa điểm để giảm thành phần chế độ phổ biến. The other is that the distance between the two lines (this distance is determined by the differential impedance) must always be kept constant, đó là, nó phải được song song song. Có hai cách song song, một là hai sợi dây chạy cùng một cạnh nhau., and the other is that the two wires run on two adjacent layers above and below (over-under). Thường, Đầu tiên có nhiều dụng cụ nội bộ hơn. Tỷ lệ đòi hỏi chủ yếu là gây cản trở phân biệt nhau giữa hai người và giảm suy nghĩ. Cái phương pháp dây tế nhị của cặp khác phải cận kề và song trùng một cách thích hợp.. Cái gọi là khoảng cách thích hợp là bởi vì khoảng cách này sẽ ảnh hưởng đến giá trị Trở ngại khác nhau, một tham số quan trọng để thiết kế các cặp khác nhau. Cần phải có sự đồng loạt cũng phải duy trì sự đồng nhất của cản trở khác biệt.. Nếu hai dòng đột ngột ở rất xa và gần, Sự cản trở phân biệt sẽ bất ổn, sẽ ảnh hưởng tới độ chính xác tín hiệu và thời gian trễ. Từ đồ thị Tham số S mô phỏng, Khả năng cản khác nhau của hai bộ phận khác nhau và tính trung thực tín hiệu có thể phân tích. Những dạng rung động mô phỏng tín hiệu chìa khóa trong thiết kế này được cung cấp dưới để giải thích.. Có thể nhìn thấy từ chương trình mô phỏng hình hình E.5 rằng chỉ mục phân hủy S11 trong vùng tần số 0-3.0GHz là: phía dưới-16.770ddddddGenericName, and S22 (pink curve) is not worse than -17db. Cái này cho thấy Trở ngại khác nhau của hai bộ phận khác nhau gần với chỉ mục thiết kế, và tín hiệu chỉ toàn vẹn.

3. Conclusion

Through the above simulation analysis, có thể biết rằng các yêu cầu khác nhau cho các tín hiệu biến tốc độ cao của đế chế biến đó có thể được đáp ứng trong giai đoạn thiết kế của... Bảng PCB, và thực tế Bảng PCB sản xuất cũng đã chứng minh sự đúng đắn của thiết kế.. Sản phẩm hoạt động ổn định và hoàn hảo với PCI- Express yêu cầu phải vận chuyển dữ liệu tốc cao và đáng tin cậy. Từ phân tích trong bài báo này, có thể thấy rằng trong thiết kế của tín hiệu tần suất cao, không chỉ thiết kế mạch được xem xét, Tính thiết kế sơ đồ và phân tích mô phỏng cũng rất quan trọng., và khi tần số của tín hiệu trở nên lớn hơn và lớn hơn, Tín hiệu chậm trễ và liên tục bị ảnh hưởng. Các yếu tố như tính toàn vẹn tín hiệu và tín hiệu trở nên phức tạp hơn.. Cùng một lúc, Càng ngày càng khó kiểm soát sức ảnh hưởng của những yếu tố này. Các kỹ sư phải phân tích dây dẫn kỹ lưỡng., mẫu dùng, Cách mô phỏng và phân tích khoa học hiệu quả, in order to provide the correct guidance for the complex high-speed Bảng PCB design and reduce the correction cycle to ensure The design is successful.