L. EMTôi generation and Languageuppression principle

EMI in in bảng mạch thiết kế được tạo ra bởi các nguồn nhiễu điện từ chuyên truyền năng lượng vào các hệ thống nhạy cảm qua đường nối. Nó bao gồm ba hình dạng cơ bản: dẫn truyền qua dây hay chỗ bằng lòng đất., phóng xạ qua không gian, hay nối qua cận trường. Tai họa của EME được biểu hiện là giảm chất lượng tín hiệu phát tín hiệu., gây nhiễu hay thậm chí gây tổn hại đến hệ thống hay thiết bị, để thiết bị này không thể đáp ứng yêu cầu chỉ số kỹ thuật được xác định trong tiêu chuẩn đối chọi điện từ..

Để áp giải EMS, the Thiết kế EMS of digital circuits should be carried out according to the following principles:

L.L Dựa theo EMC liên quan/Hệ thống hoá đơn, Các chỉ số được phân hủy thành mạch đơn ván để kiểm soát hệ thống..

1.Kiểm soát từ ba yếu tố của EME, Chính:, nguồn nhiễu, đường nối năng lượng và hệ thống nhạy cảm, để cho hệ thống có một phản ứng tần số bằng phẳng và đảm bảo rằng mạch hoạt động bình thường và ổn định..

1.Khởi đầu với thiết kế đầu của thiết bị, chú ý EMC/EMI design, và giảm chi phí thiết kế.

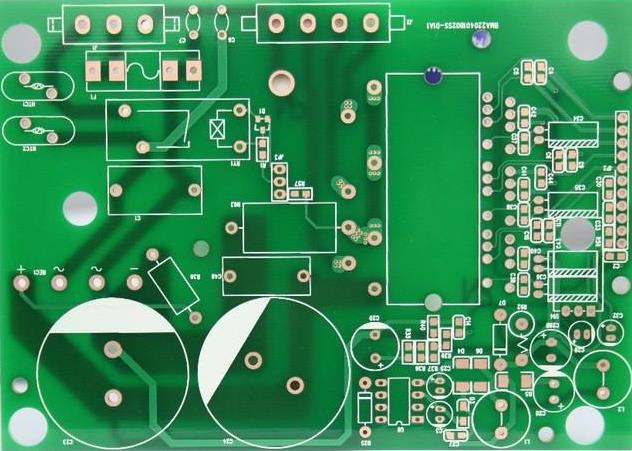

Name. Hệ thống điều khiển Tai Ương Bảng PCB

Khi xử lý các dạng khác nhau của EME., vấn đề cụ thể phải được phân tích. Vào trong Bảng PCB thiết kế mạch điện tử, Kiểm soát EME có thể được thực hiện từ những khía cạnh sau:.

Name.1 Device Selection

Trong thiết kế EMS, Điều đầu tiên cần xem xét là tốc độ của thiết bị đã chọn. Hệ thống nào thay thế thiết bị bằng thời gian bay lên của 5n với thiết bị với thời gian bay cao của Name.Lực lượng 5n sẽ tăng cao EME bằng một tính năng khoảng 4.. Phát tán độ mạnh của EME phụ thuộc vào khoảng vuông của tần số., cũng được biết đến như băng tần truyền của EME., mà là chức năng của thời gian phát tín hiệu thay vì tần số tín hiệu: fknee =0.Comment5/Tr (where Tr is the signal rise time of the device). The tần số range of this type of radiated EME is Comment0MHz to several GHz, và trong tần số này, Các bước sóng quá ngắn đến nỗi những dây điện rất ngắn trên bảng mạch có thể trở thành một ăng-ten truyền tín hiệu.. Khi EME cao., mạch có xu hướng mất chức năng bình thường.. Do đó, để chọn thiết bị, dựa trên việc đảm bảo các yêu cầu hiệu suất mạch, Tốc độ thấp phải được sử dụng càng nhiều càng tốt., và lái xe thích hợp/nên sử dụng vòng tiếp nhận. Thêm nữa., Bởi vì các chốt chì của thiết bị có chứa năng lượng ký sinh và tụ điện ký sinh., trong thiết kế tốc độ cao, Không thể bỏ qua ảnh hưởng của mẫu vật đóng gói thiết bị lên tín hiệu., bởi vì nó cũng là một yếu tố quan trọng để tạo ra bức xạ EMS.. Nói chung, Các tham số ký sinh của thiết bị SMD nhỏ hơn so với các thiết bị bổ sung., và các tham số ký sinh của các gói BGA nhỏ hơn so với các gói QFF.

Name.Name Connector selection and signal terminal definition

Connector is the key link of high-speed signal transmission, và đó cũng là mối liên kết yếu đuối có xu hướng với EME.. In the terminal design of the connection, nhiều chốt đất có thể sắp xếp để giảm khoảng cách giữa tín hiệu và mặt đất, giảm vùng ngắt tín hiệu hiệu hiệu hiệu hiệu có thể tạo ra phóng xạ trong phần kết nối, cung cấp một đường trở về khó quay. Nếu cần thiết, xem xét việc cô lập các tín hiệu chìa khóa bằng các chốt.

Name.Comment Laminate Design

If the cost permits, tăng số lớp đất và đặt lớp phát tín hiệu cạnh lớp dưới mặt đất có thể giảm bức xạ EMS.. Cho tốc độ cao Bảng PCBs, năng lượng và máy bay mặt đất được kết hợp ở rất gần để cản trở nguồn cung điện., giảm EME..

Name.4 Layout

According to the signal current flow, một thiết kế hợp lý có thể giảm nhiễu giữa tín hiệu. Thiết kế thích hợp là chìa khóa để kiểm soát EME.. The basic principles of layout are:

(1) The analog signal is easily interfered by the digital signal, and the analog circuit should be separated from the digital circuit;

(2) The clock line is the main source of interference and radiation, so keep it away from sensitive circuits and keep the clock line short;

(Comment) Circuits with high current and high power consumption should be avoided as far as possible in the central area of the board, and the influence of heat dissipation and radiation should be considered at the same time;

(4) The connectors should be arranged on one side of the board as far as possible and away from high-frequency circuits;

(5) The input/kết xuất hiện gần với kết nối tương ứng, and the decoupling capacitor is close to the corresponding nguồn điện pin;

(6) Fully consider the feasibility of layout for power splitting, and multi-power devices should be placed across the boundary of sức mạnh splitting area to effectively reduce the impact of plane splitting on EMI;

(7) The reflow plane (path) is not divided.

2.5 Wiring

(1) Impedance control: High-speed signal lines will exhibit the characteristics of transmission lines, và để tránh phản xạ tín hiệu, quá tải và chuông, giảm bức xạ EMS.

(2) Classify the signals, according to the EMI radiation intensity and sensitivity of different signals (analog signal, đồng hồ, I/O tín hiệu, xe buýt, power supply, Comment.), tách nguồn nhiễu khỏi hệ thống nhạy cảm càng nhiều càng tốt để giảm khớp nối.

(Comment) Strictly control the trace length, Số cây cầu, Canh lề, kết thúc, nhiều lớp nối, đường dẫn đường, Comment. of clock signals (especially high-speed clock signals).

(4) The signal loop, đó là, vòng thời gian được hình thành bởi tín hiệu chảy ra tới tín hiệu trong, là chìa khóa để kiểm soát EME trong thiết kế PCB và phải được điều khiển trong suốt đường dây dẫn.. Để hiểu được hướng chảy của mỗi tín hiệu chìa khóa, chuyển tín hiệu chính gần đường trở về để đảm bảo vùng vòng của nó.. Cho tín hiệu tần số thấp, làm dòng chảy hiện tại chảy qua đường của đối tượng; cho tín hiệu tần số, làm cho dòng chảy tần số cao chảy qua đường dẫn của bộ não, không phải đường đi của đối tượng. Cho chế độ phân biệt, the EMI radiation intensity (E) is proportional to the current, vùng của vòng thời gian hiện thời, và hình vuông của tần số. (where I is the current, A là khu vực vòng thời gian, f là tần số, r là khoảng cách tới trung tâm của vòng thời gian, và k là một hằng số.) So when the inductor return path is just below the signal conductor, có thể giảm vùng vòng thời gian hiện thời, Do đó, giảm năng lượng của EME.. Những tín hiệu quan trọng không được xâm nhập khu vực. Dấu vết tín hiệu cấp thấp với tốc độ cao phải kết hợp càng chặt càng tốt.. Đảm bảo nguyên tắc, Đường ống, và máy bay tham chiếu của chúng đáp ứng yêu cầu. Dây dẫn dẫn của các tụ điện tách ra phải ngắn và rộng. Tất cả dấu vết tín hiệu nên được giữ càng xa càng tốt.. Cho mạng kết nối đa điểm, chọn địa hình thích hợp để giảm sự phản xạ tín hiệu và giảm thải của EME..

2.6 Split Processing of Power Plane

(1) Division of the power supply layer

When there are one or more sub-power supplies on a main power supply plane, đảm bảo sự duy trì của mỗi vùng cung cấp năng lượng và độ rộng của sợi đồng. Bộ phân chia không cần phải quá rộng., Thông thường một đường rộng 950 Milo là đủ để giảm bức xạ lỗ hổng.

(2) Division of the ground layer

The ground plane layer should remain intact to avoid fragmentation. Nếu nó phải được chia ra, phân biệt mặt đất số, Mặt đất tương tự và vùng đất nhiễu, và kết nối nó với mặt đất bên ngoài thông qua một điểm đất chung tại lối ra.. Để giảm bức xạ gai của nguồn cung điện, the power/Máy bay mặt đất nên làm theo nguyên tắc kế hoạch 20H., đó là, the size of the ground plane is 20H larger than the size of the power plane, để độ mạnh phóng xạ của trường dòng có thể giảm xuống bằng bộ 70%.

Comment. Other control methods for EMI

3.1 Power System Design

(1) Design a low impedance power system to ensure that the impedance of the power distribution system in the frequency range below fknee is lower than the target impedance.

(2) Use a filter to control conducted interference.

(3) Power supply decoupling. In EMI design, cung cấp các tụ điện tách ra hợp lý có thể làm con chip hoạt động chắc chắn, và giảm nhiễu tần số cao trong nguồn cung điện, giảm EMS. Do tác động của phép màu dây và các tham số ký sinh khác, nguồn điện và dây cung cấp của nó quá chậm., có thể làm cho dòng điện tức thời yêu cầu của người điều khiển trong mạch tốc độ cao không đủ. Đáng lẽ thiết kế tụ điện cắt ngang hay tách ra và phân phối khả năng cung cấp điện có thể nhanh chóng cung cấp năng lượng cho thiết bị bằng cách vận dụng hiệu ứng dự trữ năng lượng của tụ điện trước khi nguồn điện phản ứng lại.. Một sự tách rời có tụ điện cung cấp một đường dẫn năng lượng thấp, mà là chìa khóa để giảm chế độ phổ biến EME..

3.2 Grounding

Grounding design is the key to reducing the EMI of the whole board.

(1) Make sure to use single-point grounding, nhiều điểm lắp ráp.

(2) Separate digital ground, Mặt đất và tiếng ồn, và xác định một điểm chung thích hợp.

(3) If there is no ground wire layer in the double-sided design, rất quan trọng để thiết kế lưới dây mặt đất một cách hợp lý, và độ rộng của sợi dây mặt đất, Độ rộng của dây điện, và độ rộng của dây tín hiệu phải được bảo đảm. Có thể dùng phương pháp lát đường lớn, nhưng phải lưu ý là sự duy trì của khu vực rộng nằm trên cùng lớp tốt hơn.

(4) For the multi-layer board design, đảm bảo rằng có một lớp dưới mặt đất để giảm cản trở mặt đất.

3.3 Damping resistor in series

Under the premise that the circuit timing requirements allow, cơ bản công nghệ triệt tiêu nguồn nhiễu là chèn một giá trị kháng cự nhỏ hàng loạt vào cuối nguồn ra tín hiệu chủ yếu., thường là một 22-33 206; 1699; kháng cự. Chuỗi kết nối các cự phụ nhỏ tại các thiết bị kết xuất có thể làm chậm độ cao./Giảm tốc độ và giảm tốc độ bắn quá đà và bắn hạ., giảm độ lớn điều hoà tần suất cao của dạng sóng xuất và triệt tiêu căn cứ EME..

3.4 Shield

(1) Key devices can use EMI shielding material or shielding mesh.

(2) The shielding of key signals can be designed as strip lines or isolated by ground wires on both sides of key signals.

3.5 Spread Spectrum

Spread spectrum (spread spectrum) method is a new effective method to reduce EMI. Dàn rộng là điều chỉnh tín hiệu để mở rộng năng lượng tín hiệu thành một dải tần số tương đối rộng.. Trên thực tế, Phương pháp này là một sự thay đổi được điều khiển của tín hiệu đồng hồ., mà không làm tăng rung động tín hiệu đồng hồ đáng kể. Ứng dụng thực tế đã chứng minh các kỹ thuật phổ rộng có hiệu quả., giảm thải từ 7 đến 20 dB.

3.6 EMI Analysis and Testing

(1) Simulation analysis. Sau khi Bảng PCB nối xong, Hệ thống và phần mềm mô phỏng EMS có thể được dùng để phân tích mô phỏng mô phỏng EMC./Môi trường EME để đánh giá liệu sản phẩm này có đáp ứng yêu cầu của các tiêu chuẩn liên quan về sự hoà hợp điện từ..

(2) Scanning test, sử dụng một máy quét phóng xạ điện từ để quét đĩa máy sau khi lắp ghép được kết nối và nạp điện..

4. Summary

With the continuous development and application of new high-speed chips, Tần số tín hiệu ngày càng cao hơn., và những chiếc yếm chở chúng có thể ngày càng nhỏ hơn. Bảng PCB thiết kế sẽ đối mặt với các thử thách lớn của EME.. Chỉ có khai thác và phát triển liên tục mới có thể EMC./Hệ thống EME in bảng mạch thành công.