Chất lượng của lớp bốn Bảng mạch PCB đã được xác định trong IPC. Quá trình bề mặt là thuốc kháng hóa. Nếu túi chân không được mở, nó sẽ được dùng trong vòng nửa năm, và túi chân không sẽ được tháo ra trong vòng một ngày., và nhiệt độ và độ ẩm được kiểm soát. Trong môi trường nơi tấm bảng không được dỡ ra, nó sẽ được dùng trong vòng một năm.. Sau khi nó được mở, nó phải được dán trong vòng một tuần và vài giờ.. Nhiệt độ và độ ẩm cũng phải được kiểm soát. Tấm bảng vàng tương đương với tấm bảng thiếc, nhưng quá trình điều khiển còn khắc nghiệt hơn cả cái bảng.

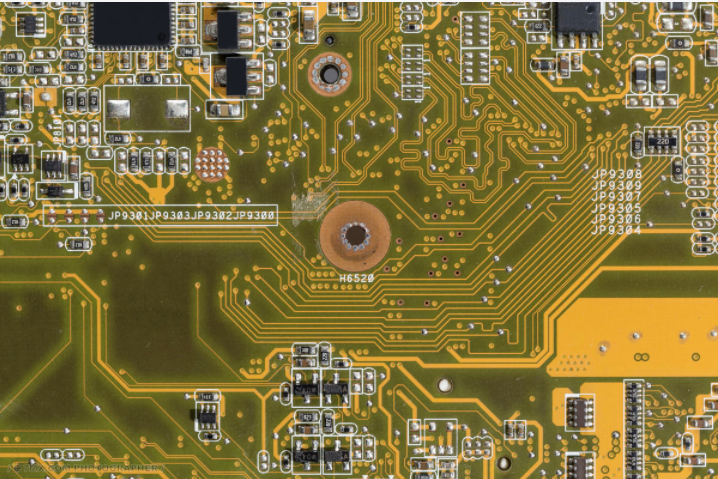

Nói chung, một bảng mạch bốn lớp có thể được chia thành một lớp trên, một lớp dưới và hai lớp giữa. Lớp trên và phía dưới được định tuyến với các đường dây tín hiệu. Lớp giữa đầu tiên sử dụng lệnh DESIN/LAYER STACK Manager để thêm chất LANGLEY và LANGLEY với ADD PLANESE là loại cấp điện lớn nhất của PCB như VC và tầng đất như GND (tức là kết nối các nhãn mạng tương ứng. Cẩn thận không sử dụng ADD LAYER, nó sẽ tăng khả năng dịch vụ MIMPLALER, thường được dùng cho vị trí tín hiệu PCB nhiều lớp) Vậy là PLNNE1 và PLANE2 là hai lớp đồng nối với nguồn cung cấp điện VC và GND mặt đất.

TPCB bốn lớp là: PCB in Bảng mạch làm bằng bốn lớp vải thủy tinh. Thường, SDRAM dùng bảng lớp 4. Tuy nhiên nó sẽ làm tăng giá của nó, nó có thể tránh nhiễu.

Các nguyên tắc chung của việc bố trí bảng mạch PCB nhiều lớp và lộ trình. Các nguyên tắc chung mà thiết kế PCB cần theo trong quá trình bao vây bảng mạch là như sau:

(1) Nguyên tắc thiết lập khoảng cách giữa những vết in của các thành phần. Khoảng cách giữa các mạng lưới khác nhau dựa trên nguyên tắc thiết lập khoảng cách giữa các vết in của các thành phần qua cách điện, quá trình sản xuất và các thành phần. Được quyết định bởi các yếu tố như kích thước. Ví dụ, nếu độ cao của một thành phần con chip là 8mil, thì hạt (Đảm bảo cấm vận) của con chip không thể đặt thành 10mil. Các nhà thiết kế PCB cần phải đặt một luật thiết kế 6km cho con chip riêng. Đồng thời, thiết lập khoảng cách cũng nên cân nhắc khả năng sản xuất của nhà sản xuất.

Hơn nữa, một yếu tố quan trọng ảnh hưởng đến các thành phần là cách điện. Nếu sự khác biệt tiềm năng giữa hai thành phần hay mạng rộng lớn, thì phải cân nhắc việc cách ly điện. Vòng an toàn của lỗ hổng trong môi trường chung là 200V/mm, chính là 5.08V/mili. Vì vậy, khi có cả điện tử lẫn điện hạ trên cùng một bảng mạch, cần phải chú ý đặc biệt tới mức độ an to àn vừa đủ. Khi có mạch điện cao và điện hạ, cần phải chú ý đặc biệt tới khoảng cách an to àn vừa đủ.

(2) Lựa chọn đường dây nối nhau ở góc đường dây. Để làm cho bảng mạch dễ dàng sản xuất và đẹp đẽ, cần thiết thiết phải đặt chế độ góc của mạch và sự chọn các hình cáp của góc của mạch khi thiết kế PCB. Có thể chọn 455444;176;, 9544456; và mic. Bình thường, không sử dụng các góc sắc bén, và tốt hơn là sử dụng cổng nam chuyển động hay 45\ 196; chuyển đổi, và tránh được 954444456; hay crop góc sắc hơn.

Sự kết nối giữa dây và miếng đệm cũng phải càng mịn càng tốt để tránh những đôi chân nhỏ, được giải quyết bằng cách phun trà. Khi khoảng cách giữa các miếng đệm thấp hơn đường kính ngoài D của một miếng đệm, độ rộng của sợi dây có thể ngang với đường kính của miếng đệm. nếu khoảng cách giữa các miếng đệm lớn hơn D, độ rộng của sợi dây không phải lớn hơn so với đường kính. Khi một sợi dây đi qua giữa hai cột mà không có kết nối với nó, nó nên giữ khoảng cách lớn nhất và ngang nhau với chúng. Cũng như, khi một sợi dây và một sợi dây nối giữa hai cái đệm mà không có kết nối với chúng, nó phải được giữ ở khoảng cách tối đa và ngang nhau, khoảng cách giữa chúng cũng phải đồng bộ và ngang nhau và giữ tối đa. Khoảng cách giữa họ cũng phải đồng bộ và bình đẳng và giữ cho đến tối đa.

(3) Cách xác định độ rộng của dấu vết in. Độ rộng của dấu vết được quyết định bởi các yếu tố như mức độ dòng chảy qua dây và chống nhiễu. Giá lớn hơn tốc độ cao chảy xuyên qua dòng chảy, thì dấu vết càng rộng. Dây điện nên rộng hơn đường dây tín hiệu. Để đảm bảo sự ổn định tiềm năng mặt đất (thì sự thay đổi của dòng mặt đất càng lớn, thì đường dẫn sẽ rộng hơn. Thông thường, đường điện sẽ rộng hơn đường dây tín hiệu, và đường điện sẽ có tác động thấp hơn chiều rộng của đường tín hiệu), đường bộ cũng phải còn dài hơn. Mặt đất rộng cũng phải rộng hơn. Các thử nghiệm đã chứng minh được rằng khi độ dày của ống in là 0.05mm, dây dẫn trên mặt đất hiện thời của sợi dây in cũng phải rộng hơn và có thể được tính theo giá trị 20A/mm2, nghĩa là, 0.05mm, sợi rộng mm có thể chảy qua 1A Current. Vì vậy, đối với dạng chung, độ rộng chung có thể đáp ứng yêu cầu; cho điện cao điện và điện cao, độ rộng của 10-30 cho đường dây tín hiệu có thể đáp ứng yêu cầu của đường cao điện và đường tín hiệu cao cấp với độ rộng dây lớn hơn hay bằng bốn triệu, đường ~Khoảng cách giữa các đường còn lớn hơn 30mill. Để đảm bảo sức mạnh chống tháo rời và độ đáng tin cậy hoạt động của sợi dây, cần sử dụng sợi dây rộng nhất có thể để giảm cản đường và tăng cường hiệu suất chống nhiễu trong phạm vi có thể xác định vùng và mật độ.

Với độ rộng của đường dây điện và đường đất, để đảm bảo sự ổn định của đường sóng, nếu khoảng cách dây của bảng mạch cho phép, hãy cố làm dày nó càng nhiều càng tốt. Thông thường, nó cần ít nhất 50triệu.

(4) Anti-interference and electromagnetic shielding of PCB printed wires. Sự can thiệp của đường dây chủ yếu bao gồm sự can thiệp giữa các dây điện, the interference introduced by the power line) the anti-interference and electromagnetic shielding of the printed wires. Sự can thiệp của đường dây chủ yếu bao gồm sự can thiệp giữa các dây điện, Giọng nói chéo giữa các đường tín hiệu PCB, và trò chuyện chéo giữa các đường tín hiệu. Sự sắp đặt hợp lý và bố trí của đường dây dẫn và các phương pháp lắp ráp có thể làm giảm các nguồn nhiễu Thiết kế PCB Hệ thống in có khả năng nhận dạng điện từ tốt hơn..