Como su nombre indica, el chip invertido es un método de encapsulamiento que conecta la parte delantera del chip (un lado del circuito IC de fabricación) hacia abajo al sustrato. Los terminales de señal eléctrica están hechos de soldadura tradicional y pueden interconectarse con el sustrato. En este tipo de interconexión, los terminales de entrada y salida (i / o) pueden cubrir todo el chip, por lo que incluso a la misma distancia, la densidad de interconexión del chip invertido es mucho mayor que la densidad de Unión del cable. En la interconexión de Unión de cables, el E / s solo se puede colocar alrededor del chip. Por lo tanto, no importa cuán pequeña sea la distancia, no se puede lograr la densidad de E / s de la interconexión de chips invertidos. Entonces, la tecnología de protuberancias es la clave de toda la tecnología de interconexión de chips invertidos.

La clave para la fabricación de protuberancias de obleas se describe en la tecnología de protuberancias de obleas es depositar la capa metálica debajo de las protuberancias (ubm). Cabe señalar que el término utilizado anteriormente por IBM era la capa de metalización de restricción esférica (blm), que funcionaba como: proporcionar una capa de Unión para la interconexión; Proporcionar una capa de barrera de difusión atómica para evitar que los átomos del material convexo se propaguen a la estructura metálica inferior; El material dieléctrico inferior y el metal proporcionan una capa adhesiva y actúan como barrera para evitar que los contaminantes se muevan al metal inferior a lo largo de la dirección horizontal de la capa dieléctrica. la mayoría de los UBM utilizados actualmente están hechos a través de procesos de pulverización. El proceso de pulverización es el proceso más rentable para fabricar ubm. Especialmente en comparación con el proceso de evaporación. El factor más directo que afecta la fiabilidad estructural de las protuberancias de soldadura es la calidad de producción de ubm. En general, la estructura de la UBM debe ser capaz de soportar múltiples retornos (generalmente hasta 20 veces) sin daños. Debido a que el UBM es una estructura utilizada para combinar protuberancias de soldadura con capas de metalización de almohadillas, también debe pasar las pruebas de esfuerzo de corte y esfuerzo de tracción. En la prueba de daño mecánico, el criterio general para la falla de los protuberancias de soldadura es que la falla ocurre en la propia soldadura. Por lo tanto, el UBM debe tener suficiente intensidad. No se producirá una disminución del rendimiento debido a factores como el tiempo, la temperatura, la humedad y el voltaje de sesgo.

Tendencia del mercado de chips invertidos el encapsulamiento de chips invertidos se ha convertido en la tecnología principal de interconexión de encapsulamiento. Hasta ahora, los chips invertidos se consideraban en realidad un encapsulamiento, no una tecnología de interconexión. Por ejemplo, el encapsulamiento de matriz de rejilla de bola de chip invertido (fcbga) utiliza principalmente tecnología de sustrato estratificado para completar el proceso de ensamblaje y encapsulamiento, pero se limita a aplicaciones de circuitos integrados de alto rendimiento. la siguiente imagen muestra el campo de aplicación del chip invertido:

(1) distancia entre puntos destacados: reducir la distancia entre puntos destacados puede aumentar la densidad de E / s; Tendencia a la variación del asfalto (transición gradual de 250 micras a 125 micras);

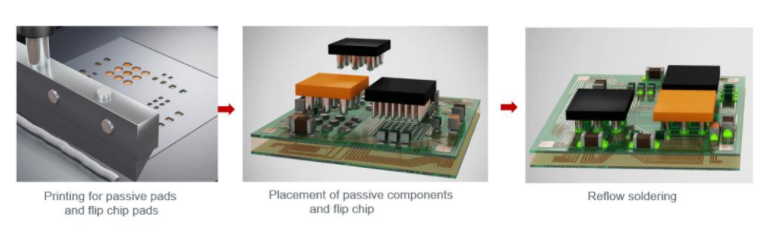

(2) método de depresión del punto de soldadura: impresión y galvanoplastia de malla de alambre evaporada;

(3) composición de la soldadura de punto sobresaliente: alto contenido de plomo y bajo contenido de eutéctica sin plomo (sn - ag) - distancia entre columnas de cobre inferior a 125 micras;

¿(4) composición del embalaje: ¿ sustrato cerámico, sustrato laminado de interconexión de alta densidad, sustrato laminado preimpregnado, sustrato laminado de bajo coeficiente de expansión térmica? Sustrato sin núcleo.

(5) estructura de embalaje: tapa única sellada (spl) - Refuerzo de tapa única no sellada + moldeo de chip desnudo cubierta

Los mercados de aplicación de fccsp tradicionales son los siguientes:

Mercado de aplicaciones fccsp:

(1) densidad de protuberancias (i / o) en relación con el tamaño del chip: para un tamaño de chip superior a 200 I / o o superior a 5,5 mm; Los productos de baja densidad utilizan wlcsp para obtener mejores y menores costos.

(2) baja potencia: potencia general inferior a 2w, dependiendo de = "," on = "" chip = "" nivel de tablero = "" encapsulamiento = "" can = "" be = "" used = "for =" Power = "" Bare = "fcccsp =" > 2w ".

(3) área: para dispositivos portátiles, la tecnología de 40 NM / 65 nm reduce el tamaño del chip, pero más I / o hace que el I / o periférico no tenga suficiente área para organizar, por lo que es necesario usar cables de sustrato para abanicar la Zona.

(4) precio: para los chips de pequeño tamaño de E / S alto, la falta de área periférica, el costo de la línea au y los sustratos de gran tamaño para el abanico de alambre impulsarán el desarrollo de fccsp competitivo en precio.

(5) moldeo, fácil de probar y agarrar, la forma común es la misma que la cabga.

Resumen

El chip invertido siempre ha sido una tecnología de encapsulamiento emocionante. Sin embargo, en comparación con el embalaje tradicional de Unión de alambre, su costo limita que los chips invertidos se conviertan en la tecnología principal. Sin embargo, las restricciones de costos se están eliminando gradualmente y el uso de chips invertidos encapsulados en tiras ha reducido significativamente sus costos. Debido a que los sustratos laminados ocupan la mayor parte del costo del producto, reducir el costo de los sustratos laminados es la forma más eficaz de reducir el costo de encapsulamiento de chips invertidos.

Además, para el diseño de fpfc, amkor ha llevado a cabo una gran cantidad de Investigaciones para transformar el diseño existente de chips invertidos de matriz de área en un diseño de espaciamiento fino. El 80% de los estudios encontró que el diseño periférico de espaciamiento fino puede reducir el costo del sustrato debido a la reducción de la capa metálica y la reducción del tamaño externo. Al reducir el costo del sustrato de encapsulamiento de chips invertidos (su costo es el más alto), el encapsulamiento de chips invertidos se puede utilizar ampliamente en otros mercados.